在FPGA滤波器设计中,合理的流程规划能显著提高设计效率和可靠性。以下是针对数字滤波器设计的结构化开发流程建议:

一、设计前期准备阶段

1. 需求规格化(关键第一步)

-

明确滤波参数:

- 采样率:100KS/s

- 截止频率:20KHz(低通)

- 阻带衰减:>40dB

- 实时性要求:处理延迟 < 5个采样周期

-

确定硬件约束:

// 示例约束模板

parameter CLK_FREQ = 100_000_000; // 100MHz主频

parameter DATA_WIDTH = 16; // 16位数据精度

2. 算法仿真验证

-

MATLAB/Python建模示例:

中值滤波仿真

import numpy as np

def median_filter(data, window=3):

return np.convolve(data, np.ones(window)/window, mode='same')raw_data = np.random.randn(1000) # 含噪数据

filtered = median_filter(raw_data)

二、架构设计阶段

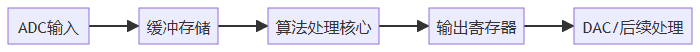

1. 数据流分析(核心步骤)

- 典型滤波器数据路径:

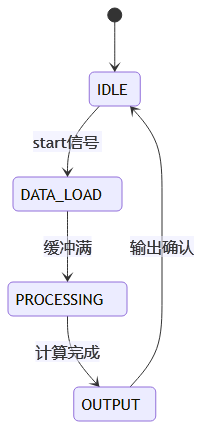

2. 控制逻辑规划

-

状态机设计建议:

typedef enum logic [1:0] {

IDLE,

DATA_LOAD,

PROCESSING,

OUTPUT

} state_t;

三、详细设计阶段

1. 时序图绘制(关键通信协议)

-

典型接口时序示例:

CLK |¯¯||¯¯||¯¯||¯¯

VALID ____|¯¯¯¯¯¯¯¯|

DATA XXXX D0 X D1 X D2 X D3 X -

设计要点:

-

- 建立/保持时间余量计算

- 跨时钟域处理标记(如有异步接口)

2. 状态转移图设计

- 状态转移示例:

四、代码实现阶段

1. 模块化编码实践

-

推荐结构:

module digital_filter (

input logic clk,

input logic [15:0] adc_data,

output logic [15:0] dac_data

);// 数据通路 datapath u_datapath (.*); // 控制逻辑 control_fsm u_control (.*);endmodule

2. 关键代码段示例

-

滑动窗口实现:

always_ff @(posedge clk) begin

if (window_shift_en) begin

data_window[0] <= adc_data;

for(int i=1; i<WINDOW_SIZE; i++)

data_window[i] <= data_window[i-1];

end

end

五、验证与调试阶段

1. 联合仿真策略

-

Testbench结构:

module tb_filter;

// 生成激励

logic clk = 0;

always #5 clk = ~clk;// 实例化DUT digital_filter dut (.*); // 自动验证 initial begin apply_test_patterns(); verify_output(); $finish; endendmodule

2. 硬件调试技巧

-

嵌入式逻辑分析仪(ILA)配置:

Xilinx Vivado ILA配置

create_debug_core u_ila ila

set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila]

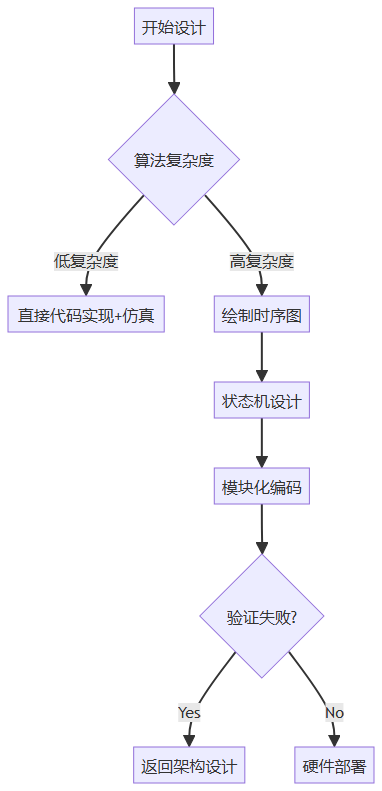

六、设计流程决策树

七、各阶段时间分配建议

|------|------|-------------|

| 阶段 | 时间占比 | 关键产出物 |

| 需求分析 | 20% | 规格文档 |

| 架构设计 | 30% | 数据流图/状态机图 |

| 代码实现 | 25% | 可综合RTL代码 |

| 验证调试 | 25% | 测试报告/时序收敛报告 |

八、经验总结

- 复杂滤波器设计(如自适应滤波器):

-

- 必须优先绘制状态转移图

- 需要详细时钟域分析

- 建议采用SystemVerilog Assertion验证

- 简单滤波器实现(如移动平均滤波器):

-

- 可跳过状态机设计

- 直接用时序图指导编码

- 重点确保时序收敛

-

混合信号处理:

// 数模混合设计示例

analog begin

V(in) <+ transition(data_in, 0, 10n);

end

digital begin

always @(posedge clk) begin

adc_val <= $rdm(V(in));

end

end

建议根据设计复杂度动态调整流程,对于首次设计建议采用完整流程,后续可根据经验简化非必要步骤。