FPGA同步复位、异步复位、异步复位同步释放仿真

xilinx VIVADO仿真

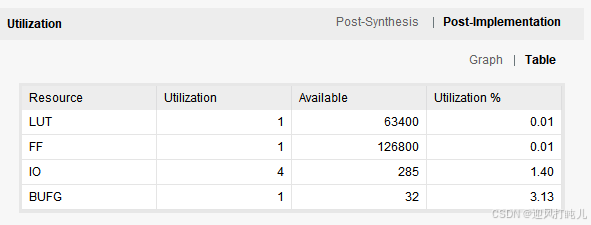

行为仿真

综合后功能仿真,综合后时序仿真

实现后功能仿真,实现后时序仿真

目录

前言

本文将详细介绍FPGA同步复位、异步复位、异步复位同步释放,并用实际的例子在VIVADO上面完成这三种复位的仿真,仿真包括行为仿真、综合后功能仿真、综合后时序仿真、实现后功能仿真、实现后时序仿真五种仿真。同时也将给出RTL、综合、实现后的电路图。仿真和电路图可以帮助我们彻底搞清楚这三种复位。

++提示:以下是本篇文章正文内容,下面案例可供参考++

一、同步复位

同步复位指的是在时钟边沿(有效沿)检测到复位信号后,执行复位操作。

设计源文件和仿真源文件如下:

//*******************同步复位*******************

module reset_research(

input clk , //时钟

input rst_n, //复位,低电平有效

input in , //输入信号

output reg out //输出信号

);

always@(posedge clk)begin

if(!rst_n)

out <= 1'b0; //复位将输出置零

else

out <= in; //其他时候将输入赋值给输出

end

endmodule

module tb_reset_research;

parameter PERIOD = 20;

reg clk = 0 ;

reg rst_n= 1 ;

reg in = 1 ;

wire out ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

reset_research u_reset_research

(

.clk ( clk ),

.rst_n ( rst_n ),

.in ( in ),

.out ( out )

);

initial

begin

#25 rst_n<=0;

#10 rst_n<=1;

#35 rst_n<=0;

#10 rst_n<=1;

#20 rst_n<=0;

#10 rst_n<=1;

#45 rst_n<=0;

#5 rst_n<=1;

#100

$finish;

end

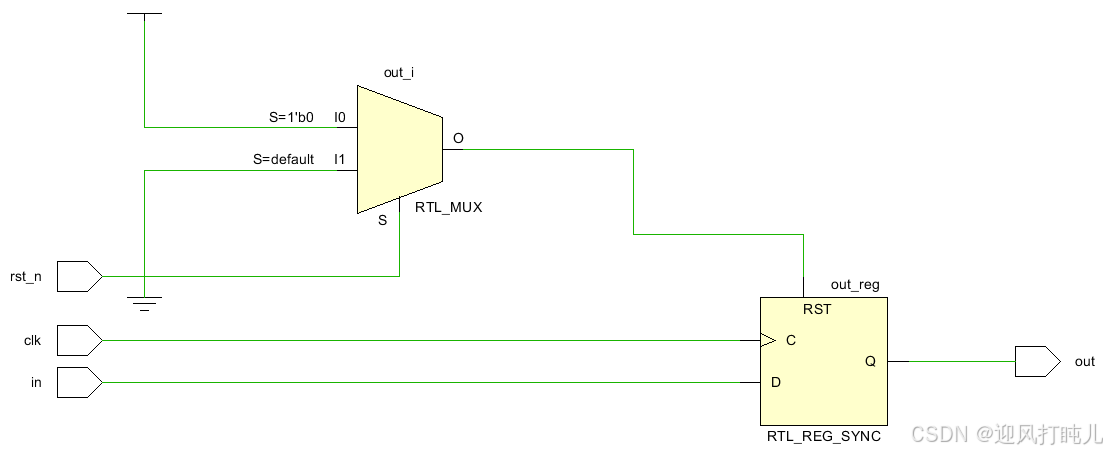

endmoduleRTL级电路如下:

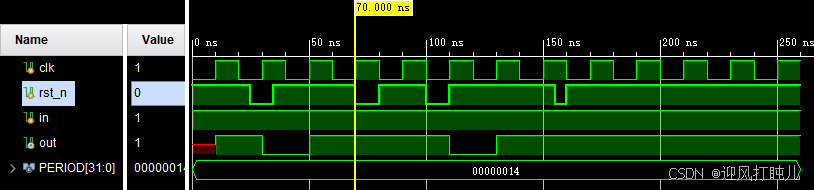

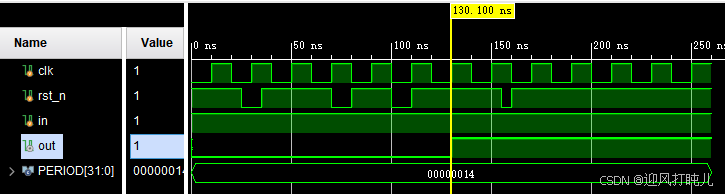

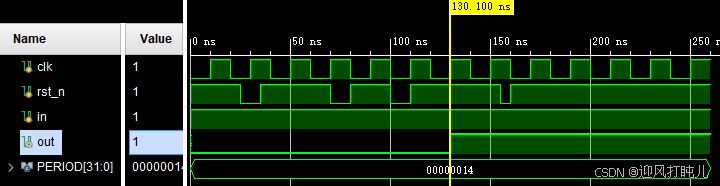

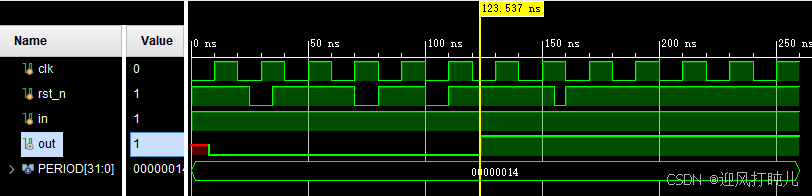

行为仿真结果如下:

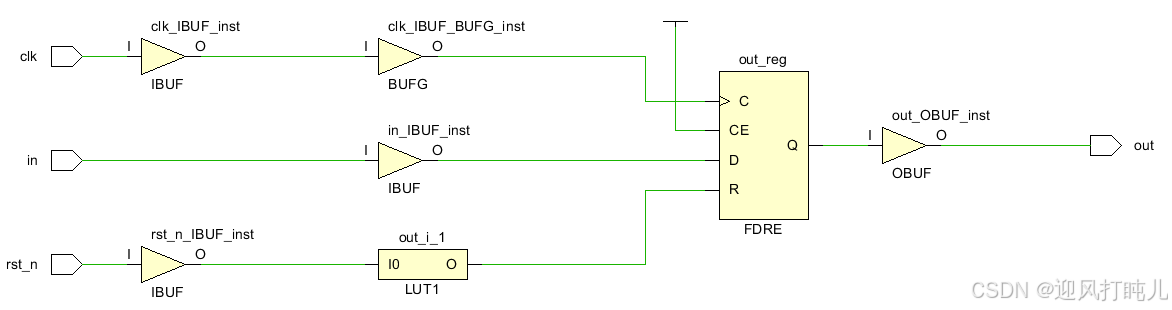

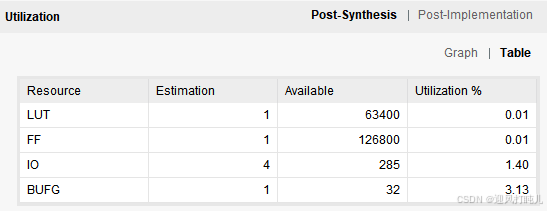

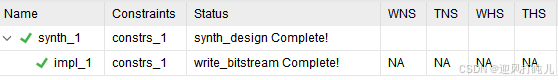

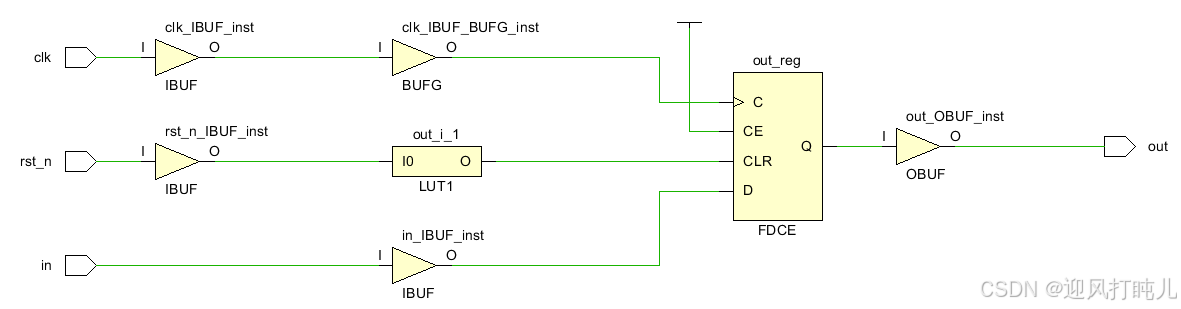

综合后的电路图如下:

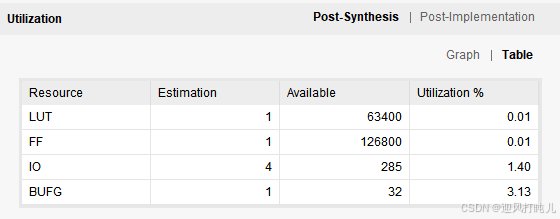

综合后功能仿真

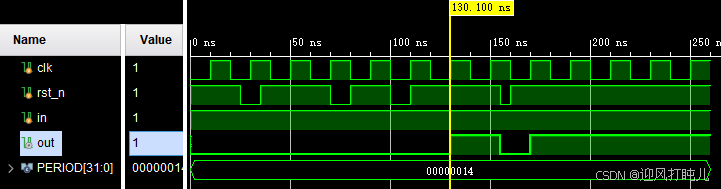

综合后时序仿真

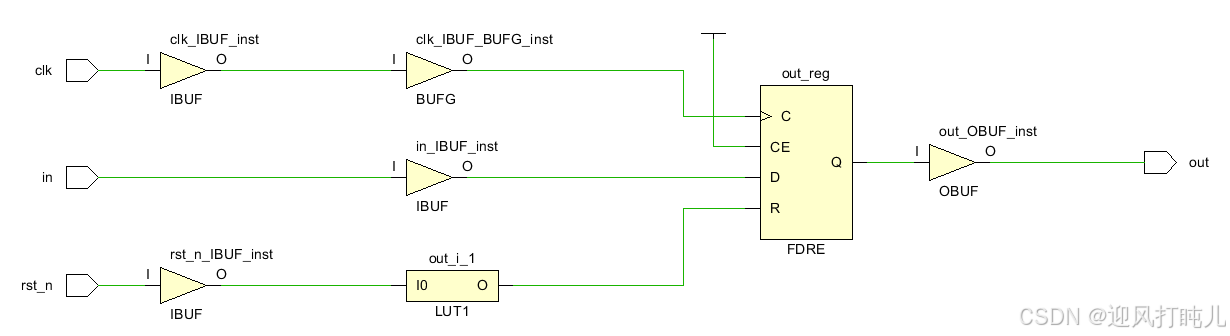

实现后的电路图如下:

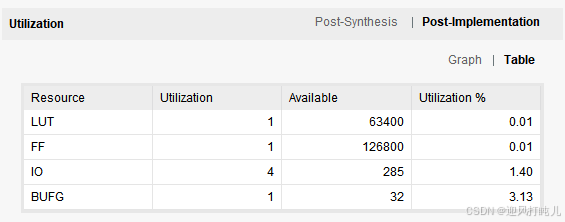

实现后功能仿真

实现后时序仿真

由于输入的复位信号没有同步到当前时钟域下,VIVADO实现无法做时序分析。

二、异步复位

异步复位指的是无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

设计源文件如下,仿真源文件和同步复位一样。

//*******************异步复位*******************

module reset_research(

input clk , //时钟

input rst_n, //复位,低电平有效

input in , //输入信号

output reg out //输出信号

);

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

out <= 1'b0; //复位将输出置零

else

out <= in; //其他时候将输入赋值给输出

end

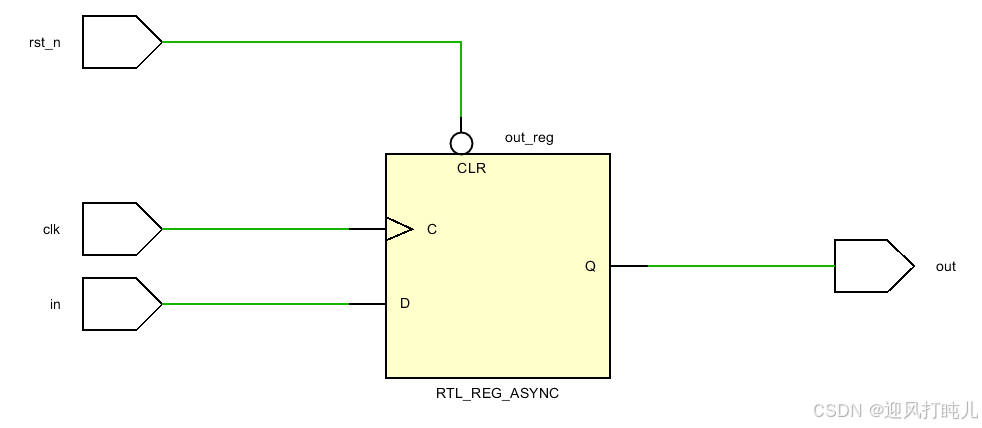

endmoduleRTL级电路如下:

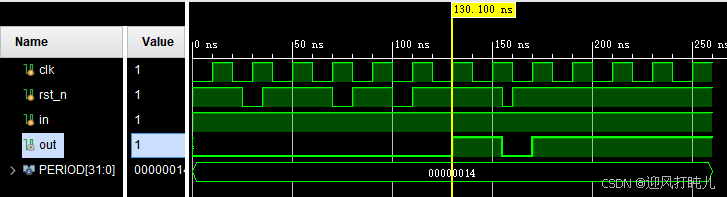

行为仿真结果如下:

综合后的电路图如下:

综合后功能仿真

综合后时序仿真

实现后的电路图如下:

实现后功能仿真

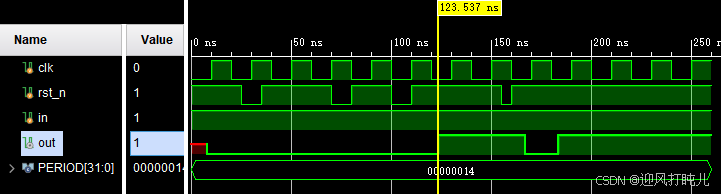

实现后时序仿真

由于输入的复位信号没有同步到当前时钟域下,VIVADO实现无法做时序分析。

三、异步复位同步释放

异步复位同步的根本思想,是将异步信号同步化。

设计源文件如下,仿真源文件和前两种复位的一样。

//异步复位同步释放(如果复位信号从IO进来,这样可以消除异步复位的亚稳态问题)

module reset_research(

input clk , //时钟

input rst_n, //复位,低电平有效

input in , //输入信号

output reg out //输出信号

);

reg new_rst_n_d0;

reg new_rst_n;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

new_rst_n_d0<=0;

new_rst_n<=0;

end

else

begin

new_rst_n_d0<=1;

new_rst_n<=new_rst_n_d0;

end

end

//使用同步后的复位信号进行异步复位

always@(posedge clk or negedge new_rst_n)begin

if(!new_rst_n)

out <= 1'b0; //复位将输出置零

else

out <= in; //其他时候将输入赋值给输出

end

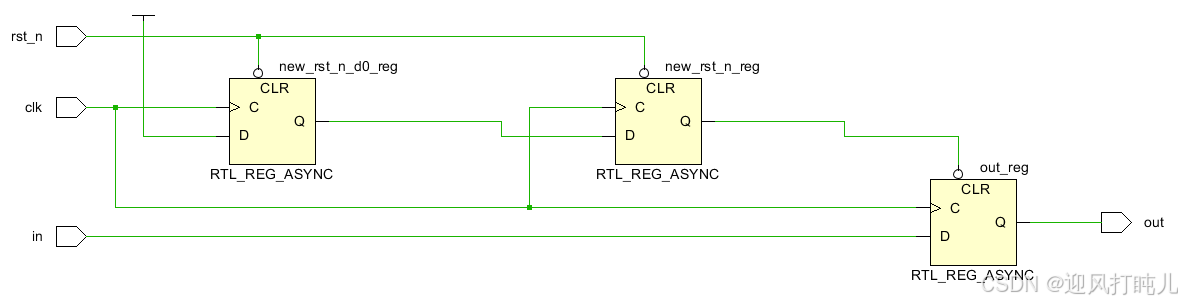

endmoduleRTL级电路如下:

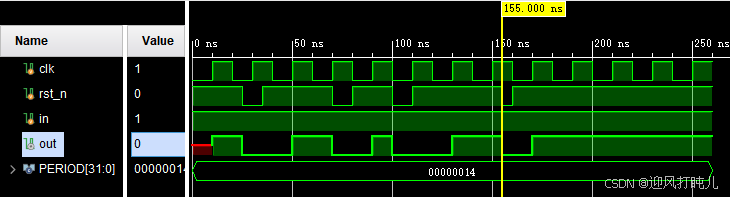

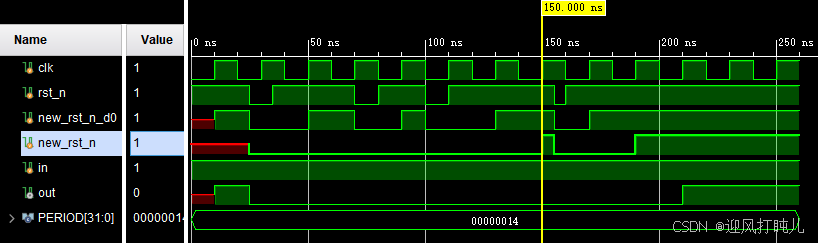

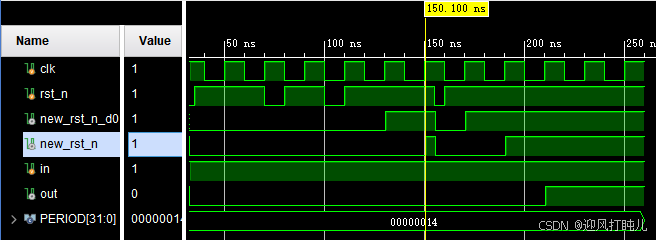

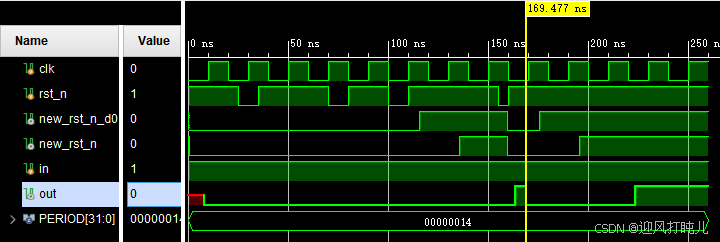

行为仿真结果如下:

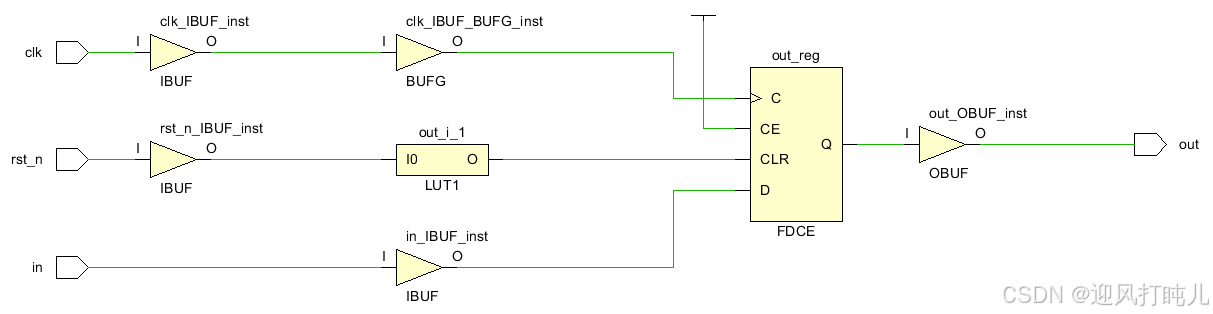

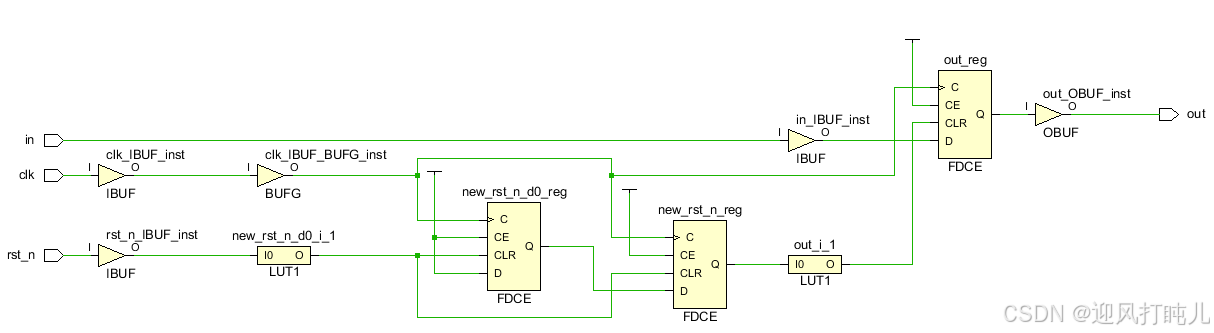

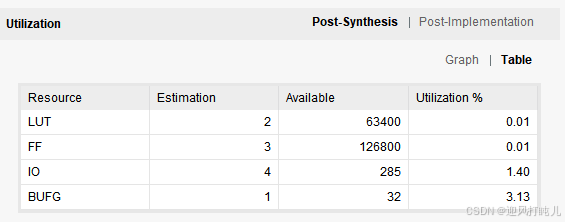

综合后的电路图如下:

综合后功能仿真

综合后时序仿真

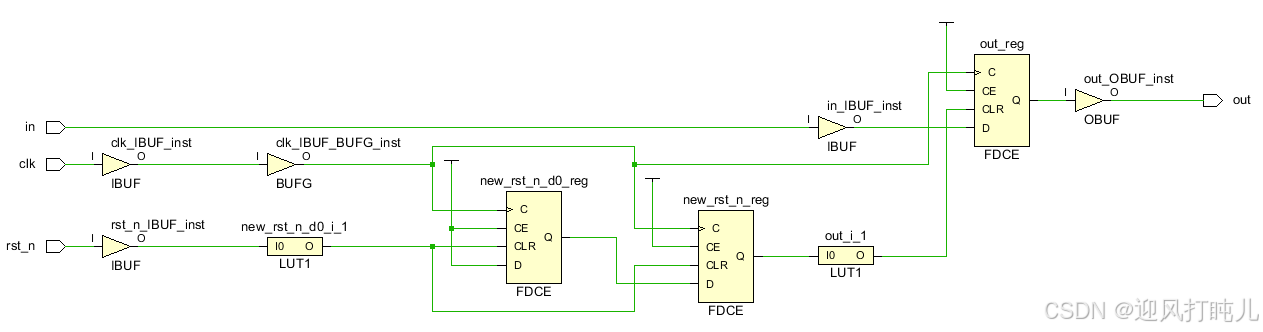

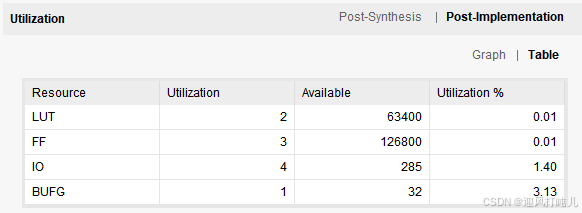

实现后的电路图如下:

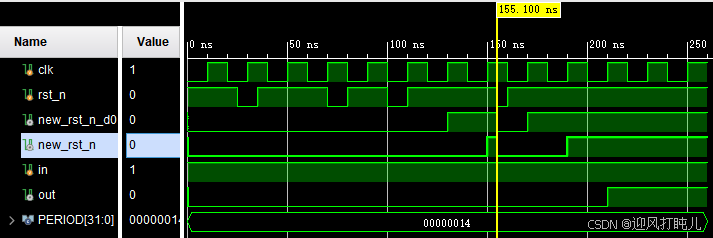

实现后功能仿真

实现后时序仿真

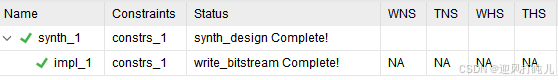

由于输入的复位信号同步到了当前时钟域下,VIVADO实现可以做时序分析。

总结

从以上结果,我们可以得出以下结论:

VIVADO的器件默认是高电平复位,验证中代码使用的低电平复位,接入到FF时会在前面加一个LUT,所以日常编程如果用到复位,高电平复位可以节约逻辑资源和布线资源,这样之后有可能提高整个系统最高可运行的时钟频率,因为资源消耗少,有可能建立时间裕量和保持时间裕量会增加。

异步复位同步释放便于软件进行时序分析,能通过软件分析结果得出时序是否收敛,其他两种复位软件无法进行时序分析,无法得知设计的电路时序是否收敛。

每一种复位中,综合实现后的功能仿真对得上,综合实现后的时序仿真也对得上,只是延时不同,但是由于时序仿真考虑了延时,所以时序仿真的结果与功能仿真的结果可能会出现偏差,如本文便出现了这种情况,当然也可能是仿真激励条件过于刁钻了。实际应用中的时序电路要确保所有信号同步于时钟边沿,对于异步信号,需要同步化,这样能提高电路的可靠性。

综上,复位会消耗资源,所以能不用复位就不用复位,如果要用复位,外部的复位信号使用的方式应该是异步复位同步释放。