《FPGA经典例程及解读--基于xilinx K325T平台》系列导航

本专栏主要针对与想学习FPGA的同学,从基础的点灯到之后的复杂功能实战例程,从入门到进阶,通过这些例程的学习和了解,希望可以帮助你从一个FPGA小白进阶到FPGA中级阶段,能够处理工作中大多数的FPGA使用场景。

本篇是该系列的第三篇内容

上一篇:FPGA例程(2):LED流水灯--vivado FPGA程序固化下载-CSDN博客

**下一篇:**关注我,第一时间获取更新!!

设计程序参考: FPGA例程(3):按键检测实验资源-CSDN下载

1 引言

通过该实验,检测开发板的按键功能是否正常。知晓硬件描述语言与FPGA硬件之间的联系。

2 硬件环境

开发环境使用vivado2019.1

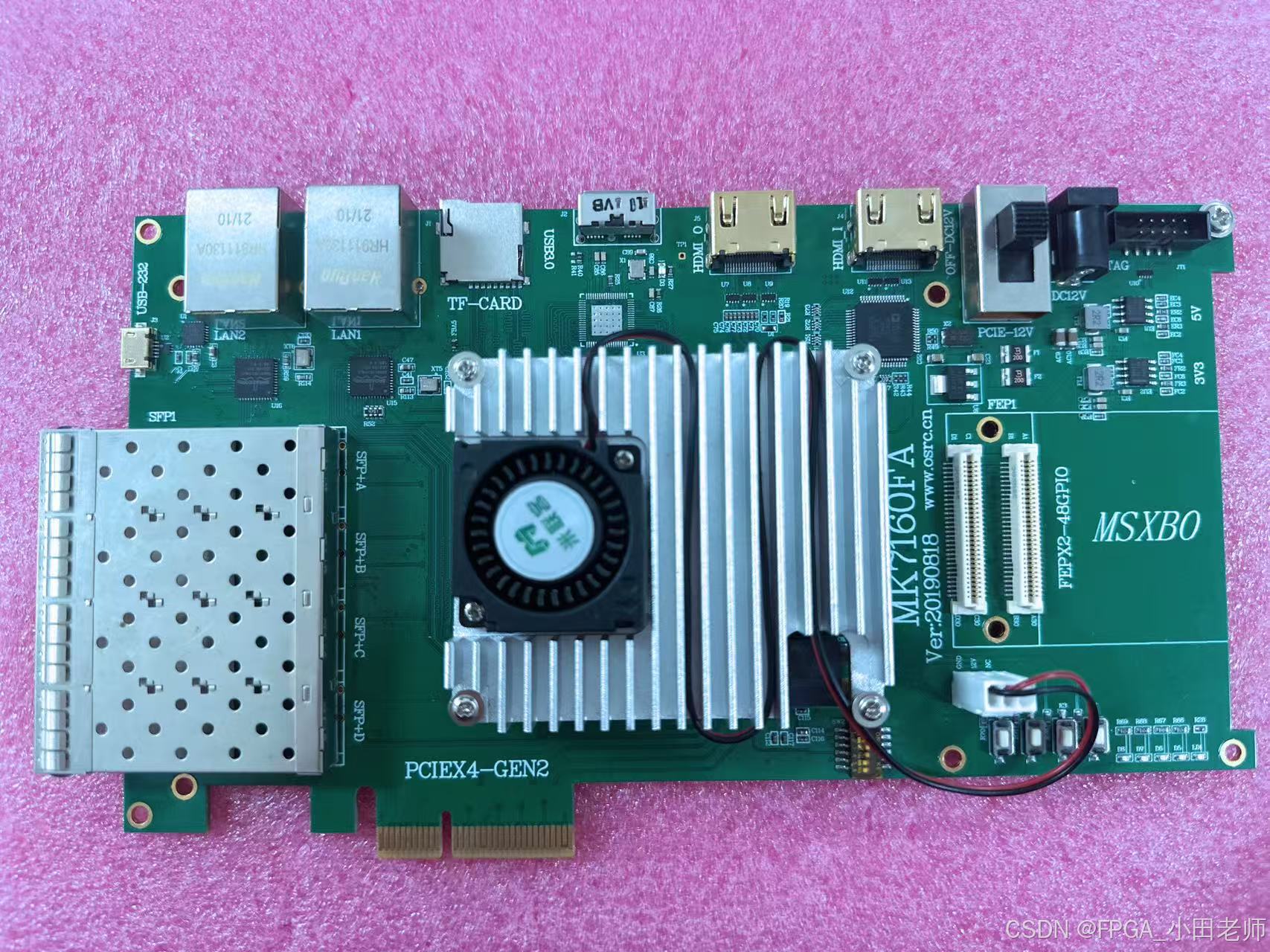

开发板使用米联客的MK7160FA

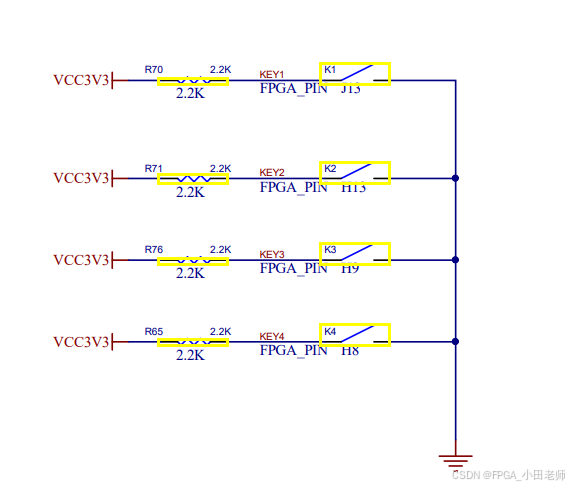

对应的原理图如下

从图中可以看到,按键松开KEY为高电平,按键按下KEY为低电平。

3 程序设计

这个程序设计并没有很复杂,我们在LED灯实验的基础上,进行设计FPGA例程(1):LED流水灯实验--vivado工程创建、编译及下载bit-CSDN博客

3.1 接口说明

对外接口

两个输入按钮key1_i和key2_i

两个输出led灯LED1_o和LED2_o

LED1_o是一个闪烁的led灯,500ms闪烁一次,

当key1按键按下,key1_i会变为0,LED1停止闪烁

当key1按键断开,key1_i会变为1,LED1闪烁

LED2_o是与按键KEY2状态相关的灯

当key2按键按下,key2_i变为0,led2变为1,LED2亮

当key2按键断开,key2_i变为1,led2变为0,LED2灭

3.2 整体程序

整体程序设计如下:

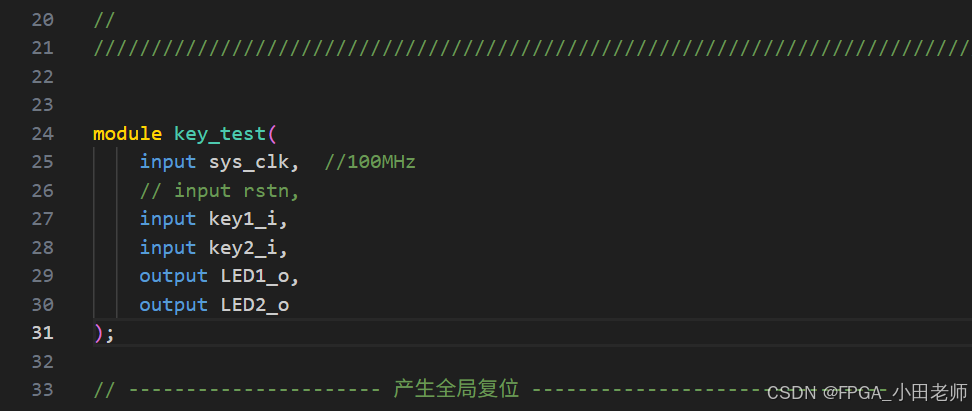

module key_test(

input sys_clk, //100MHz

// input rstn,

input key1_i,

input key2_i,

output LED1_o,

output LED2_o

);

// ---------------------- 产生全局复位 -------------------------------

parameter RST_DELAY = 8'd128;

reg [7:0] rst_cnt;

always @(posedge sys_clk) begin

if(rst_cnt < RST_DELAY)begin

rst_cnt <= rst_cnt + 1'd1;

end else if(rst_cnt == RST_DELAY) begin

rst_cnt <= rst_cnt;

end else begin

rst_cnt <=0;

end

end

reg rst_n;

always @(posedge sys_clk) begin

if(rst_cnt == RST_DELAY) begin

rst_n <= 1;

end else begin

rst_n <= 0;

end

end

// -----------------------------------------------------------------

reg [31:0] led_cnt;

always @ (posedge sys_clk or negedge rst_n) begin

if (!rst_n) begin

led_cnt <= 32'd0;

end

else begin

if (led_cnt == 32'd50_000_000 - 1) begin // 对应500ms

led_cnt <= 32'd0;

end

else begin

led_cnt <= led_cnt + 32'd1;

end

end

end

reg led_c;

always @ (posedge sys_clk or negedge rst_n) begin

if (!rst_n) begin

led_c <= 1'b0;

end

else begin

if (led_cnt == 32'd50_000_000 - 1) begin

led_c <= ~led_c;

end

else begin

led_c <= led_c;

end

end

end

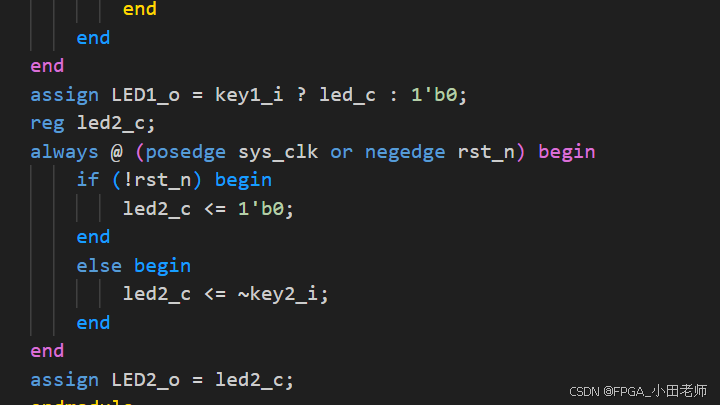

assign LED1_o = key1_i ? led_c : 1'b0;

reg led2_c;

always @ (posedge sys_clk or negedge rst_n) begin

if (!rst_n) begin

led2_c <= 1'b0;

end

else begin

led2_c <= ~key2_i;

end

end

assign LED2_o = led2_c;

endmodule4 工程分析

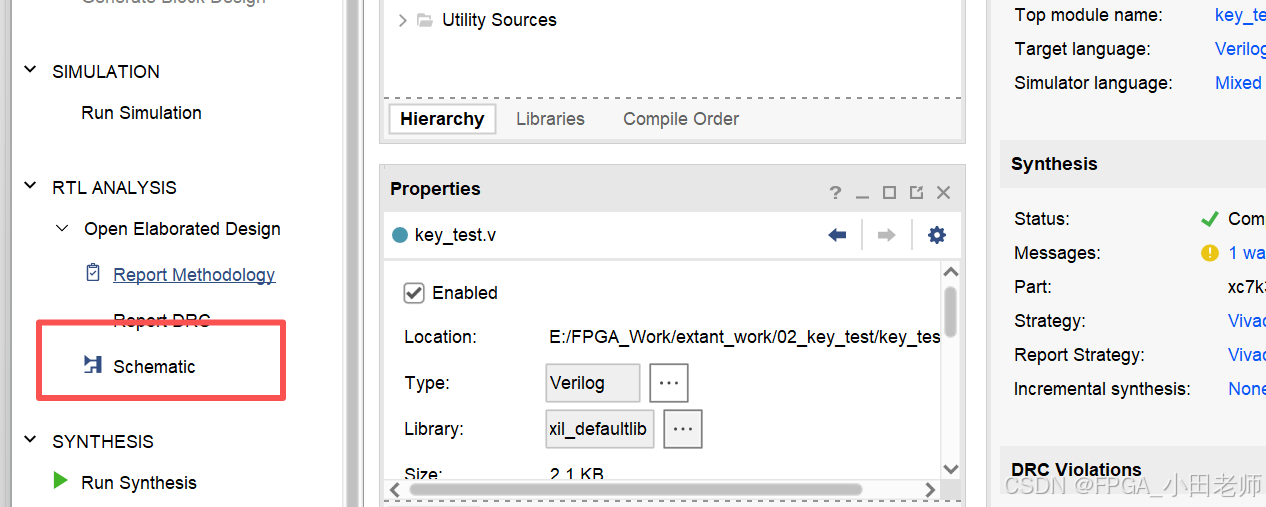

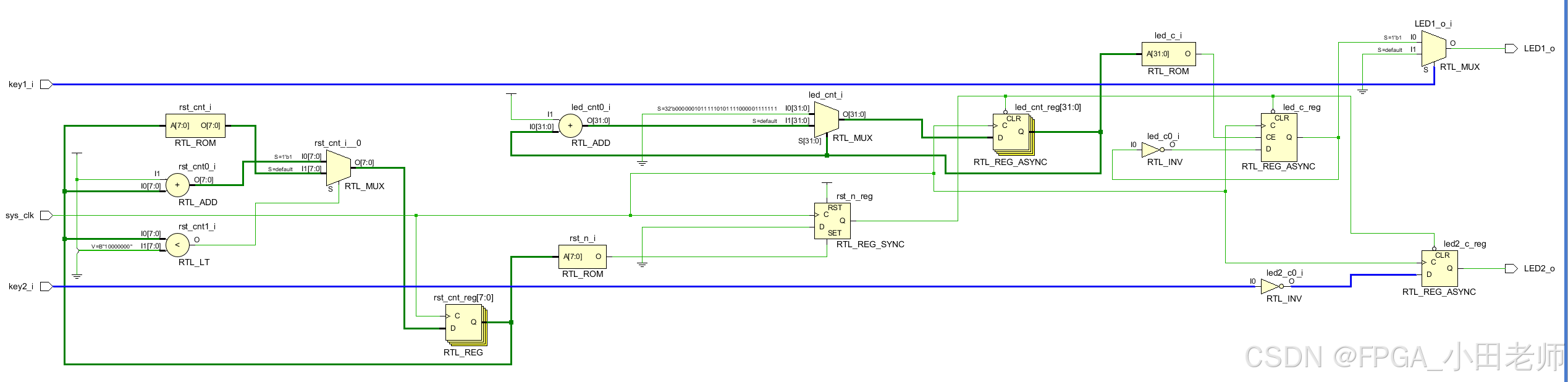

打开RTL ANALYSIS--->Schematic,可以看到我们的Verilog语言与FPGA硬件之间的联系。

LED1:

通过 选择器 选择输出led_c还是0,选择器的S参数就是key1的值;

当S是1的时候,输出led_c,当S是0的时候输出0;

LED2:

key2取反之后输入D触发器,输入D触发器的信号会在D触发器时钟上升沿锁存然后再送到输出。

5 实验结果

我们按照FPGA例程(1):LED流水灯实验--vivado工程创建、编译及下载bit-CSDN博客的方式编译完成生成bit,并将bit文件下载进板子,我们可以看到现象如下。

- 当key1断开的时候led1闪烁

- 当按下key1的时候led1熄灭

- 当key2断开的时候led2熄灭

- 当按下key2的时候led2变亮

key按键测试