目录

-

- 一、状态机

-

- [1. 状态机基本概念](#1. 状态机基本概念)

- [2. 状态机类型](#2. 状态机类型)

- [3. Verilog 状态机设计要点](#3. Verilog 状态机设计要点)

- 二、状态机实现一个1s流水灯

- 三、DE2-115实物演示

一、状态机

1. 状态机基本概念

状态机(Finite State Machine, FSM)是数字电路设计中用于描述系统状态转换的核心组件,由以下要素组成:

状态寄存器 :存储当前状态

下一状态逻辑 :根据输入和当前状态确定下一状态

输出逻辑:生成与当前状态相关的输出

2. 状态机类型

| 类型 | 特点 |

|---|---|

| Moore | 输出仅取决于当前状态 |

| Mealy | 输出取决于当前状态和输入 |

| 混合型 | 结合 Moore 和 Mealy 的特点 |

3. Verilog 状态机设计要点

推荐使用三段式状态机结构:

- 状态寄存器(时序逻辑)

- 下一状态逻辑(组合逻辑)

- 输出逻辑(组合逻辑或时序逻辑)

优点:结构清晰、避免组合逻辑环路、便于综合和调试。

二、状态机实现一个1s流水灯

代码:

主模块:

c

module flowLed (

input wire clk, // 系统时钟

input wire rst_n, // 复位信号

output reg [7:0] led // 8位LED输出

);

// 时钟分频信号连线

wire clk_1s_en;

// 实例化时钟分频模块

clk_divider u_clk_divider (

.clk(clk),

.rst_n(rst_n),

.clk_1s_en(clk_1s_en)

);

// ========== 三段式状态机设计 ========== //

// 第一阶段:状态寄存器定义

reg [7:0] state;

// 第二阶段:状态转移逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= 8'b0000_0001; // 复位时第一个LED亮

end else if (clk_1s_en) begin // 每秒更新一次状态

state <= {state[6:0], state[7]}; // 循环左移

end

end

// 第三阶段:输出逻辑(直接驱动LED)

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

led <= 8'b0000_0001; // 初始状态

end else begin

led <= state; // 状态直接映射到LED输出

end

end

endmodule分频模块:

c

module clk_divider (

input wire clk, // 系统时钟(如50MHz)

input wire rst_n, // 复位信号(低有效)

output reg clk_1s_en // 1秒使能信号(高脉冲)

);

// 50MHz -> 1Hz,需要计数50,000,000次(根据实际时钟调整)

parameter MAX_COUNT = 50_000_000 - 1;

reg [25:0] counter; // 足够覆盖50MHz分频的位宽

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

counter <= 0;

clk_1s_en <= 0;

end else begin

if (counter == MAX_COUNT) begin

clk_1s_en <= 1; // 产生1Hz使能脉冲

counter <= 0;

end else begin

counter <= counter + 1;

clk_1s_en <= 0; // 保持单周期高脉冲

end

end

end

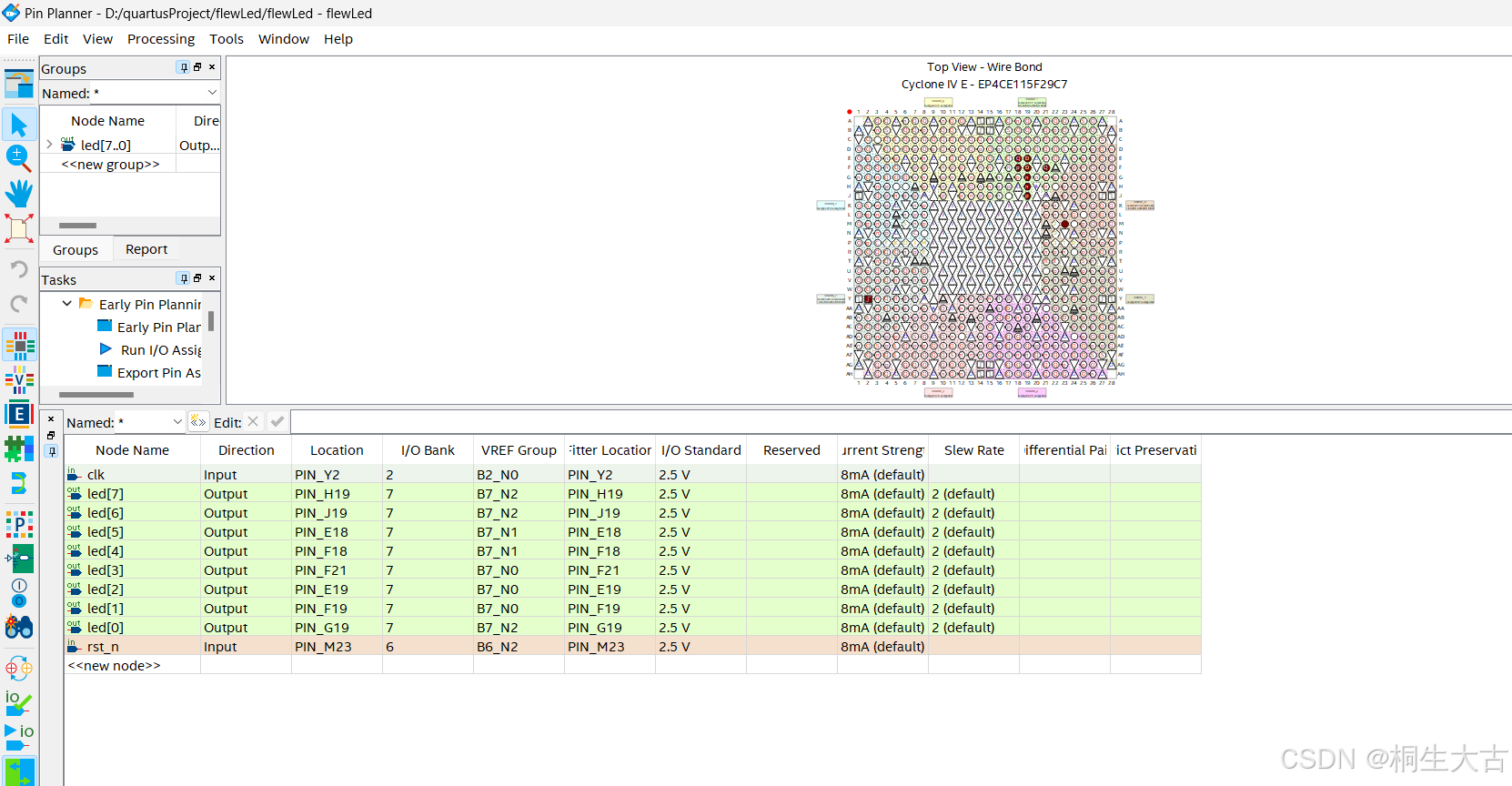

endmodule三、DE2-115实物演示

引脚配置:

实物效果:

流水灯