我们在做ZYNQ系统开发时候做的IP基本都是AXI_LITE_SLAVE,是SLAVE,从设备。就是提供了若干寄存器接口供MASTER进行读写。SLAVE里面的逻辑通过读写动作或者读写的数据进行响应的动作。这种方式的好处是硬件层面可以访问寄存器,软件层面是可以实现用指针访问,实现了硬件和软件的统一。

比如ZEDBOARD+FMCS3的官方DEMO,ADI官方提供了基于这套硬件组合的VIVADO项目以及PS的驱动项目。其中HDL部分对应PL部分实现系带数据的收发,而PS部分运行C语言实现一些计算并通过SPI读写AD9361。这种方式对于具备ZYNQ架构的硬件再合适不过了。但是在很多情况下,我们可能只使用纯的FPGA,还想使用上这套如此完美的架构,那我们就开始琢磨了。

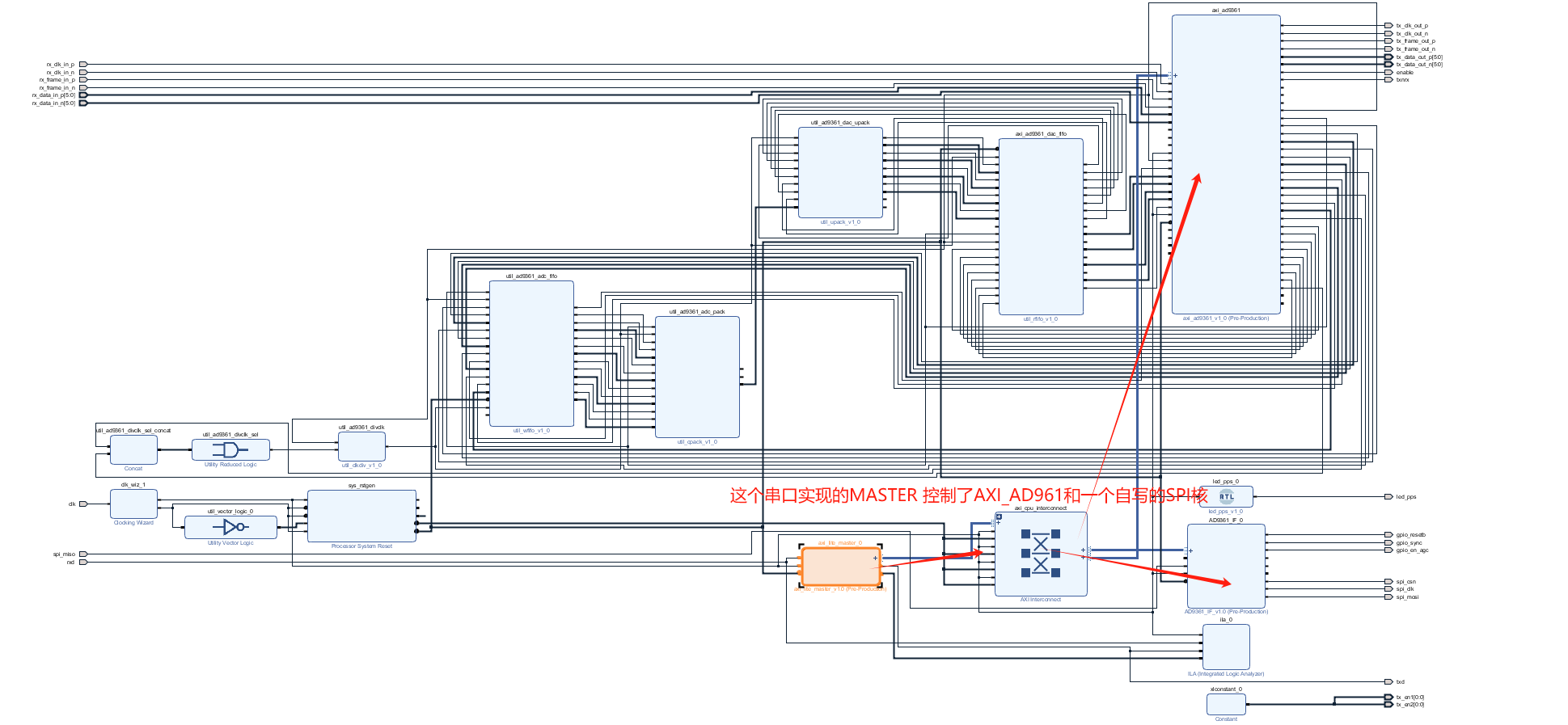

首先我们考虑PS部分运行的那堆C代码,是可移植的,我们可以移植到PC机里面跑,最终那堆C跟AD9361进行控制交互的是SPI口以及AD9361的那几个AXI的IP核。如果有一个AXI MASTER 直接能控制这些SLAVE,并且能被PC控制。简单说就是PC通过某个手段方式控制一个AXI MASTER,就可以实现对ADI官方提供的AXi_9361等核进行配置。我们首先想到了UART。这样就可以做一些基于UART的握手协议,在PC机电脑层面控制一个SLAVE MASTER。这样下来这个UART串口因为速度比较慢会导致配置时间延长很大,但是这不重要了,因为AD9361使用后几乎不再需要很多配置,收发开始之后数据主要还是交由FPGA的逻辑处理,那已经跟UART这个控制接口无关了。

在ZEDBOARD+FMCOMMS3中,AD9361的SPI口是接在PL的引脚上,但是使用PS的SPI核通过EMIO进行引出控制,这就要求我们另外单独提供做一个符合AD9361的SPI时序的AXI_LITE_SLAVE的IP。还好不是接在PS的专用MIO上,否则我们就没有办法使用纯PL实现对AD9361的SPI总线的读写。

上述就是做好的这样一个去掉PS的AD9361配置的设计。我们还可以看到这个MASTER其实可以通过一个INTERCONNECT模块连接控制很多AXI_LITE_SLAVE。

下一篇我们分析和实现这个用串口实现的AXI_MASTER。