Ultrascale系列的可编程输入延迟组件原语为IDELAYE3,IDELAYE3可以用于延迟除时钟外的任何输入信号,然后将其转发到fpga内部逻辑或是寄存到寄存器。IDELAY无法直接布线到全局时钟缓存,若想延迟时钟请使用MMCM和PLL生成时钟并使用其相移功能进行延迟。

7系列和Ultrascale系列的IDELAY原语架构与实现方式相差较大,7系列的IDELAYE2有32个抽头延迟线,IDELAYE3有512个抽头延迟线,每个抽头的分辨率如下:

Ultrascale系列,抽头分辨率为2.5ps~15ps:

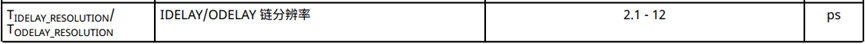

Ultrascale+系列,抽头分辨率为2.1ps~12ps:

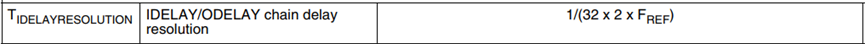

7系列的抽头分辨率如下图所示,抽头分辨率可以计算出一个值而不是一个范围:

按照IDELAYCTRL的参考时钟频率可以准确计算获取到,如200M参考时钟抽头分辨率为78ps,Ultrascale系列相对于7系列架构大改,体现便是U/U+系列的抽头增加到512个,同时每个抽头的分辨率就无法像7系列那样能得到一个准确的值,是一个波动的范围值,抽头分辨率随着工艺温度电压的变化而变化。

每个单独的抽头都未经校准,但是IDELAYCTRL组件中提供了用于校准延迟线的逻辑。

IDELAYE3有两种模式COUNT和TIME模式:

COUNT模式:

不使用IDELAYCTRL组件,延迟线使用时不会校准,没有电压温度补偿;

延迟线仅用于抽头计数,无法对延时的时间计数,因为该模式下抽头精度无法确定;

TIME模式:

必须使用IDELAYCTRL组件;

延时线使用时会按照请求的延时时间校准,进行电压温度补偿以确保延时值不变;

IDELAYE3和IDELAYCTRL两个组件的参考时钟频率必须匹配;

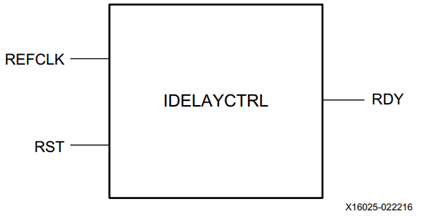

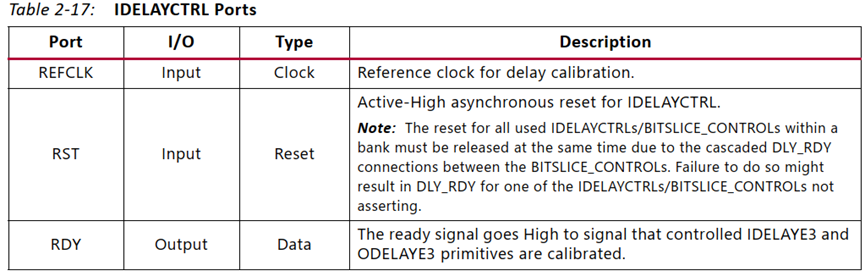

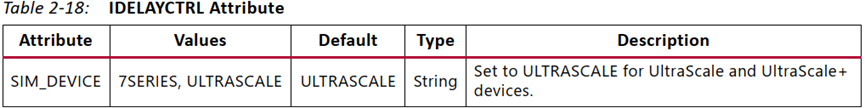

IDELAYCTRL组件:

IDELAYCTRL框图:

IDELAYCTRL例化模板:

IDELAYCTRL #(

.SIM_DEVICE("ULTRASCALE") // Must be set to "ULTRASCALE"

)

IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(REFCLK), // 1-bit input: Reference clock input

.RST(RST) // 1-bit input: Active high reset input. Asynchronous assert, synchronous deassert to

// REFCLK.

);

例化模板与7系列一致,且端口基本也相同;

如果使用了IDELAYE3或ODELAYE3的TIME模式,就必须例化IDELAYCTRL组件,如果使用COUNT模式,就不使用IDELAYCTRL组件;

IDELAYCTRL组件每个bank存在8个,每个半字节有1个,组件将在其区域内将TIME模式下配置的各个延迟线校准到其设定值,以补偿工艺、电压、温度(PVT)带来的影响。

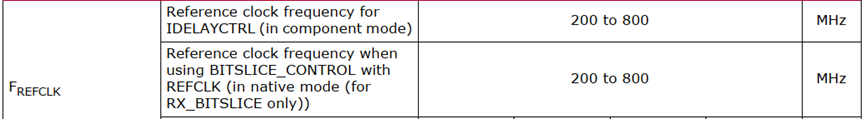

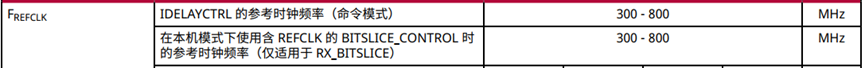

REFCLK:参考时钟,使用时参考时钟与其联合使用的IDELAYE3和ODELAYE3设置相同值;

Ultrascale器件参考时钟,范围为200~800MHZ:

Ultrascale+器件参考时钟,范围为300~800MHZ:

在使用时固定使用例化模板默认的300M即可;

RST:高有效异步复位;

RDY:就绪信号高有效,拉高表示受控的IDELAYE3或ODELAYE3原语已经校准;

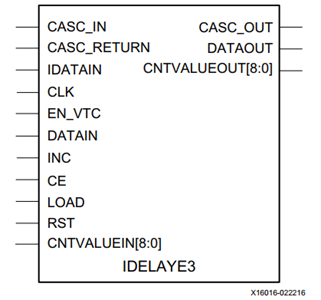

IDELAYE3组件:

IDELAYE3框图:

IDELAYE3例化模板:

IDELAYE3 #(

.CASCADE("NONE"), // Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE)

.DELAY_FORMAT("TIME"), // Units of the DELAY_VALUE (COUNT, TIME)

.DELAY_SRC("IDATAIN"), // Delay input (DATAIN, IDATAIN)

.DELAY_TYPE("FIXED"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD)

.DELAY_VALUE(0), // Input delay value setting

.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK

.IS_RST_INVERTED(1'b0), // Optional inversion for RST

.REFCLK_FREQUENCY(300.0), // IDELAYCTRL clock input frequency in MHz (200.0-2667.0)

.SIM_DEVICE("ULTRASCALE"), // Set the device version (ULTRASCALE)

.UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL, SYNC)

)

IDELAYE3_inst (

.CASC_OUT(CASC_OUT), // 1-bit output: Cascade delay output to ODELAY input cascade

.CNTVALUEOUT(CNTVALUEOUT), // 9-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data output

.CASC_IN(CASC_IN), // 1-bit input: Cascade delay input from slave ODELAY CASCADE_OUT

.CASC_RETURN(CASC_RETURN), // 1-bit input: Cascade delay returning from slave ODELAY DATAOUT

.CE(CE), // 1-bit input: Active high enable increment/decrement input

.CLK(CLK), // 1-bit input: Clock input

.CNTVALUEIN(CNTVALUEIN), // 9-bit input: Counter value input

.DATAIN(DATAIN), // 1-bit input: Data input from the logic

.EN_VTC(EN_VTC), // 1-bit input: Keep delay constant over VT

.IDATAIN(IDATAIN), // 1-bit input: Data input from the IOBUF

.INC(INC), // 1-bit input: Increment / Decrement tap delay input

.LOAD(LOAD), // 1-bit input: Load DELAY_VALUE input

.RST(RST) // 1-bit input: Asynchronous Reset to the DELAY_VALUE

);

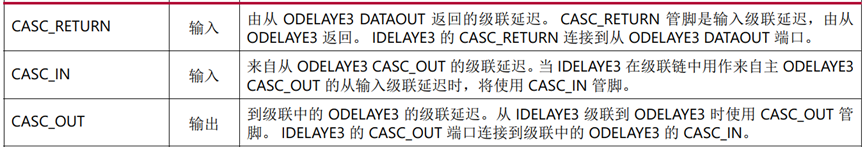

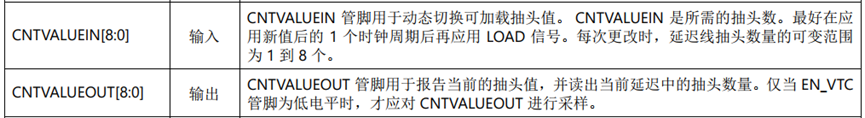

IDELAYE3端口:

CASC_RETURN:级联使用端口,连接到ODELAYE3 DATAOUT端口,从ODELAYE3返回的输入级联延迟;

CASC_IN:级联使用端口,连接到ODELAYE3 CASC_OUT端口,当IDELAYE3在级联链条中用作ODELAYE3的从属输入级联延迟时,使用该端口;

CASC_OUT:级联使用端口,连接到ODELAYE3 CASC_IN端口,当IDELAYE3在级联链条中用作ODELAYE3的主级联时,使用该端口;

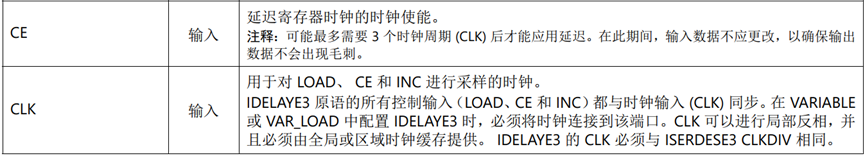

CE:延迟寄存器时钟使能,使用方法与7系的CE端口相同;

CLK:控制端口的时钟,用于对LOAD、CE、INC端口进行采样的时钟,时钟需由全局时钟缓存提供,原语的控制输入端口与该时钟同步;

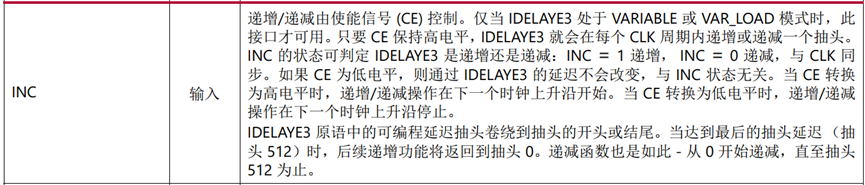

INC:和7系INC信号使用方法相同,和CE搭配控制延迟递增递减,仅当原语处于VARIAVLE和VAR_LOAD模式时才可用。CE=1&INC=1时递增,CE=1&INC=0时递减,CE=0时延迟不会变化,使用时使能一个周期即可;

IDELAYE3的抽头同样具有环绕操作,当抽头数到511时递增将抽头数变到0,当抽头数到0时递减将抽头数变到511;

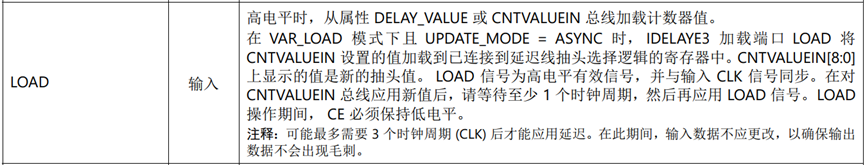

LOAD:与7系中的load信号作用相同,用于将cntvaluein端口的新抽头值加载到原语中;

CNTVALUEIN:供加载的新抽头值,范围0~511,且每次更改时,更改范围不要超过8,否则可能造成信号出问题;

CNTVALUEOUT:显示当前延迟状态的抽头值;

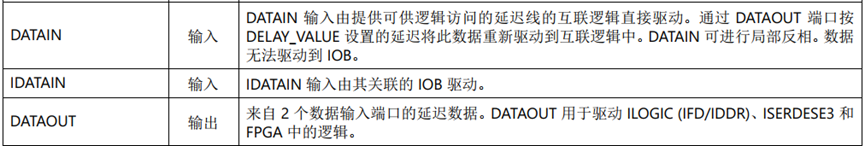

DATAIN:FPGA内部逻辑的输入;

IDATAIN:来自IOB的输入,当使用DATAIN作为输入数据时,如果无法找到一个有效的IDATAIN输入,那就将IDATAIN管脚悬空;

DATAOUT:IDELAYE3原语延迟的信号输出;

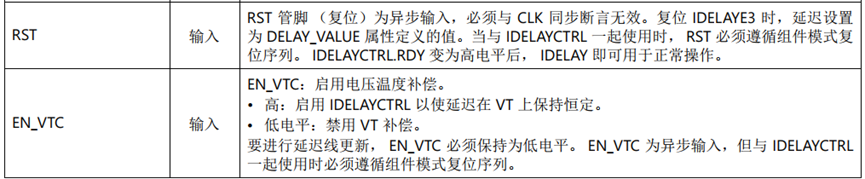

RST:异步高有效复位;

EN_VTC:电压温度补偿开启的使用信号,COUNT模式下不能使用,必须保持为0,TIME模式下需要使用,在延迟工作时要启用温度电压补偿,在修改抽头值时需要关闭温度电压补偿,修改完后启用;

参数部分待下一节讲解;

本文章由威三学社出品

对课程感兴趣可以私信联系