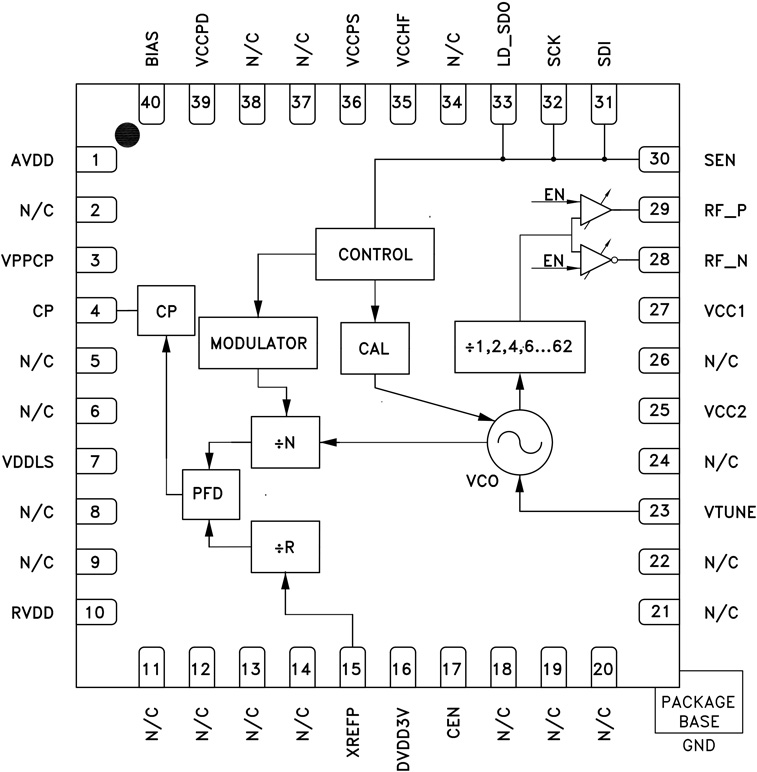

锁相环HMC830 集成VCO 的小数N分频PLL,输出频率支持25~3000 MHz,国产24所有PIN-TO-PIN替换的器件,在UD PCIe-402上用此器件接收2外部10MHz参考信号,然后锁出任意的频点给FPGA使用,以便用于多设备的同步、ECL的任意速率的发射等场景。

该芯片控制比较简单,采用标准FPGA实现的SPI总线即可对其进行控制。配置时要注意的是:

1 SEN是高有效。主机(Master)拉低 SDI,拉低 SEN,并产生一个 SCK 的上升沿

1.1SEN 拉低表示开始一次通信(SEN = Serial Enable)。

1.2SDI 这时候拉低,表示这是一个 "写操作"。

1.3紧接着产生第一个 SCK 的上升沿(时钟信号)。

2 从机(Slave)在 SEN 拉低之后的第一个 SCK 上升沿读取 SDI,判断是读还是写

2.1这个时候从机会读取 SDI 的状态:

2.2若 SDI = 0:是 写 操作。

2.3若 SDI = 1:是 读 操作(通常这种协议里读操作是不常见的)。

3 主机在接下来的 6 个 SCK 下降沿 上,依次发送地址(共 6 bit,MSB First)每个地址位在 SCK 的下降沿放到 SDI 上。

4 从机在这 6 个时钟的 上升沿 上接收这 6 位地址1也就是说:主机在 SCK 下降沿发数据,从机在上升沿接收。

5 接下来主机发送 24 位数据,也是在 下降沿 上发送继续沿用刚才的节奏:主机在 下降沿 上发送 24 个数据位。仍然是 MSB first。

6 从机在随后的 24 个 上升沿 上接收这 24 位数据

7 在第 32 次 上升沿 后,从机把刚才收到的地址+数据写入寄存器

7.1从第 2 个到第 31 个 SCK 上升沿,是数据接收阶段。

7.2第 32 个上升沿时:正式将数据加载写入到目标寄存器里(完成写入)。

8 主机释放(拉高) SEN,结束传输SEN 要保持一小段时间(t5)再拉高,表示传输结束。

6 寄存器

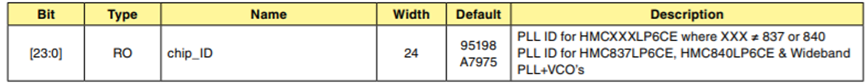

6.1Reg0x00

读取寄存器可读芯片id为0x0a7975.

6.2Reg0x01

确认为spi程控 写入0X000002.

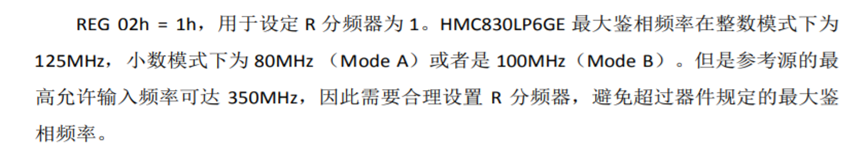

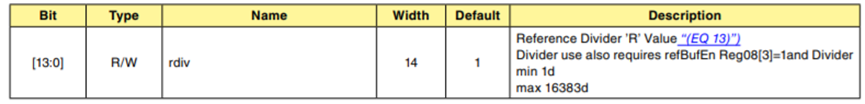

6.3Reg0x02

R分频器。

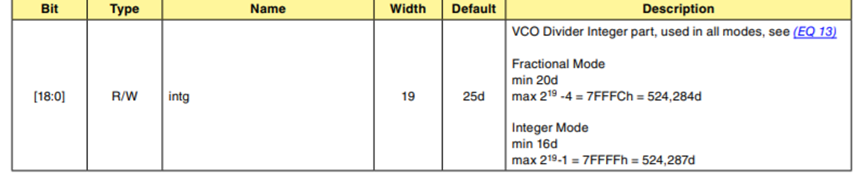

6.4Reg0x03

N倍频器 整数部分

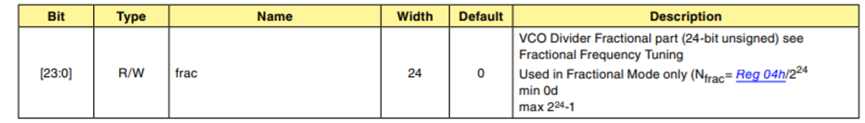

6.5Reg0x04

N倍频器 小数部分

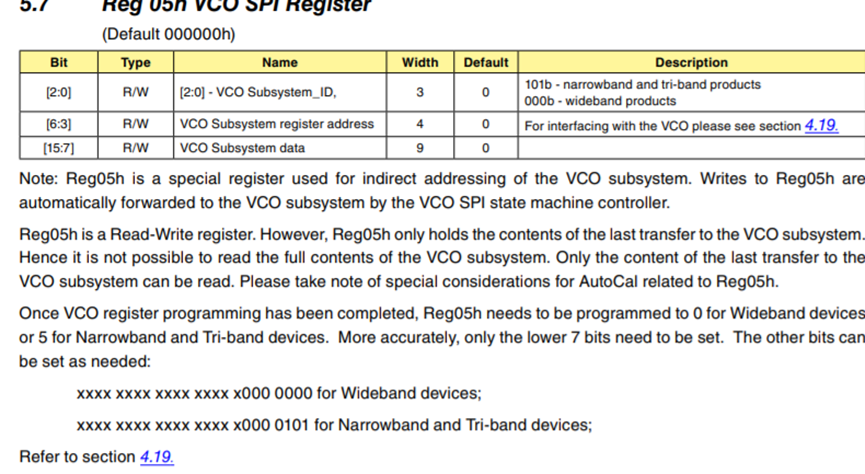

6.6Reg0x05

- Reg[2:0]对应硬件HMC830直接取 3'b000 。

- Reg[6:3]对应子系统地址。

- Reg[15:7]对应子系统数据。

- 只要reg05做任何改变 就需要再次写入0x05=000000h;才能使寄存器生效。

- 读取时只能读取最后一次传入数据。

- 演示控制增益 (单端差分输出也在这里选择)

REG 05h=E090h=1110000010010000

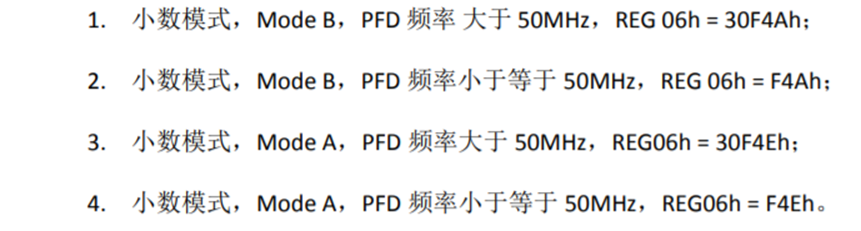

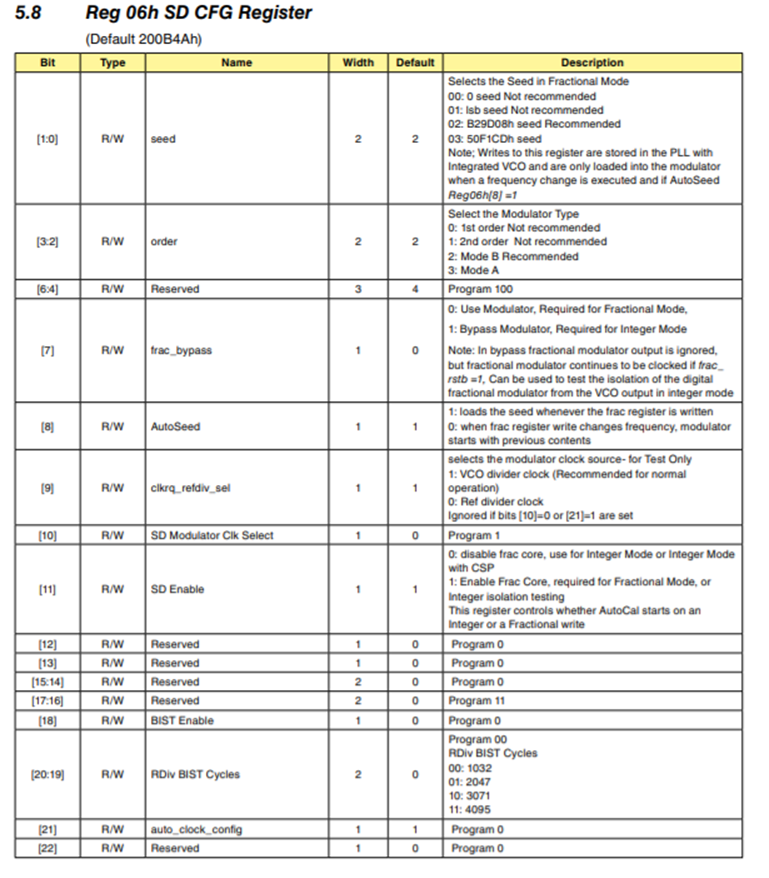

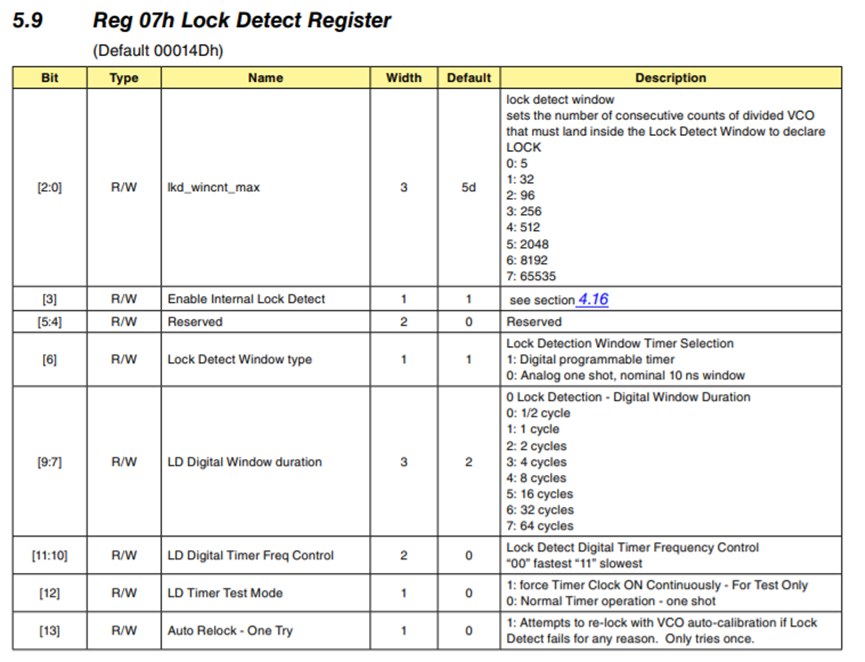

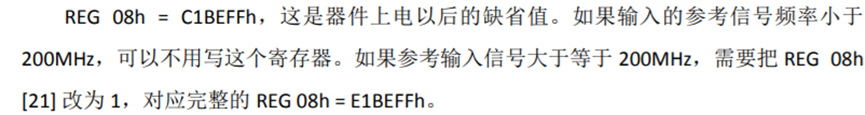

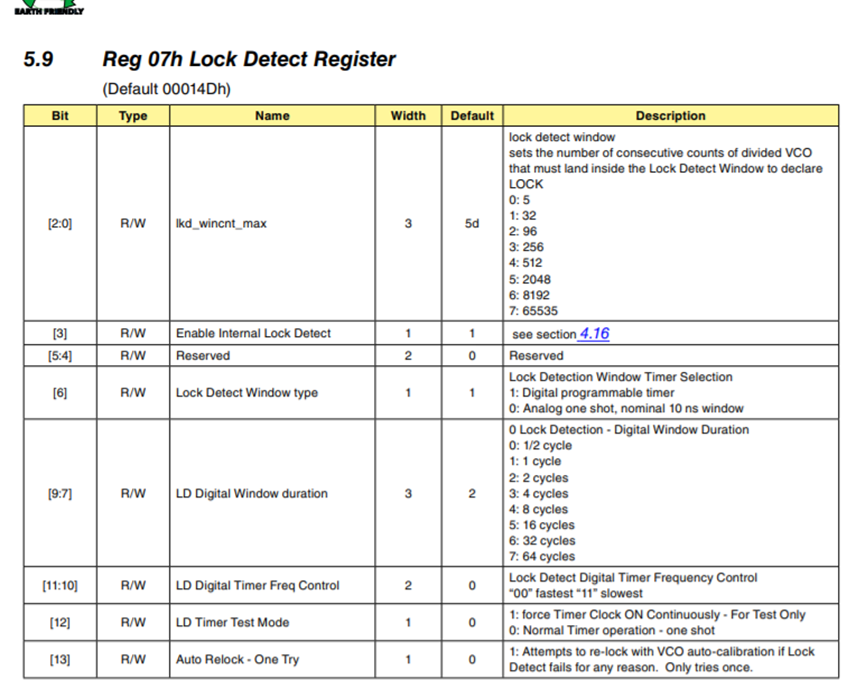

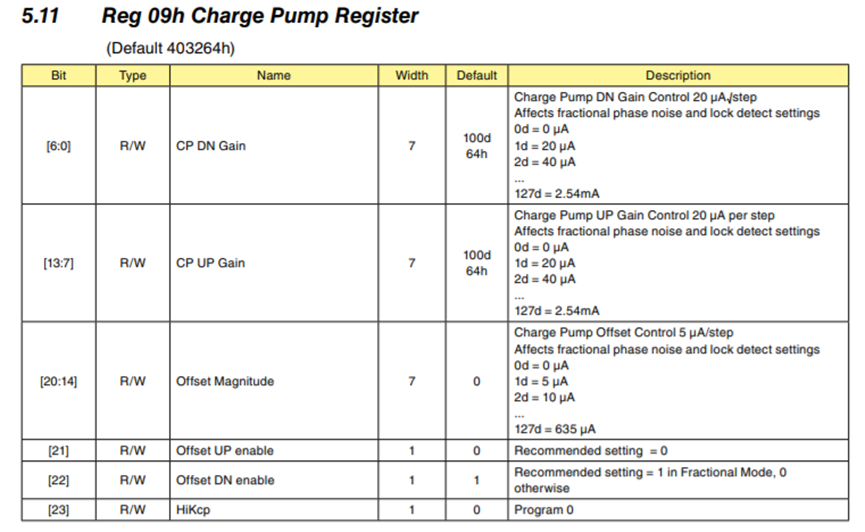

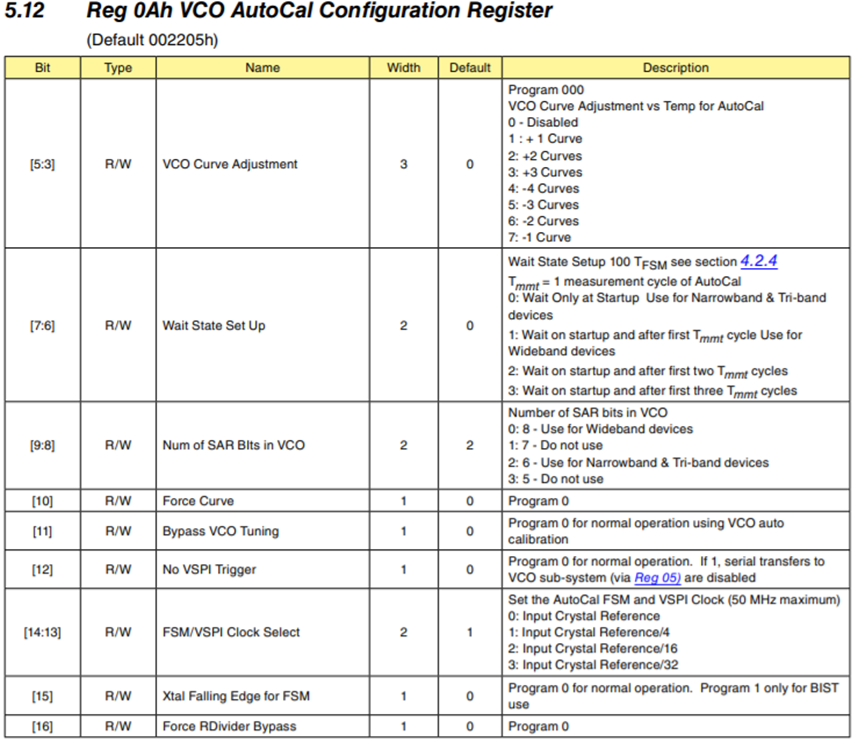

2:0\]=000, \[6:3\]=0010,控制增益 \[15:7\]=\[111000001\],分频器为1射频增益最大  ##### 6.7Reg0x06 小数模式选择   ##### 6.8Reg0x07 锁定指示  ##### 6.9Reg0x08 根据参考信号变化 #####   ##### 6.10Reg0x09 电流设置寄存器。  ##### 6.11Reg0x0A Voc校准寄存器  ##### 6.12Reg0x0f LD锁定和回传