第五篇:多主仲裁与错误恢复

副标题 :从总线冲突到故障自愈------构建高可靠I2C系统的终极指南

1. 多主仲裁机制

1.1 仲裁原理与硬件实现

-

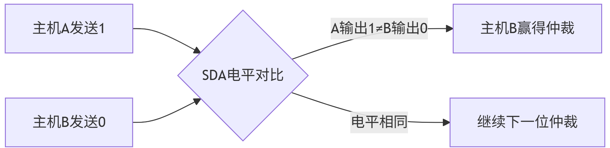

仲裁流程图解 :

-

仲裁失败处理 :

立即切换为从机模式

监测总线空闲后重试(随机退避算法)

1.2 仲裁波形深度解析

- 典型冲突场景 :

关键节点:- t₁: 主机A发送高电平,主机B发送低电平

- t₂: 主机A检测到SDA被拉低,释放总线

- t₃: 主机B继续完成传输

1.3 Verilog仲裁逻辑实现

verilog

// 仲裁检测模块

always @(negedge scl) begin

if (sda_out_reg != sda_in && master_mode) begin

arbitration_lost <= 1'b1;

master_mode <= 1'b0; // 切换为从机

retry_counter <= 8'd0;

end

end

// 随机退避重试

always @(posedge clk) begin

if (arbitration_lost) begin

if (bus_free && retry_counter == backoff_time)

master_mode <= 1'b1;

else

retry_counter <= retry_counter + 1;

end

end 2. 错误检测与恢复

2.1 错误分类与应对策略

| 错误类型 | 检测方法 | 恢复策略 |

|---|---|---|

| 从机无应答 | ACK位检测 | 重发数据包(最多3次) |

| 总线死锁 | 超时计数器(>50ms) | 发送STOP条件强制复位 |

| 时钟拉伸超时 | SCL低电平持续时间监控 | 主控复位并重新初始化 |

2.2 硬件CRC校验加速

-

CRC8算法实现 :

verilog// 多项式: x^8 + x^2 + x + 1 function [7:0] crc8; input [7:0] data; input [7:0] crc; begin crc8[0] = data[7] ^ crc[6]; crc8[1] = data[6] ^ crc[7] ^ crc[0] ^ crc[6]; // ... 完整CRC逻辑 end endfunction -

性能对比 :

| 实现方式 | 时钟周期数 | 资源消耗(LUT) |

|---|---|---|

| 软件计算 | 72 | 0 |

| 硬件加速 | 8 | 42 |

3. 高级诊断功能

3.1 错误注入测试平台

-

可注入错误类型 :

pythonerror_types = [ "NACK Injection", "Clock Stretch", "Glitch on SDA", "Arbitration Loss" ] -

自动化测试框架 :

测试流程: 1. 发送正常数据包 2. 注入指定错误 3. 监测控制器响应 4. 生成测试报告

3.2 JTAG调试接口设计

- 寄存器映射 :

| 地址 | 名称 | 功能 |

|---|---|---|

| 0x00 | ERR_STATUS | 错误类型编码 |

| 0x04 | RETRY_COUNTER | 重试次数统计 |

| 0x08 | DEBUG_CONTROL | 错误注入使能 |

-

Vivado ILA配置 :

tclcreate_debug_core u_ila ila set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila] connect_debug_port u_ila/clk [get_nets clk]

4. 设计注意事项

4.1 总线负载管理 :

总线上主设备不宜过多(建议≤3个),避免频繁仲裁降低效率。

增加 上拉电阻 优化信号边沿(典型值:4.7kΩ@3.3V)。

4.2 错误恢复机制 :

仲裁失败的主设备应 等待随机时间 后重试,避免重复冲突。

添加 总线监控逻辑 (如I2C协议分析仪),记录冲突事件。

4.3 时序参数验证 :

使用示波器检查 建立时间(t_SU;DAT) 和 保持时间(t_HD;DAT) ,确保仲裁期间时序满足规范。