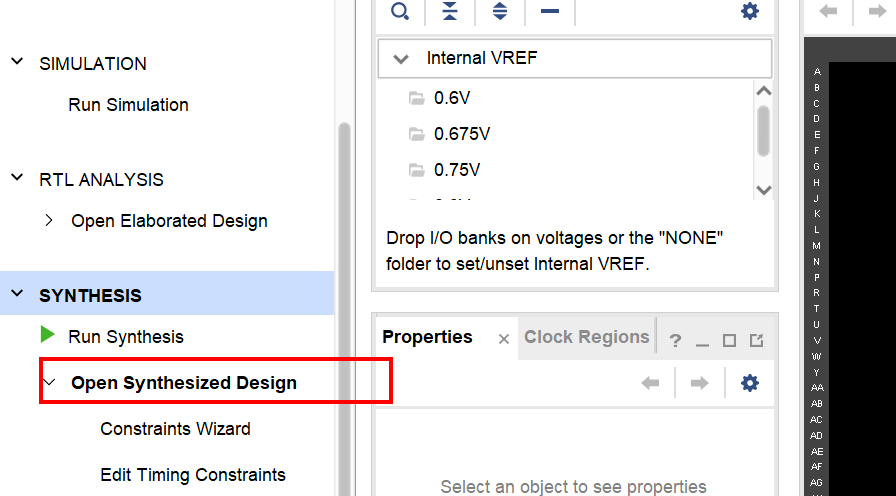

在工程综合完成或者implement完成后,打开综合设计或者实现设计。

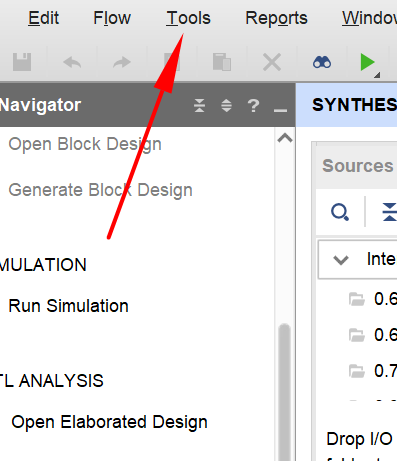

toots--->Edit Device Properties--->打开比特流设置

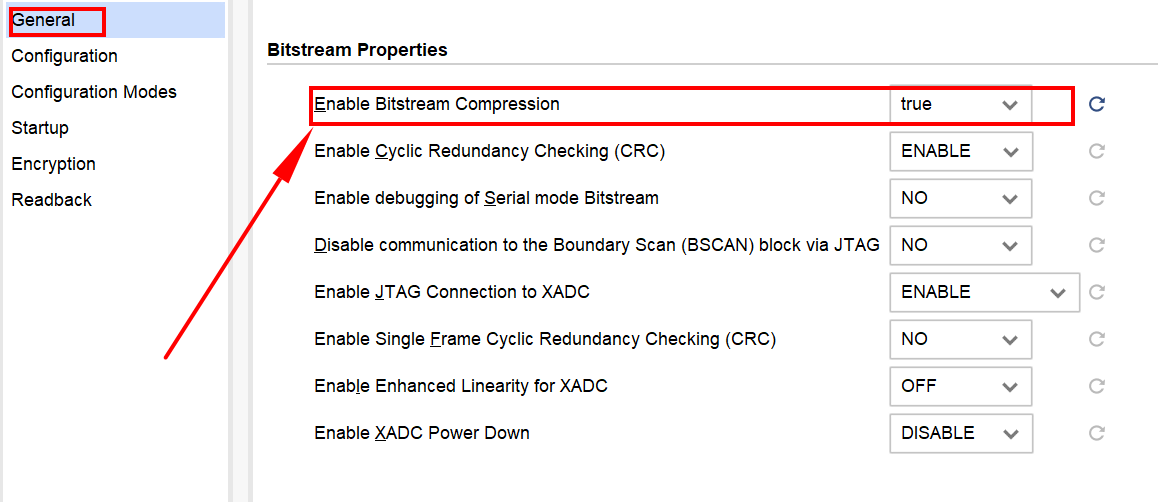

将bitstream进行压缩

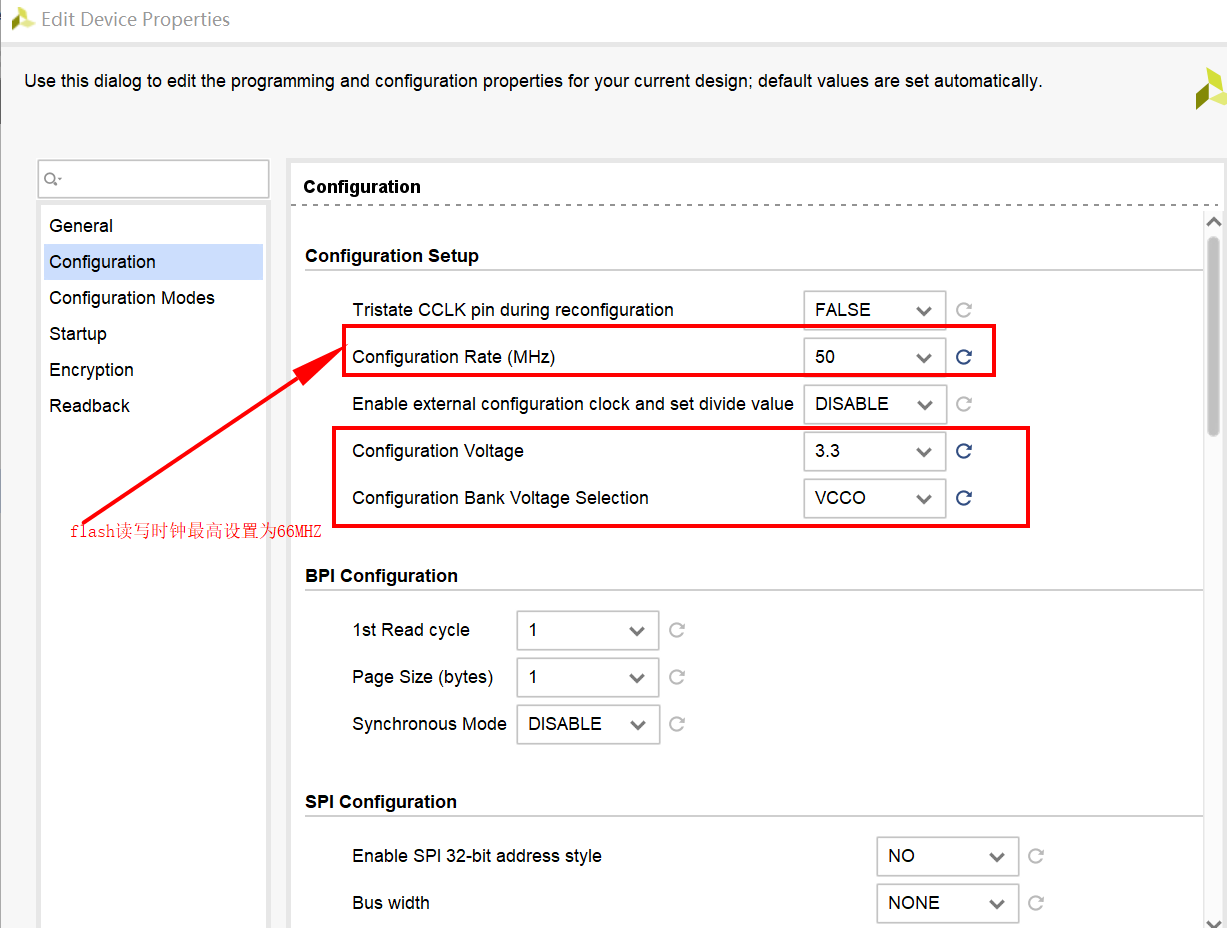

上图中,时钟频率选择的档位有限,最大为66MHZ

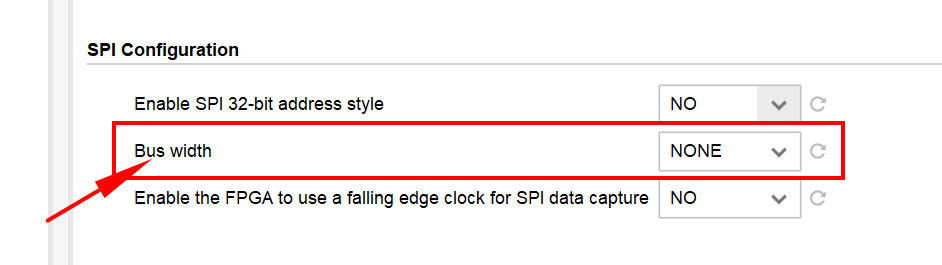

io的bus width可以设置为x1,x2,x4

- vivado在设计过程中生成的bitstream需要通过FPGA特定的配置管脚引脚导入到FPGA中。FPGA这些专用的配置管脚在不同的电压级别下决定了其工作在不同的配置模式。

- 纯FPGA的bitstream加载和ZYNQ的加载不同,其中纯FPGA加载是直接通过外部Flash进行加载的,而ZYNQ的Flash不是通过FPGA加载的,而是通过ARM进行加载,所以QSPI的x1和x4是对单纯的FPGA是可配的,ZYNQ一般是只能进行文件的压缩配置和电压配置。

- 烧录需要注意:FPGA如果选择生成bit文件是QSPI X4的,如果在批量烧写完FLASH之后再贴装的情况下,需要工厂烧录器设置为x4的烧写模式。要不,贴装之后FPGA很有可能起不来。

- 参考:Xilinx FPGA------Vivado生成bit文件时需要添加的约束_edit device properties vivado-CSDN博客

- 参考:https://zhuanlan.zhihu.com/p/457990312

- 参考:xilinx fpga 启动速度加快_专栏_易百纳技术社区

- 注意:不同型号的FPGA对外部QSPI Flash支持的最高频率是不一样的。XC6SLX45支持的最高频率仅为26MHz, 而XC7K325T支持的最高频率高达66MHz

- 参考:Xilinx FPGA下如何加快QSPI Flash加载速度_如何提高spi flash访问速度-CSDN博客

- 关于烧录文件:固化文件bin文件最小,hex文件最大,mcs大小居中

- 参考:关于XDC 约束固化flash流程_xdc约束为x4-CSDN博客

- 参考:FPGA:生成固化文件(将代码固化到板子上面)_fpga怎么将代码固定-CSDN博客

- 参考:FPGA------VIVADO生成固化文件,掉电不丢失_vivado固化bin文件-CSDN博客