CSI-2 协议详细解析(三):数据格式(Data Formats)

1. 格式分类与优先级

| 类型 | 主要格式(Primary) | 次要格式(Secondary) |

|---|---|---|

| YUV | YUV422 8-bit | YUV420 8-bit/10-bit (Legacy/CSPS) |

| RGB | RGB888, RGB565 | RGB666, RGB555, RGB444 |

| RAW | RAW8 | RAW6/7/10/12/14 |

| 其他 | 通用8位长包, 用户自定义字节包 | - |

- 强制支持要求 :

发送端(TX)至少支持一种主要格式。

接收端(RX)必须支持所有主要格式。

2. 通用数据格式

(1) 数据类型代码

| Data Type | 描述 |

|---|---|

0x10 |

Null(空包,内容忽略) |

0x11 |

Blanking(消隐数据,内容忽略) |

0x12 |

Embedded 8-bit(嵌入式非图像数据) |

0x13-0x17 |

Reserved(保留) |

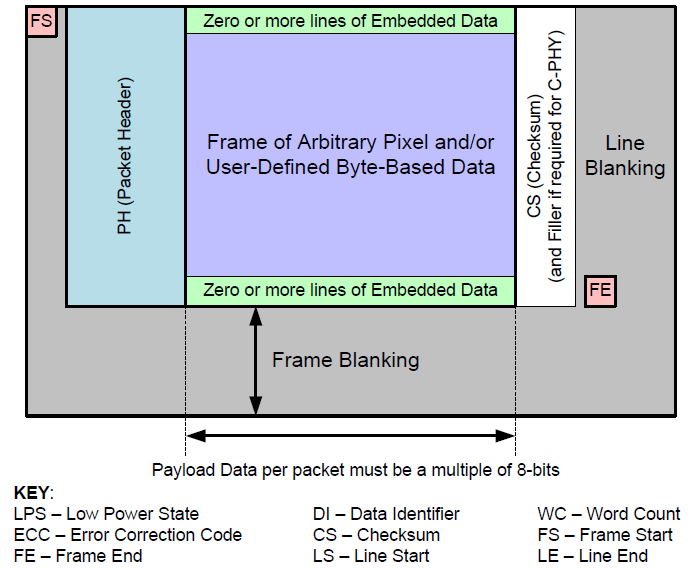

(2) 嵌入式数据(Embedded Data)

- 位置 :可置于帧头(零或多行)或帧尾(零或多行)

- 用途 :传输非图像信息(如传感器参数、时间戳)。

- 包结构 :使用

0x12数据类型,负载长度=8位字节的整数倍。

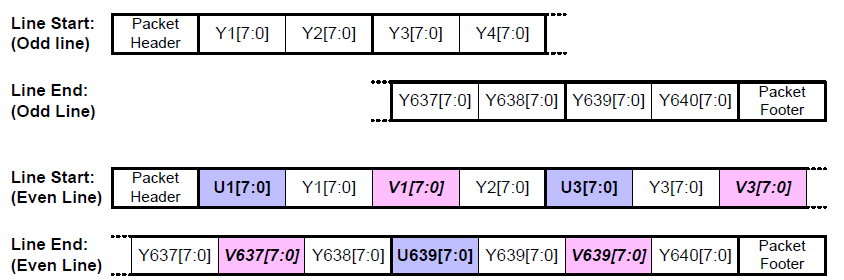

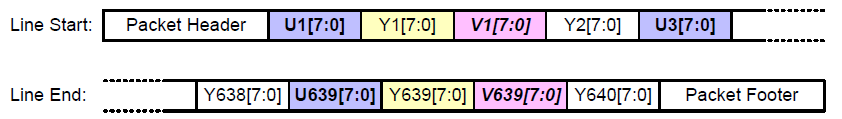

3. YUV格式

(1) 关键特性

-

颜色空间 :基于ITU-R BT.601的8位伽马校正Y'CbCr

-

传输规则 :每行图像数据=1个长包。

-

子格式对比 :

格式 传输方式 行约束 包长度规则(表10-15) Legacy YUV420 8-bit 奇行传 UYYY...,偶行传VYYY...总行数必须为偶数 每包=3字节/2像素 (24位) YUV420 8-bit 奇行仅传 Y,偶行传UYYY(同YUV422)总行数必须为偶数 奇行:2字节/2像素 ``偶行:4字节/2像素 YUV422 8-bit 每像素传 UYVY序列(图82)- 每包=4字节/2像素 (32位)

(2) 字节映射规则

-

Legacy YUV420

Byte n=V/U分量→Byte n+1=Y1→Byte n+2=Y2

-

YUV422 :

Byte n=U→Byte n+1=Y1→Byte n+2=V→Byte n+3=Y2

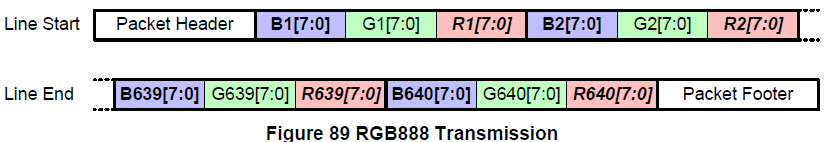

4. RGB格式

(1) 关键特性

-

颜色空间 :基于IEC 61966的非线性sRGB'

-

子格式对比 :

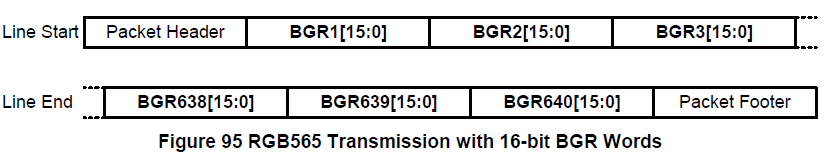

格式 位深 传输单元 包长度规则(表17-20) RGB888 8位/分量(24位) 3字节/像素 每包=3字节×像素数 RGB565 5-6-5位(16位) 2字节/像素 每包=2字节×像素数 RGB666 6位/分量(18位) 3字节/2像素 每包=3字节×(像素数/2)

(2) 字节映射规则

-

RGB888 :

Byte n=B→Byte n+1=G→Byte n+2=R

-

RGB565 :

Byte n=G2 G1 G0 B4 B3 B2 B1 B0(低8位)

Byte n+1=R4 R3 R2 R1 R0 G5 G4 G3(高8位)

5. RAW格式

(1) 关键特性

-

数据来源 :相机传感器原始Bayer模式数据

-

通用规则 :每行图像数据=1个长包, 像素需填充对齐

-

子格式对比 :

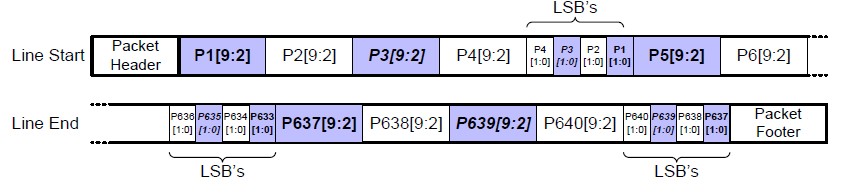

格式 位深 传输单元 包长度约束 填充要求 RAW8 8位/像素 1字节/像素 每包=1字节×像素数 无 RAW10 10位/像素 4字节存储3像素(图110) 每包=4字节×(像素数/3) 像素数需为4的倍数 RAW12 12位/像素 3字节存储2像素 每包=3字节×(像素数/2) 像素数需为2的倍数

(2) 字节映射示例(RAW10)

- 像素序列 :

Pixel1 (10位)→Pixel2 (10位)→Pixel3 (10位) - 字节打包 :

6. 用户自定义格式

- 数据类型 :

0x30-0x37。 - 特性 :

负载为 任意8位字节流 (图118)。

长度可变,无内容限制(如传输JPEG压缩数据)。

包结构:长包格式,负载长度=字节整数倍。

关键设计约束

- 包负载对齐 :所有负载长度必须是 8位的整数倍

- 数据类型一致性 :包头中的

Data Type必须匹配负载格式 - 行长度统一 :同一帧内同虚拟通道同数据类型的所有包 长度必须相等 (YUV420例外)。

总结 :本章定义了CSI-2支持的像素级数据编码规则,涵盖主流图像格式(YUV/RGB/RAW)及自定义数据,通过严格的包长度约束和字节映射确保传输效率。实际实现需重点处理对齐要求(如RAW10的4像素对齐)和格式兼容性。查看CSI-2协议,了解更多更详细的数据格式。