目录

[使用以下计算得出的延迟值对SYSREF DELAY寄存器进行编程:](#使用以下计算得出的延迟值对SYSREF DELAY寄存器进行编程:)

实现可重复的延迟

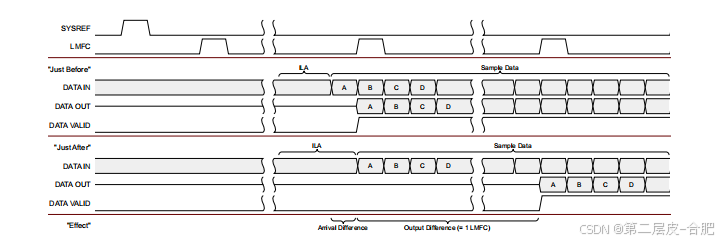

在某些情况下,虽然不需要知道端到端延迟的具体数值,但必须确保这种延迟能够稳定重复。由于基于高速收发器的链路,如JESD204B物理层中使用的链路,在重置或电源周期后不会保持相同的数据路径延迟,因此当接收核心接收到的起始数据接近LMFC边界时,可能会出现系统问题。这些系统可能无法处理在重启之间链路延迟的小变化。图展示了样本数据在LMFC边界前后到达的情况,说明了重启可能带来的影响。可以看出,核心接收到的数据时间的微小差异,可能导致输出数据定时的变化达到1个LMFC周期。

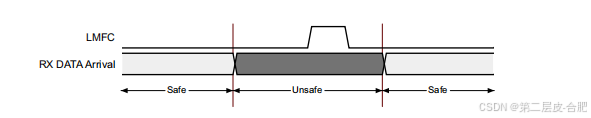

为防止出现这种情况,必须在LMFC边界周围设置一个边界,数据的开始必须避开这个边界。

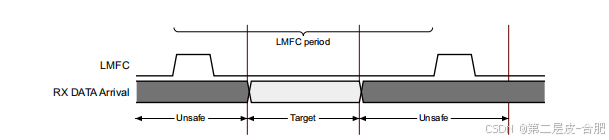

LMFC是一种周期性信号,需要一个目标窗口(TW)来瞄准。图显示了这一点。如果数据可以在该TW内开始,则链路的鲁棒性得到保证。

TW通常可以可靠地设置在LMFC边界前后各2个CORE_CLK周期之间。注意:这假设ADC输出时序的变化不超过四个字节。如果输出变化超过四个字节,可以增加裕度并相应减少TW。解决方法是调整内部LMFC以适应固定的数据到达时间,确保到达的数据落在图所示的目标窗口内(即移动窗口)。

通过启动链接,并使用核心寄存器来确定已缓冲的数据量,然后逐步调整LMFC边界,直到达到可接受的值。这一过程在开发过程中只需执行一次,因为系统已经调整到确保数据到达在目标窗口内,之后就不需要再进行调整了。

此过程中使用的寄存器为

BUFFER ADJUST:JESD204B核心为每个JESD204B通道提供了一个可读的缓冲调整寄存器。该寄存器显示了在输出数据释放时,每个通道在LMFC边界处的通道对齐缓冲区中的数据量。注意:由于链路上的通道偏斜,每个通道的缓冲调整寄存器值可能不同。关注的是所有通道中最小的值,这标志着所有通道都有有效数据的时间点,即核心准备释放数据的时间点。此寄存器中的值以字节为单位计数,每个core CLK周期有四个字节。

SYSREF DELAY:位于SYSREF处理寄存器:此寄存器将内部LMFC边界相对于SYSREF延迟一个整数个core CLK周期。因此,设置SYSREF DELAY为0x1将导致LMFC延迟四个字节。

详细调试过程-实现可重复的延迟

1.计算多帧(MF)大小。MF=F*K(其中F=帧大小,K=每个多帧中的帧数)。

MF值越大,目标窗口就越大。建议选择一个K值,使得MF至少为32个字节。

2.根据MF大小计算字节中的TW最大值。

具体公式为:Max =(MF-0x8),Min= 0x8。(其中0x8代表2个CORE_CLK周期)

3.配置系统并启动链接。此时所有延迟都是未知的。

4.链路运行后,读取每个正在使用的JESD204B通道的JESD204B RX核心BUFFER ADJUST寄存器。选择从该寄存器读取的最小值,并将其命名为BUF_FILL。

5.如果BUF_FILL落在最小值和最大值之间(在步骤2计算),则数据到达处于安全的TW内,无需采取进一步措施。但如果BUF_FILL不在最小值和最大值之间,则应采取以下措施。

使用以下计算得出的延迟值对SYSREF DELAY寄存器进行编程:

如果BUF_FILL值较低,则应将SYSREF DELAY值增加1或2,如下所示:如果BUF_FILL < Min - 4,则SYSREF DELAY应增加2;如果BUF_FILL < Min但> Min - 4,则SYSREF DELAY应增加1

如果缓冲器几乎满,则应将编程的SYSREF DELAY值增加3或4(即,1或2加上2的低裕量),如下所示:

b. Reset the JESD204B receive core and reinitialize the link. This step must be

performed before the modified SYSREF_DELAY value will affect the LMFC.

c. Re-read the BUFFER ADJUST register for every lane to confirm the data arrival is now

within the target window.

The calculated SYSREF DELAY value should be stored for future use when configuring

this link