基于FPGA的PID算法学习---------实现P比例控制算法

前言

学习内容:参考网站:

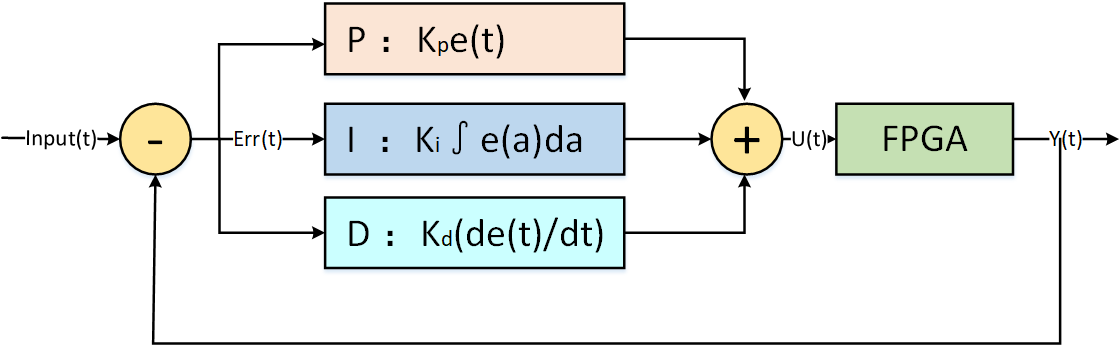

PID算法控制

PID即:Proportional(比例)、Integral(积分)、Differential(微分)的缩写。也就是说,PID算法是结合这三种环节在一起的。

闭环控制:输出会影响到输入,进而逐渐逼近目标。

一、P比例算法控制

P比例控制算法:

核心部分,大部分作用来自于P,I和D主要控制减小误差。

目标值:Target

实际值:Pid_out

误差值:e_t

弥补值:u_t

相关公式:

误差值:e_t=Target - Pid_out

弥补值:u(t)=Kp * e(t)

输出值:Pid_out = Pid_out + u(t)

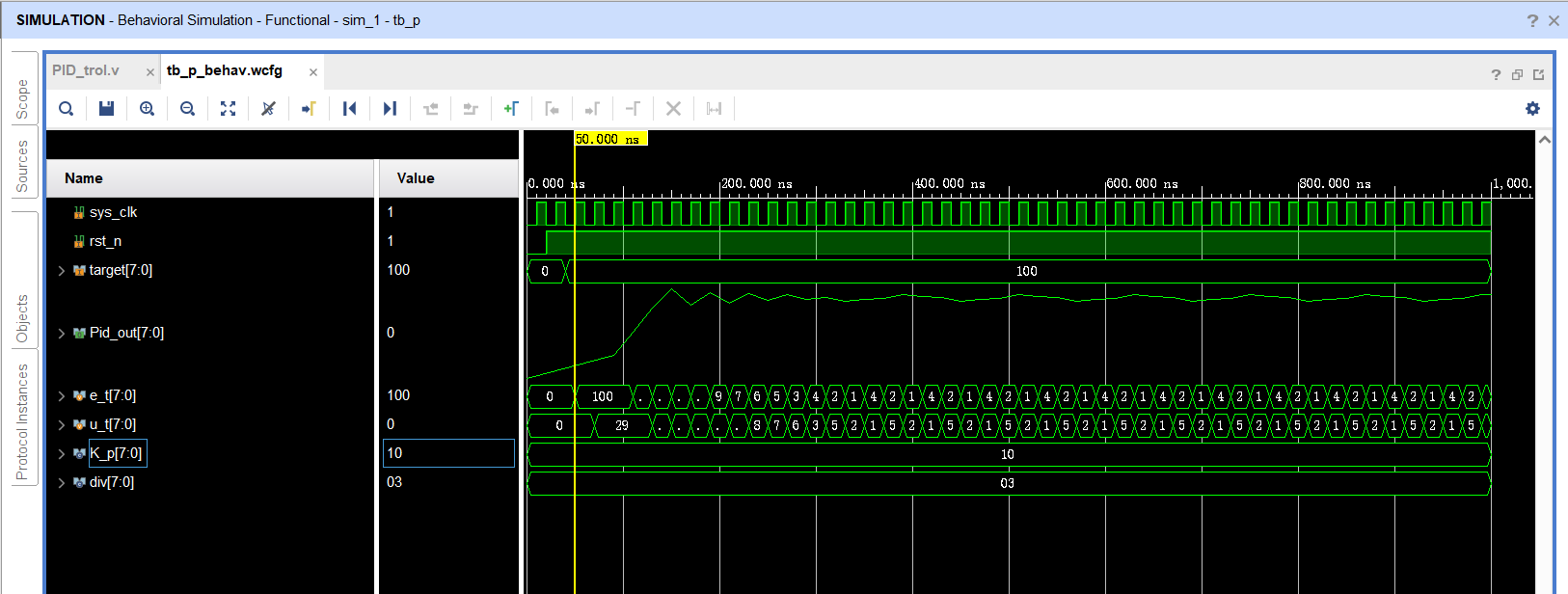

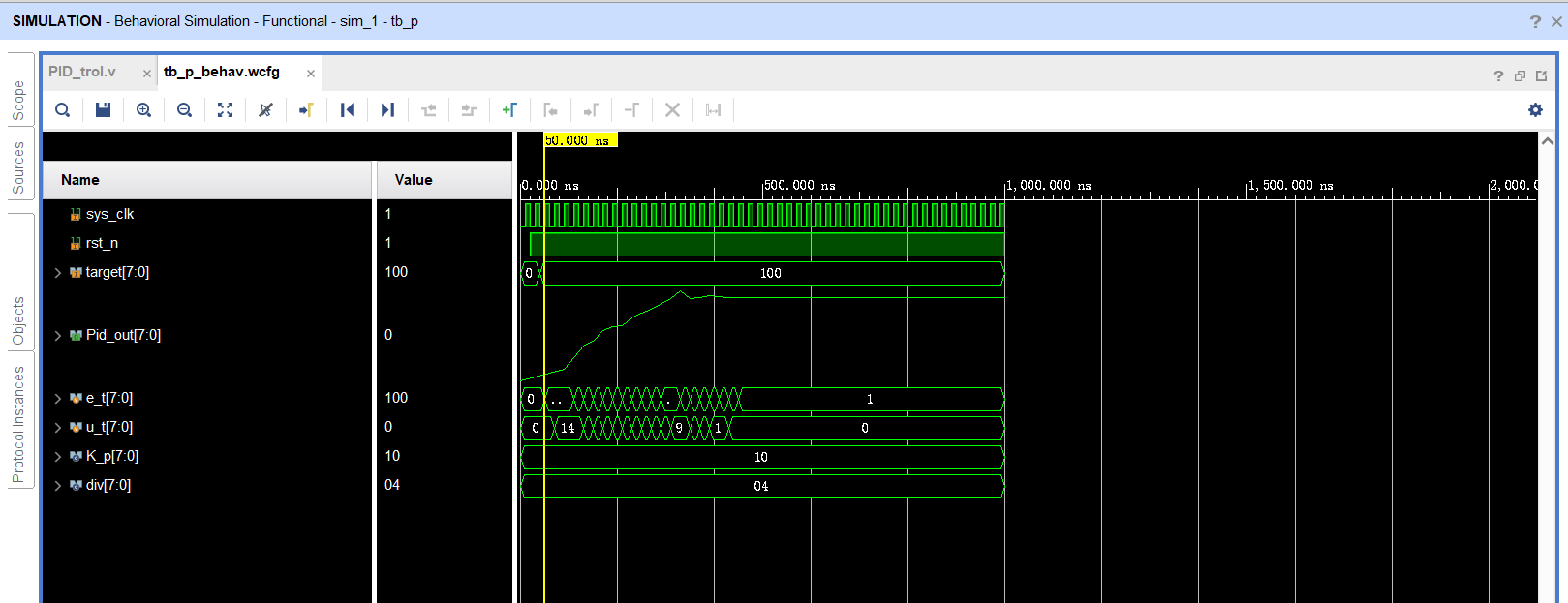

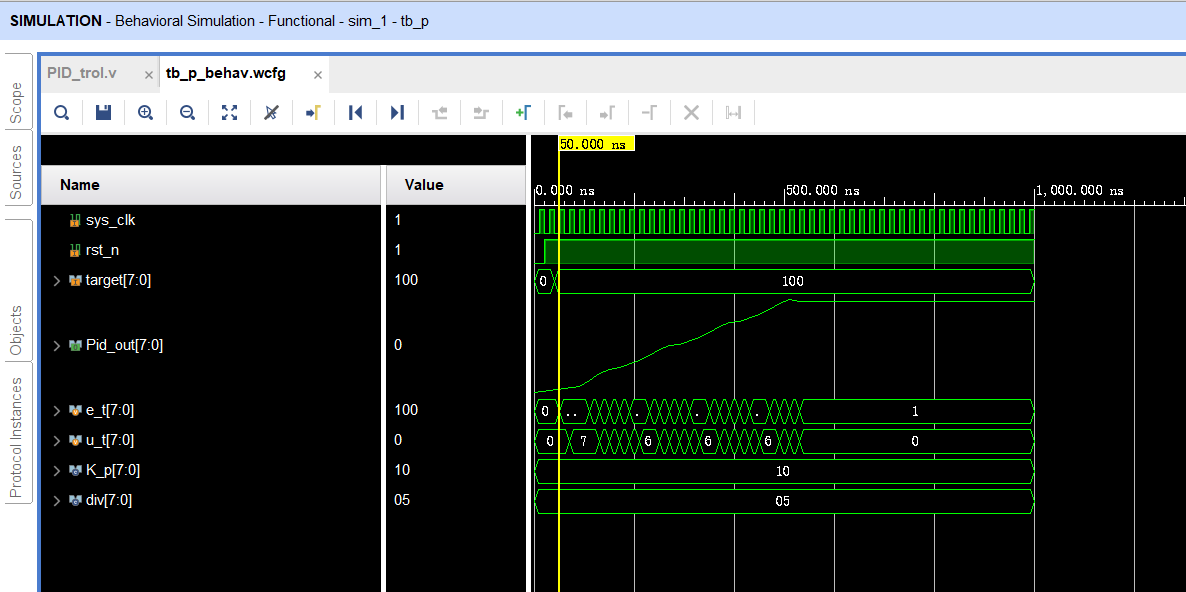

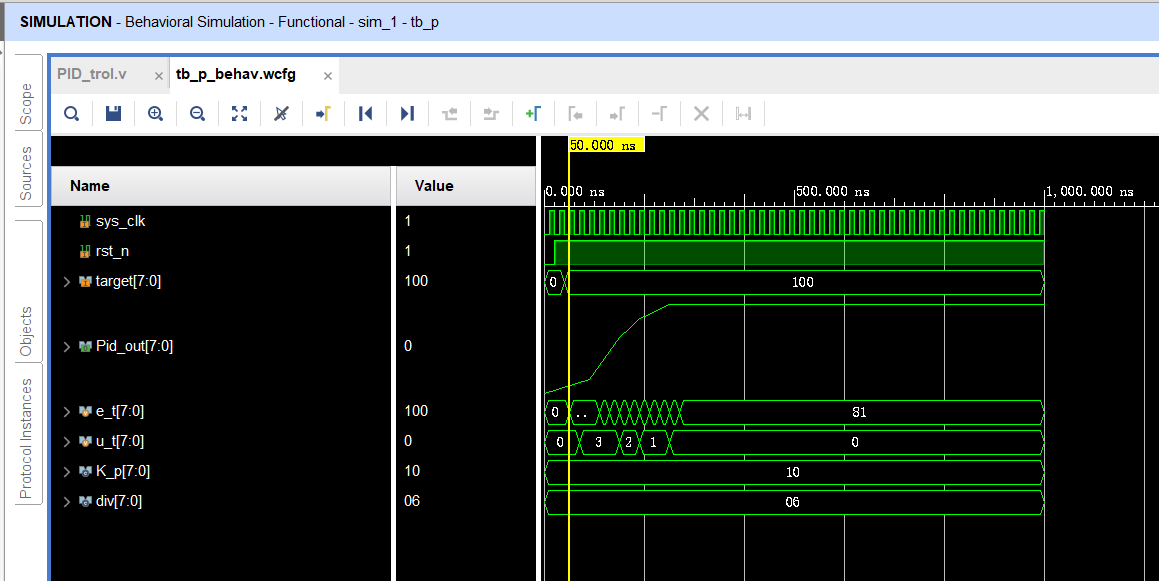

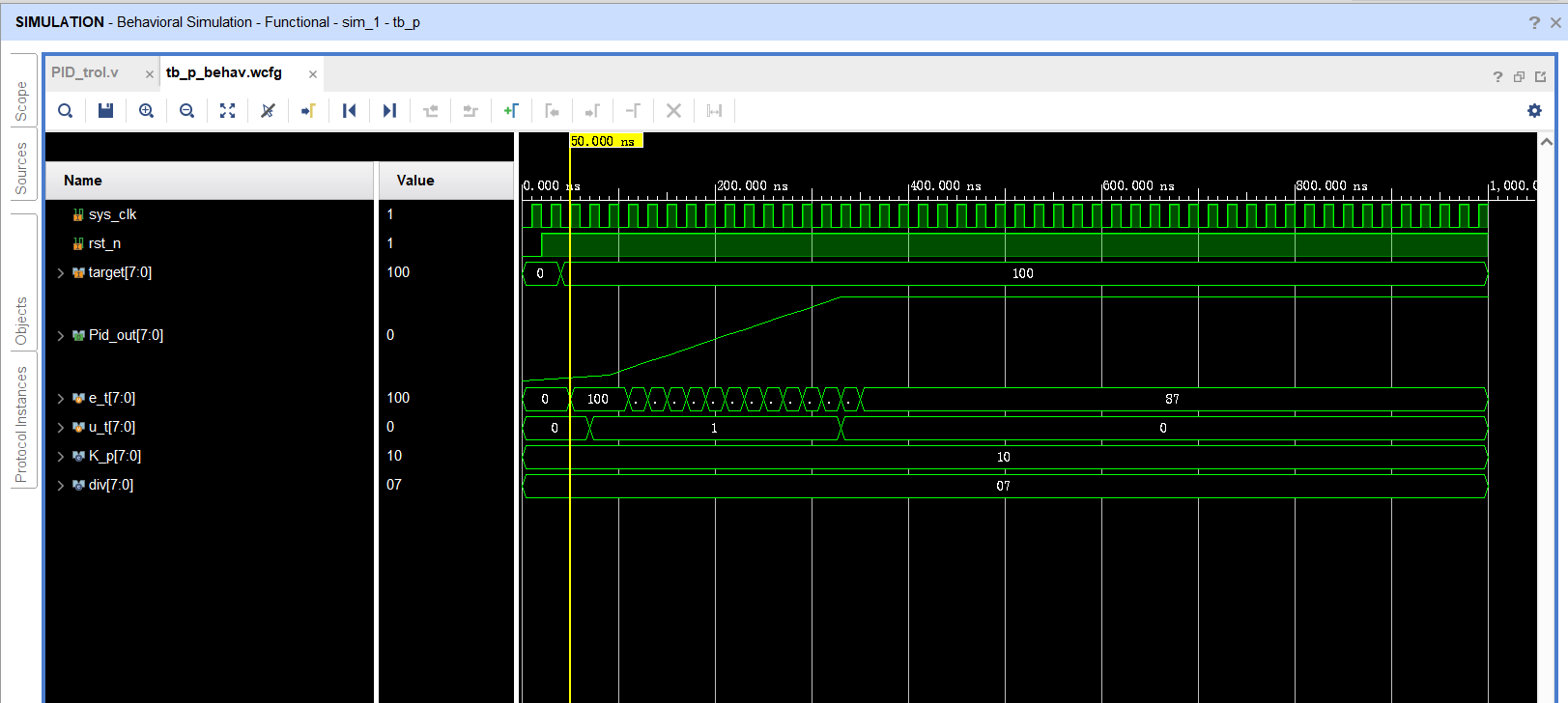

二、FPGA仿真验证

真实的K_p = K_p / 2^div

c

module PID_trol(

input sys_clk ,

input rst_n,

//signal

input [7:0] target,

output reg [7:0] Pid_out

);

reg [7:0] e_t;//目标值和现在值的差距

reg [7:0] u_t;//补偿值

parameter K_p = 8'd10;

parameter div = 8'd3;

always @(posedge sys_clk or negedge rst_n)begin

if(!rst_n)begin

e_t <= 8'd0;

end

else if(Pid_out < target)begin

e_t <= target - Pid_out;

end

else if(Pid_out >= target)begin

e_t <= Pid_out - target;

end

else begin

e_t <= e_t;

end

end

always @(posedge sys_clk or negedge rst_n)begin

if(!rst_n)begin

u_t <= 8'd0;

end

else begin

u_t <= (e_t * K_p )>>div;

end

end

always @(posedge sys_clk or negedge rst_n)begin

if(!rst_n)begin

Pid_out <= 8'd0;

end

else if(Pid_out < target)begin

Pid_out <= Pid_out + u_t;

end

else if(Pid_out >= target)begin

Pid_out <= Pid_out - u_t;

end

end

endmoduleKp=10/8=1.25

Kp=10/16=0.625

Kp=10/32=0.3125

Kp=10/64=0.157

Kp=10/128=0.0789

总结

这一篇只验证了PID中的比例系数P,其他都是0。