VCS使用教程 (Synopsys VCS Simulator Tutorial)

目录

- VCS使用教程 (Synopsys VCS Simulator Tutorial)

- 目录

- [1. VCS简介](#1. VCS简介)

- [1.1 什么是VCS?](#1.1 什么是VCS?)

- [1.2 VCS的特点和优势](#1.2 VCS的特点和优势)

- [1.2.1 技术优势](#1.2.1 技术优势)

- [1.2.2 与竞争产品对比](#1.2.2 与竞争产品对比)

- [1.3 VCS工作原理](#1.3 VCS工作原理)

- [1.3.1 编译型仿真vs解释型仿真](#1.3.1 编译型仿真vs解释型仿真)

- [1.3.2 VCS编译流程详解](#1.3.2 VCS编译流程详解)

- [1.4 VCS与其他仿真器对比](#1.4 VCS与其他仿真器对比)

- [1.4.1 性能基准测试](#1.4.1 性能基准测试)

- [1.4.2 应用场景推荐](#1.4.2 应用场景推荐)

- [2. VCS基础使用](#2. VCS基础使用)

- [2.1 基本编译流程](#2.1 基本编译流程)

- [2.1.1 编译流程图](#2.1.1 编译流程图)

- [2.1.2 基本命令格式](#2.1.2 基本命令格式)

- [2.2 常用编译选项](#2.2 常用编译选项)

- [2.2.1 基础编译选项](#2.2.1 基础编译选项)

- [2.2.2 调试相关选项](#2.2.2 调试相关选项)

- [2.2.3 性能优化选项](#2.2.3 性能优化选项)

- [2.2.4 文件和路径选项](#2.2.4 文件和路径选项)

- [2.3 常用仿真选项](#2.3 常用仿真选项)

- [2.3.1 基本仿真选项](#2.3.1 基本仿真选项)

- [2.3.2 运行控制选项](#2.3.2 运行控制选项)

- [2.3.3 调试和分析选项](#2.3.3 调试和分析选项)

- [2.4 文件管理与生成物](#2.4 文件管理与生成物)

- [2.1 基本编译流程](#2.1 基本编译流程)

- [3. VCS进阶功能](#3. VCS进阶功能)

- [3.1 SystemVerilog支持](#3.1 SystemVerilog支持)

- [3.2 UVM验证方法学](#3.2 UVM验证方法学)

- [3.3 覆盖率分析](#3.3 覆盖率分析)

- [3.4 断言验证](#3.4 断言验证)

- [4. 波形查看与调试](#4. 波形查看与调试)

- [4.1 波形文件格式详解](#4.1 波形文件格式详解)

- [4.2 DVE调试环境](#4.2 DVE调试环境)

- [4.3 Verdi调试平台](#4.3 Verdi调试平台)

- [4.4 调试技巧与最佳实践](#4.4 调试技巧与最佳实践)

- [4.5 iverilog与GTKWave](#4.5 iverilog与GTKWave)

- [5. 实战案例](#5. 实战案例)

- [5.1 简单组合逻辑验证](#5.1 简单组合逻辑验证)

- [5.1.1 RTL代码 (

adder.v)](#5.1.1 RTL代码 (adder.v)) - [5.1.2 Testbench代码 (

adder_tb.v)](#5.1.2 Testbench代码 (adder_tb.v)) - [5.1.3 仿真流程](#5.1.3 仿真流程)

- [5.1.1 RTL代码 (

- [5.2 时序逻辑与状态机验证](#5.2 时序逻辑与状态机验证)

- [5.2.1 RTL代码 (

fsm_demo.v)](#5.2.1 RTL代码 (fsm_demo.v)) - [5.2.2 Testbench代码 (

fsm_demo_tb.v)](#5.2.2 Testbench代码 (fsm_demo_tb.v)) - [5.2.3 仿真流程](#5.2.3 仿真流程)

- [5.2.1 RTL代码 (

- [5.3 复杂SoC模块验证](#5.3 复杂SoC模块验证)

- [5.4 回归测试脚本](#5.4 回归测试脚本)

- [5.1 简单组合逻辑验证](#5.1 简单组合逻辑验证)

- [6. 性能优化与最佳实践](#6. 性能优化与最佳实践)

- [6.1 编译优化](#6.1 编译优化)

- [6.2 仿真加速](#6.2 仿真加速)

- [6.3 内存管理](#6.3 内存管理)

- [6.4 多核并行](#6.4 多核并行)

- [7. 常见问题与解决方案](#7. 常见问题与解决方案)

- [7.1 编译错误](#7.1 编译错误)

- [7.1.1 常见编译错误及解决方案](#7.1.1 常见编译错误及解决方案)

- [7.1.2 编译优化建议](#7.1.2 编译优化建议)

- [7.2 仿真问题](#7.2 仿真问题)

- [7.3 License问题](#7.3 License问题)

- [7.4 性能问题](#7.4 性能问题)

- [7.1 编译错误](#7.1 编译错误)

- [8. 附录](#8. 附录)

- [8.1 VCS命令速查表](#8.1 VCS命令速查表)

- [8.2 环境变量参考](#8.2 环境变量参考)

- [8.3 资源链接](#8.3 资源链接)

- [8.4 CPU RTL最佳实践代码](#8.4 CPU RTL最佳实践代码)

1. VCS简介

1.1 什么是VCS?

VCS (Verilog Compiled Simulator) 是Synopsys公司开发的高性能、工业级Verilog/SystemVerilog仿真器。它采用编译型仿真技术,将HDL代码编译成优化的C代码,再编译成可执行文件,从而实现高速仿真。

主要特性:

- 🚀 高性能:编译型仿真,速度比解释型仿真器快10-100倍

- 🔧 全面支持:完整支持Verilog、SystemVerilog、VHDL、SystemC

- 🎯 验证方法学:内置UVM/OVM支持,完整的验证生态

- 🔍 调试能力:与Verdi/DVE深度集成,强大的调试分析功能

- 📊 覆盖率分析:全面的功能覆盖率、代码覆盖率、断言覆盖率

1.2 VCS的特点和优势

1.2.1 技术优势

编译型仿真流程:

HDL源码 → 解析分析 → 中间表示 → C代码生成 → 编译优化 → 可执行文件

↓ ↓ ↓ ↓ ↓ ↓

语法检查 语义分析 IR优化 代码生成 编译器优化 高速执行1.2.2 与竞争产品对比

| 特性对比 | VCS | QuestaSim | Xcelium | NC-Verilog |

|---|---|---|---|---|

| 仿真速度 | 🏆 最快 | 中等 | 快 | 中等 |

| 内存使用 | 🏆 优秀 | 良好 | 良好 | 一般 |

| 调试功能 | 🏆 Verdi集成 | 内置GUI | Indago | SimVision |

| 语言支持 | 🏆 最全面 | 全面 | 全面 | 基础 |

| 验证方法学 | 🏆 UVM原生支持 | UVM支持 | UVM支持 | 基础支持 |

| 市场占有率 | 🏆 最高 | 中等 | 中等 | 较低 |

1.3 VCS工作原理

1.3.1 编译型仿真vs解释型仿真

编译型仿真 (VCS模式):

优点:

✅ 仿真速度极快

✅ 内存使用效率高

✅ 支持大规模设计

✅ 优化程度高

缺点:

❌ 编译时间较长

❌ 调试相对复杂

❌ 代码修改需重新编译解释型仿真 (传统模式):

优点:

✅ 编译快速

✅ 调试直观

✅ 代码修改立即生效

缺点:

❌ 仿真速度慢

❌ 内存占用大

❌ 不适合大规模设计1.3.2 VCS编译流程详解

-

前端编译 (vlogan):

- 语法解析和语义分析

- 生成中间数据库文件

- 支持多种HDL语言混合编译

-

后端编译 (vcs):

- 链接和优化

- 生成C代码

- 调用系统C编译器

- 生成可执行仿真文件

-

仿真执行 (simv):

- 加载测试向量

- 执行仿真计算

- 生成波形和日志

1.4 VCS与其他仿真器对比

1.4.1 性能基准测试

| 测试项目 | VCS | QuestaSim | Xcelium | 说明 |

|---|---|---|---|---|

| 小规模设计 | 100% | 85% | 90% | 相对性能 |

| 中规模设计 | 100% | 70% | 80% | 1M gate级别 |

| 大规模设计 | 100% | 50% | 70% | 10M+ gate级别 |

| 编译时间 | 100% | 60% | 80% | 相对时间 |

| 内存使用 | 100% | 120% | 110% | 相对消耗 |

1.4.2 应用场景推荐

-

VCS适用场景:

- 大规模SoC验证

- 高性能要求的项目

- 需要完整UVM支持

- 回归测试和CI/CD

-

其他工具适用场景:

- QuestaSim:中小规模设计,教育培训

- Xcelium:Cadence生态,混合信号验证

- ModelSim:入门学习,简单项目

2. VCS基础使用

2.1 基本编译流程

VCS采用两阶段编译模式,提供了灵活性和高性能:

2.1.1 编译流程图

graph TD A[Verilog/SV源码] --> B[vlogan 前端编译] B --> C[生成数据库文件] C --> D[vcs 后端编译] D --> E[生成simv可执行文件] E --> F[./simv 仿真执行] F --> G[生成波形和日志]

2.1.2 基本命令格式

bash

# 方法1:一步编译(推荐用于简单项目)

vcs [编译选项] [源文件] -o [输出文件名]

# 方法2:两步编译(推荐用于复杂项目)

vlogan [编译选项] [源文件] # 前端编译

vcs [链接选项] [顶层模块] -o [输出文件名] # 后端编译

# 方法3:使用文件列表

vcs [编译选项] -f [文件列表] -o [输出文件名]2.2 常用编译选项

2.2.1 基础编译选项

| 选项 | 功能 | 示例 | 备注 |

|---|---|---|---|

-help |

显示帮助信息 | vcs -help |

查看所有可用选项 |

-full64 |

64位编译模式 | vcs -full64 |

推荐用于大型设计 |

-sverilog |

支持SystemVerilog | vcs -sverilog |

必需,用于SV语法 |

+v2k |

支持Verilog-2001 | vcs +v2k |

向后兼容 |

-timescale |

指定时间精度 | vcs -timescale=1ns/1ps |

仿真时间单位 |

-o <name> |

指定输出文件名 | vcs -o my_sim |

默认为simv |

2.2.2 调试相关选项

| 选项 | 功能 | 示例 | 说明 |

|---|---|---|---|

-debug_access+all |

完全调试访问 | vcs -debug_access+all |

允许查看所有信号 |

-debug_access+r |

只读调试访问 | vcs -debug_access+r |

只读模式,节省资源 |

-line |

启用行号调试 | vcs -line |

源码级调试 |

-lca |

生成覆盖率数据库 | vcs -lca |

用于覆盖率分析 |

-cm <type> |

覆盖率类型 | vcs -cm line+cond+fsm |

line/cond/fsm/tgl |

2.2.3 性能优化选项

| 选项 | 功能 | 示例 | 说明 |

|---|---|---|---|

-Mupdate |

增量编译 | vcs -Mupdate |

只编译修改的文件 |

-j<n> |

并行编译 | vcs -j8 |

使用8个CPU核心 |

-comp |

优化编译 | vcs -comp |

编译时优化 |

-no_save |

不保存中间文件 | vcs -no_save |

节省磁盘空间 |

-fast |

快速模式 | vcs -fast |

牺牲精度换取速度 |

2.2.4 文件和路径选项

| 选项 | 功能 | 示例 | 说明 |

|---|---|---|---|

-f <file> |

文件列表 | vcs -f filelist.f |

包含源文件路径 |

-v <file> |

库文件 | vcs -v my_lib.v |

单个库文件 |

-y <dir> |

库目录 | vcs -y ./lib |

库文件目录 |

+libext+<ext> |

库文件扩展名 | +libext+.v+.sv |

搜索文件类型 |

+incdir+<dir> |

include目录 | +incdir+./inc |

`include文件路径 |

+define+<macro> |

预定义宏 | +define+SIM_MODE |

编译时宏定义 |

2.3 常用仿真选项

2.3.1 基本仿真选项

| 选项 | 功能 | 示例 | 说明 |

|---|---|---|---|

-R |

编译后立即运行 | vcs -R test.v |

一步完成 |

-gui |

启动图形界面 | ./simv -gui |

DVE调试界面 |

-gui=dve |

指定DVE界面 | ./simv -gui=dve |

明确指定DVE |

-l <file> |

日志文件 | ./simv -l sim.log |

保存仿真日志 |

-s |

交互模式 | ./simv -s |

在时间0停止 |

2.3.2 运行控制选项

| 选项 | 功能 | 示例 | 说明 |

|---|---|---|---|

+vcs+stop+<time> |

指定停止时间 | ./simv +vcs+stop+1000 |

1000时间单位后停止 |

+vcs+max_cpu=<sec> |

CPU时间限制 | ./simv +vcs+max_cpu=3600 |

1小时CPU时间限制 |

+ntb_random_seed=<n> |

随机种子 | ./simv +ntb_random_seed=123 |

确定性随机序列 |

+vcs+lic_wait |

等待license | ./simv +vcs+lic_wait |

license不足时等待 |

2.3.3 调试和分析选项

| 选项 | 功能 | 示例 | 说明 |

|---|---|---|---|

-ucli |

启动UCLI | ./simv -ucli |

统一命令行界面 |

-vpd_file <file> |

VPD文件名 | ./simv -vpd_file sim.vpd |

指定波形文件 |

-cm_name <name> |

覆盖率名称 | ./simv -cm_name test1 |

覆盖率数据库名 |

-cm_dir <dir> |

覆盖率目录 | ./simv -cm_dir ./cov |

覆盖率存储路径 |

2.4 文件管理与生成物

当执行VCS编译命令后,会生成一系列文件和目录,理解它们有助于更好地管理项目。

-

simv:默认的仿真可执行文件。通过./simv来运行仿真。 -

simv.daidir/:VCS的中间数据库目录,包含了设计的层次化信息。 -

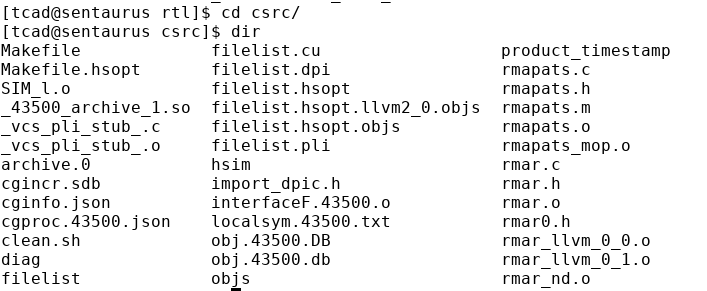

csrc/:存放VCS生成的C语言源码。VCS将Verilog/SV代码转换为C代码,然后使用系统C/C++编译器(如gcc/g++)来创建最终的可执行文件。 -

ucli.key:记录了VCS编译过程的详细信息,可用于后续的增量编译或调试。 -

日志文件 :通过在编译或仿真命令后加上

-l <filename>(例如-l compile.log或-l sim.log),可以将编译或仿真的日志信息保存到指定文件,便于回顾和问题定位。 -

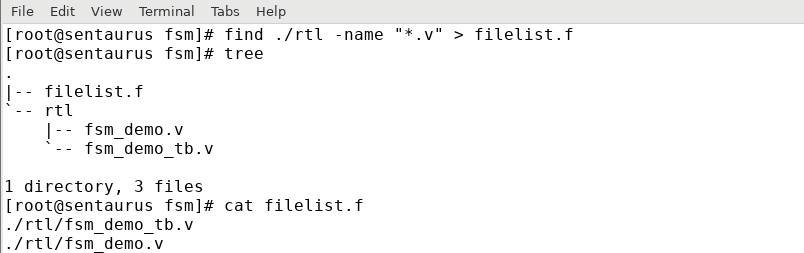

filelist.f:这通常是用户自己创建的文件列表,使用-f选项指定。它可以清晰地管理项目中的源文件,避免在命令行中输入大量文件名。一个常见的做法是使用find命令生成:bashfind ./rtl -name "*.v" > filelist.f find ./tb -name "*.sv" >> filelist.f

3. VCS进阶功能

VCS不仅仅是一个Verilog仿真器,它提供了强大的高级功能,以支持现代复杂的SoC验证流程。

3.1 SystemVerilog支持

VCS全面支持IEEE 1800-2017 SystemVerilog标准,这是现代验证的基础。

- 启用SystemVerilog :在编译时必须添加

-sverilog开关。 - 关键特性支持 :

- 类和对象 (Classes and Objects):支持面向对象的编程(OOP),用于构建可重用、可扩展的验证环境(如UVM)。

- 约束随机化 (Constrained-Random) :通过

rand和constraint关键字,可以生成复杂的随机激励,有效探索设计状态空间。 - 功能覆盖率 (Functional Coverage) :使用

covergroup和coverpoint,可以衡量验证是否覆盖了所有的设计功能点。 - 断言 (Assertions):支持SystemVerilog Assertions (SVA),用于在设计中嵌入属性检查,进行动态和形式化验证。

- 接口 (Interfaces):简化模块间的连接,特别是对于复杂的总线协议。

- 直接编程接口 (DPI):允许SystemVerilog与C/C++/SystemC代码高效交互。

3.2 UVM验证方法学

UVM (Universal Verification Methodology) 是业界标准的验证方法学,VCS对其提供原生支持。

- 原生支持 :VCS内置了UVM库,无需额外配置。只需在代码中

import uvm_pkg::*;并include "uvm_macros.svh"。 - UVM核心组件 :VCS高效地编译和仿真基于UVM的验证平台,包括:

uvm_test: 测试用例的顶层。uvm_env: 封装验证环境。uvm_agent: 封装协议的激励器、监视器和检查器。uvm_driver: 驱动信号到DUT。uvm_monitor: 监测DUT信号。uvm_scoreboard: 检查DUT的响应是否正确。

- UVM调试:结合DVE或Verdi,可以方便地调试UVM环境,例如查看UVM树状结构、追踪transaction流程、调试factory机制等。

3.3 覆盖率分析

覆盖率是衡量验证完备性的关键指标。VCS支持多种覆盖率类型。

-

启用覆盖率收集 :使用

-cm编译选项。bash# 收集行覆盖率(line)、条件覆盖率(cond)、有限状态机覆盖率(fsm)和翻转覆盖率(tgl) vcs -cm line+cond+fsm+tgl -f filelist.f -

覆盖率类型 :

- 代码覆盖率 (Code Coverage) :

line: 每行可执行代码是否被执行。cond:if-else、case语句的每个分支是否被走到。fsm: 状态机的每个状态和状态转移是否被访问。tgl: 每个bit信号是否经历了0->1和1->0的翻转。

- 功能覆盖率 (Functional Coverage) :通过SystemVerilog的

covergroup定义,衡量设计规格中的功能点是否被测试到。下面是一个针对5.2节FSM例子的功能覆盖率代码示例,可以将其放在Testbench中:

systemverilog// Functional coverage for the FSM covergroup FsmCoverage @(posedge clk); // Coverpoint for the state variable cp_state: coverpoint u_fsm_demo.present_state { bins idle = {fsm_demo::IDLE}; bins s1 = {fsm_demo::S1}; bins s2 = {fsm_demo::S2}; bins s3 = {fsm_demo::S3}; bins s4 = {fsm_demo::S4}; } // Coverpoint for state transitions cp_transition: cross cp_state, cp_state { // Ignore transitions to the same state ignore bins self_transition = (s) with (s.cp_state == s.cp_state'); } endgroup // Instantiate the covergroup initial begin FsmCoverage cov = new(); cov.sample(); end- 断言覆盖率 (Assertion Coverage):衡量SVA断言被触发、成功和失败的次数。

- 代码覆盖率 (Code Coverage) :

-

管理和查看 :

-cm_dir <directory>:指定存放覆盖率数据库的目录。-cm_name <name>:为当次仿真产生的覆盖率数据命名。- 结果合并与分析:多次回归测试产生的覆盖率数据库可以被合并(merge),并在DVE或Verdi中进行可视化分析,生成报告。

3.4 断言验证

断言是描述设计应有行为的属性,对于协议检查和错误定位非常有效。

- 启用断言 :在编译时使用

-sverilog即可,VCS会自动识别并处理SVA。 - 断言的作用 :

- 动态仿真:在仿真过程中,断言会实时检查设计行为是否符合预期,一旦违背立即报错,精确定位问题。

- 形式化验证:断言可以被形式化验证工具(如Synopsys VC Formal)使用,穷尽所有可能来证明属性的正确性。

- SVA示例:下面是一个针对5.2节FSM例子的SVA代码,可以放在FSM模块内部,用于检查复位逻辑。

systemverilog

// Assertion to check that after reset, state goes to IDLE

property p_reset_to_idle;

@(posedge clk) disable iff (!rst_n)

$rose(rst_n) |=> (present_state == IDLE);

endproperty

a_reset_to_idle: assert property (p_reset_to_idle) else $error("Reset sequence failed: state is not IDLE.");- 调试:在DVE或Verdi中,可以查看断言的成功/失败情况,并追溯到导致失败的波形和代码位置。

4. 波形查看与调试

4.1 波形文件格式详解

波形文件是数字电路仿真和调试的关键,不同的格式有不同的特点和适用场景。

-

VCD (Value Change Dump)

-

特点:ASCII格式,通用性好,几乎所有波形查看工具都支持。但文件体积巨大,读写速度慢。

-

生成方法 :在Testbench中添加系统任务。

veriloginitial begin $dumpfile("my_design.vcd"); $dumpvars(0, top_module_name); // 0表示dump所有层级 end

-

-

VPD (Verilog Procedural Dump)

-

特点:Synopsys自家的二进制压缩格式,文件体积比VCD小很多,读写速度快。是VCS/DVE环境下的常用格式。

-

生成方法 :在Testbench中添加

$vcdpluson;系统任务,并在编译时开启调试选项。veriloginitial begin $vcdpluson(); end编译后,仿真会自动生成

vcdplus.vpd文件。

-

-

FSDB (Fast Signal Database)

-

特点:Verdi(原Novas)的波形格式,同样是二进制压缩格式,压缩率高,加载速度快,支持更丰富的调试特性。

-

生成方法 :需要Verdi的环境支持,并在Testbench中调用特定系统任务。

veriloginitial begin $fsdbDumpfile("my_design.fsdb"); $fsdbDumpvars(0, "top_module_name", "+all"); end

-

-

WLF (Wave Log File)

- 特点:Mentor Graphics (Siemens) QuestaSim/ModelSim使用的默认波形格式,也是一种高效的二进制格式。

- 生成方法:在QuestaSim/ModelSim环境中通过命令或GUI配置生成。

| 格式 | 优点 | 缺点 | 常用工具 |

|---|---|---|---|

| VCD | 通用性强,可读 | 文件大,速度慢 | GTKWave, Verdi, DVE |

| VPD | 压缩率高,VCS原生 | Synopsys生态 | DVE, Verdi |

| FSDB | 压缩率极高,功能强 | Verdi生态 | Verdi |

| WLF | 性能好 | Mentor生态 | QuestaSim, ModelSim |

4.2 DVE调试环境

DVE (Discovery Visual Environment) 是VCS自带的图形化调试工具。

-

启动DVE :

bash# 编译时需要加入调试选项 -debug_access+all vcs -full64 -debug_access+all -f filelist.f # 仿真结束后启动DVE查看波形 dve -vpd vcdplus.vpd & -

基本操作 :

- 信号添加:在左侧的设计浏览器中找到信号,右键点击 "Add to Waves"。

- 波形缩放:使用工具栏的放大/缩小按钮。

- 光标定位:在波形窗口点击,可以查看该时间点的信号值。

- 源码关联:在波形窗口右键点击信号,可以选择 "Go to Source Code"。

4.3 Verdi调试平台

Verdi是比DVE更强大的调试平台,尤其在协议分析、性能分析和根本原因分析(RCA)方面表现出色。通常需要单独的License。

4.4 调试技巧与最佳实践

高效的调试是缩短验证周期的关键。以下是一些在DVE/Verdi中行之有效的技巧:

-

分而治之:当遇到问题时,首先将其定位到具体的模块。通过查看模块的输入输出波形,判断问题是在模块内部还是外部。

-

信号追溯 (Signal Tracing) :

- 驱动追溯 (Trace Drivers / Fan-in):当发现一个信号的值不正确时,使用此功能可以快速找到所有驱动该信号的源头,从而定位赋值逻辑。

- 负载追溯 (Trace Loads / Fan-out):查看一个信号被哪些逻辑使用,有助于理解其影响范围。

-

利用断言:在关键位置和协议接口处编写SVA断言。断言失败能提供精确的时间点和违例类型,是定位bug的利器。

-

增量式Dump波形 :对于长时间仿真,一直dump波形会产生巨大的文件并拖慢仿真。可以先进行一次不dump波形的仿真,如果出现错误,再根据错误报告的时间点,重新进行一次只dump错误时间点前后一小段时间窗口的仿真。

verilog// Example of timed waveform dumping initial begin #10000; // Wait until the interesting time $vcdpluson(1, top.dut); // Dump specific module from now on #5000; $vcdplusoff(); $finish; end -

利用日志文件 :在Testbench中,使用

$display,$monitor,$info,$warning,$error等系统任务打印关键信息、变量值和仿真进度。结构化的日志是事后分析问题的重要线索。 -

对比波形 (Waveform Compare):当修改了RTL代码后,可以使用Verdi等工具的波形对比功能,将新旧两次仿真的波形进行比较,快速找出行为差异点。这对于验证代码重构或bug修复非常有用。

-

理解

X态的根源 :X态(未知态)是调试中的常见问题。出现X态时,应逆向追溯其来源,通常原因包括:- 未复位的寄存器。

- 多个驱动源冲突(multiple drivers)。

- 读取内存时地址越界。

- 时序违例(在门级仿真中)。

4.5 iverilog与GTKWave

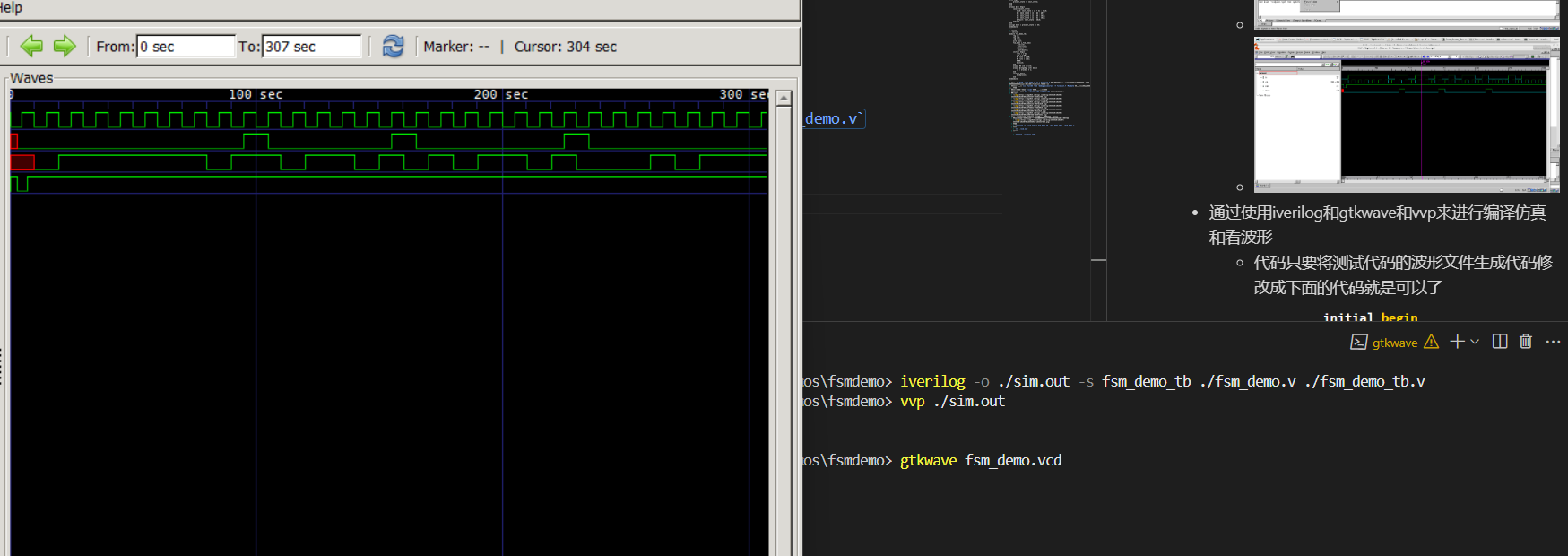

对于学习和小型项目,开源工具Icarus Verilog (iverilog) 和 GTKWave 是一个很好的选择。

-

编译 :

bashiverilog -o sim.out -s fsm_demo_tb fsm_demo_tb.v fsm_demo.v -

仿真 :

bashvvp ./sim.out -

查看波形 :

bashgtkwave waveform.vcd

5. 实战案例

5.1 简单组合逻辑验证

本节将演示如何验证一个简单的4位全加器。

5.1.1 RTL代码 (adder.v)

verilog

module adder(

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] sum,

output cout

);

assign {cout, sum} = a + b + cin;

endmodule5.1.2 Testbench代码 (adder_tb.v)

verilog

module adder_tb;

reg [3:0] a;

reg [3:0] b;

reg cin;

wire [3:0] sum;

wire cout;

adder u_adder(

.a(a),

.b(b),

.cin(cin),

.sum(sum),

.cout(cout)

);

initial begin

// Enable VPD waveform dumping

$vcdpluson;

// Test case 1

a = 4'h1; b = 4'h2; cin = 1'b0; #10;

// Test case 2

a = 4'hF; b = 4'h1; cin = 1'b0; #10;

// Test case 3

a = 4'h9; b = 4'h9; cin = 1'b1; #10;

// Add more random tests

repeat(5) begin

{a, b, cin} = $random;

#10;

end

$finish;

end

initial begin

// Monitor the signals

$monitor("Time=%0t, a=%h, b=%h, cin=%b -> cout=%b, sum=%h", $time, a, b, cin, cout, sum);

end

endmodule5.1.3 仿真流程

-

创建文件列表

filelist.f:adder.v adder_tb.v -

编译 :

bashvcs -full64 +v2k -debug_access+all -f filelist.f -l compile.log -

运行仿真 :

bash./simv -l sim.log你将在

sim.log文件中看到$monitor打印的输出。 -

查看波形 :

bashdve -vpd vcdplus.vpd &

5.2 时序逻辑与状态机验证

本案例将演示如何使用VCS验证一个检测"1101"序列的状态机(FSM)。

5.2.1 RTL代码 (fsm_demo.v)

verilog

// detect 1101

module fsm_demo(

input wire in,

input wire clk,

input wire rstn,

output wire dout);

localparam IDLE = 5'b00001, S1 = 5'b00010, S2 = 5'b00100, S3 = 5'b01000, S4 = 5'b10000;

reg [4:0] present_state;

reg [4:0] next_state;

always @(posedge clk or negedge rstn) begin

if(~rstn) begin

present_state <= IDLE;

end

else begin

present_state <= next_state;

end

end

always @(*) begin

case(present_state)

IDLE: next_state = in ? S1 : IDLE; // a 1 is received

S1: next_state = in ? S2 : IDLE; // a 1 is received

S2: next_state = in ? S2 : S3; // a 0 is received

S3: next_state = in ? S4 : IDLE; // a 1 is received

S4: next_state = in ? S1 : IDLE; // sequence detected, ready for next '1'

default: next_state = IDLE;

endcase

end

assign dout = (present_state == S4); // output is high when in S4 state

endmodule5.2.2 Testbench代码 (fsm_demo_tb.v)

verilog

module fsm_demo_tb;

reg in;

reg clk;

reg rstn;

wire dout;

fsm_demo u_fsm_demo(

.clk(clk),

.rstn(rstn),

.in(in),

.dout(dout)

);

initial begin

rstn = 1'b1;

clk = 1'b0;

#3 rstn = 1'b0;

#4 rstn = 1'b1;

#300 $finish;

end

always #5 clk = ~clk;

always @(negedge clk) begin

in <= $random % 2;

end

initial begin

// Enable VPD waveform dumping

$vcdpluson;

end

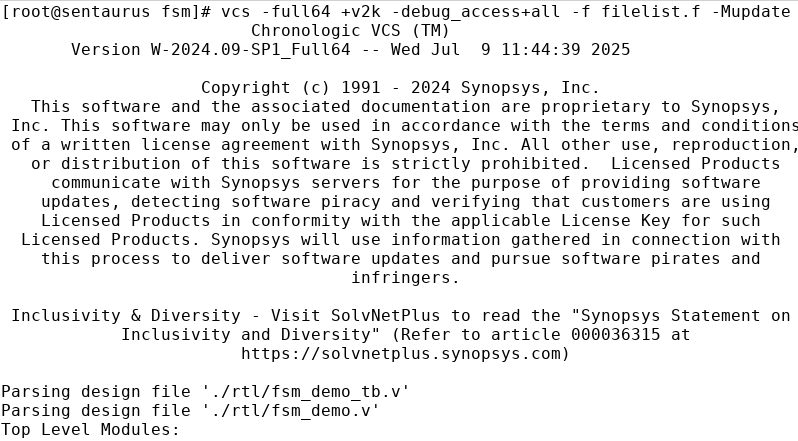

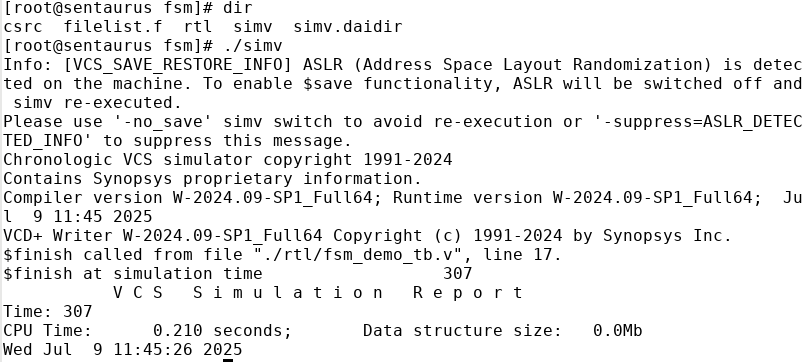

endmodule5.2.3 仿真流程

-

创建文件列表

filelist.f:fsm_demo.v fsm_demo_tb.v -

编译: 使用VCS编译RTL和Testbench。

bash# -Mupdate: 增量编译 # -debug_access+all: 开启所有调试功能,用于生成波形 vcs -full64 +v2k -debug_access+all -f filelist.f -Mupdate -l compile.log

-

运行仿真 : 执行生成的

simv文件。bash./simv -l sim.log

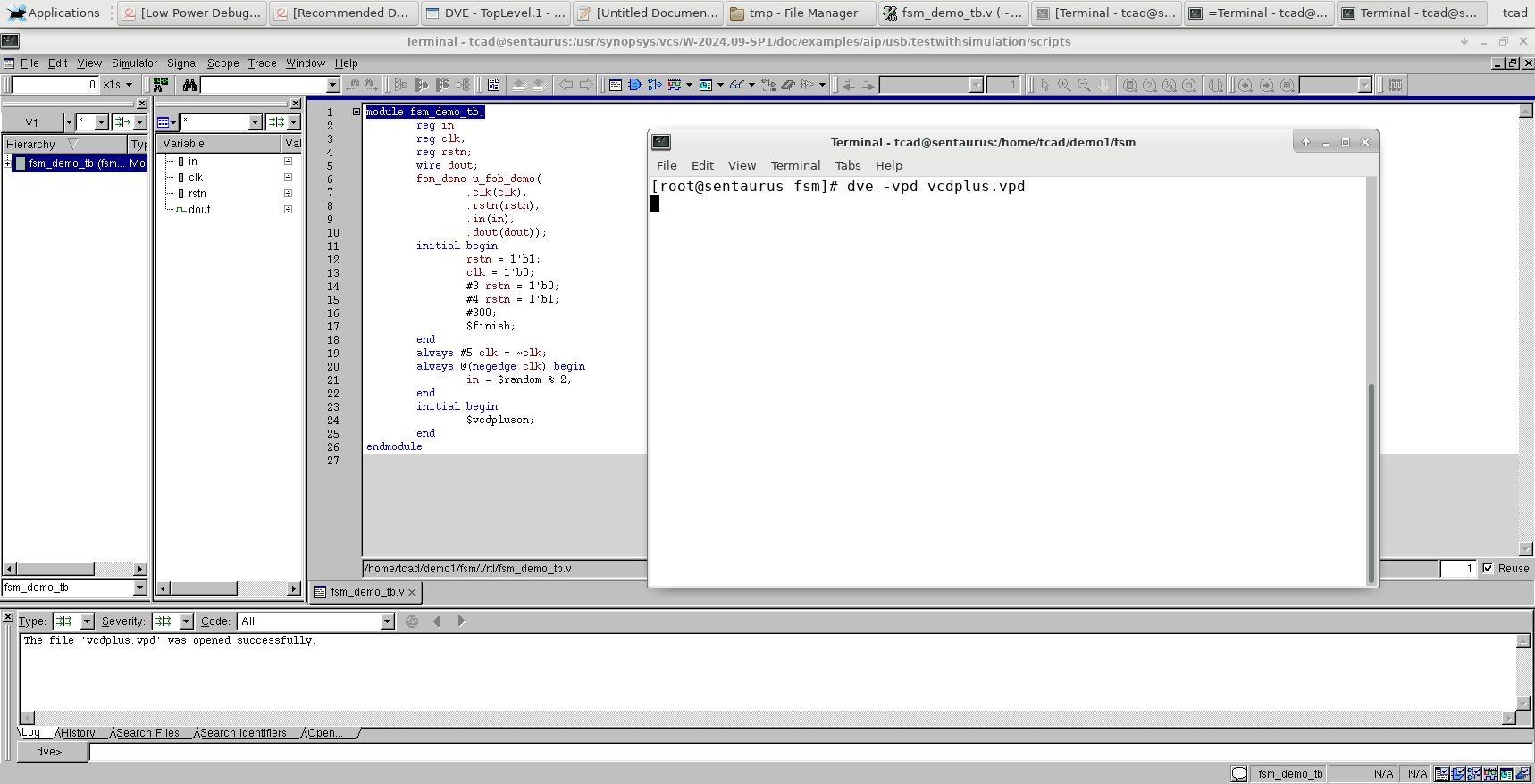

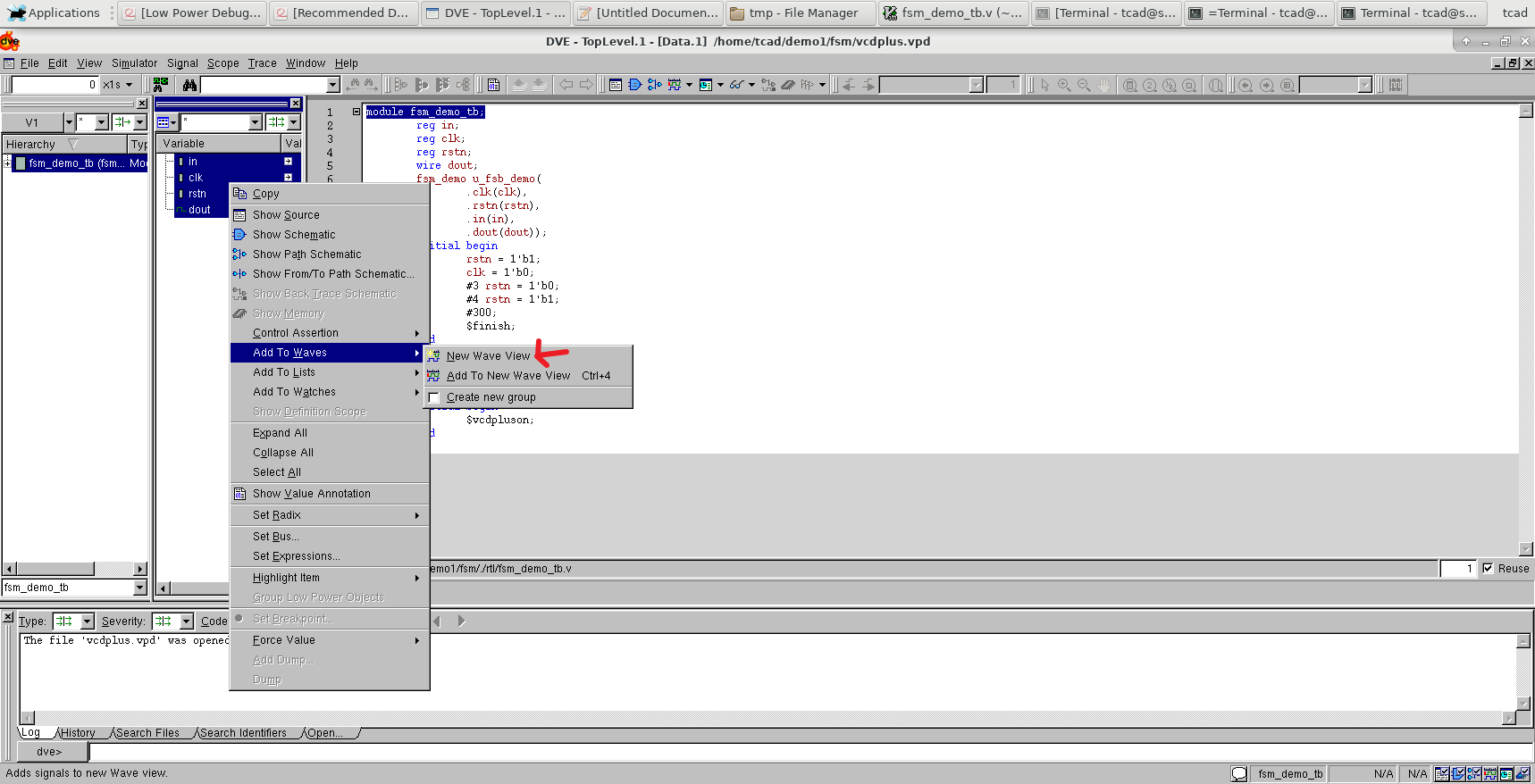

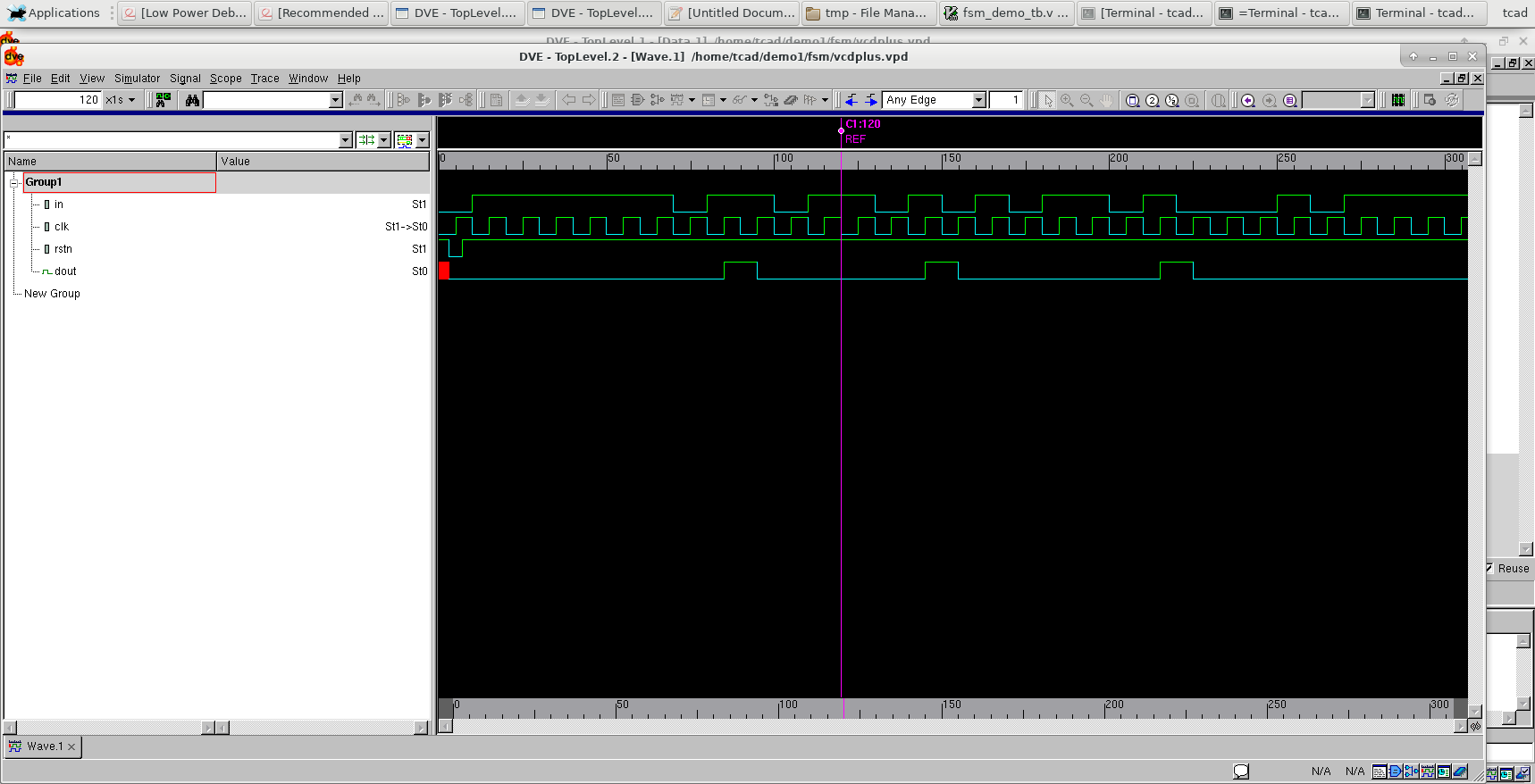

-

查看波形 : 使用DVE打开生成的

vcdplus.vpd波形文件。bashdve -vpd vcdplus.vpd &

在DVE中,将

in,clk,rstn,present_state,dout等信号添加到波形窗口,可以看到状态机的跳转和输出结果。

5.3 复杂SoC模块验证

在复杂的SoC(System on Chip)项目中,验证通常围绕标准的总线协议(如AXI, AHB, APB)和关键IP(如DMA控制器、中断控制器)展开。这类验证通常会用到UVM方法学。

一个典型的验证场景可能包括:

- DUT: 一个AXI-Lite接口的寄存器模块。

- 验证平台 :

- 使用UVM构建一个AXI-Lite Master Agent来产生读写操作。

- 一个Scoreboard来比对写入和读出的数据是否一致。

- 使用约束随机化来生成各种地址和数据。

- 使用功能覆盖率来确保所有寄存器都被访问过,且所有比特位都被测试过。

由于代码量较大,这里只提供一个框架思路,具体的实现可以参考UVM相关的教程和开源项目。

5.4 回归测试脚本

在项目开发过程中,代码会频繁变更。为了确保新修改没有破坏原有功能,需要进行回归测试。手动执行所有测试用例是低效且易错的,因此需要自动化脚本。Makefile 是一个常用的工具。

下面是一个简单的 Makefile 示例,用于管理编译和运行多个测试用例。

makefile

# Makefile for VCS Regression

# --- Tool Setup ---

VCS = vcs

SIMV = ./simv

DVE = dve

# --- VCS Flags ---

VCS_FLAGS = -full64 -sverilog +v2k -debug_access+all

COMP_LOG = compile.log

SIM_LOG_DIR = logs

COV_DIR = coverage

# --- Source Files ---

RTL_FILES = adder.v fsm_demo.v

TB_ADDER = adder_tb.v

TB_FSM = fsm_demo_tb.v

# --- Tests ---

TESTS = test_adder test_fsm

# --- Default Target ---

all: $(TESTS)

# --- Compilation Targets ---

simv_adder:

$(VCS) $(VCS_FLAGS) $(RTL_FILES) $(TB_ADDER) -o simv_adder -l $(COMP_LOG)

simv_fsm:

$(VCS) $(VCS_FLAGS) $(RTL_FILES) $(TB_FSM) -o simv_fsm -l $(COMP_LOG)

# --- Simulation Targets ---

test_adder: simv_adder

@echo "Running Adder Test..."

./simv_adder -l $(SIM_LOG_DIR)/adder.log

test_fsm: simv_fsm

@echo "Running FSM Test..."

./simv_fsm -l $(SIM_LOG_DIR)/fsm.log

# --- Housekeeping ---

run: all

setup:

mkdir -p $(SIM_LOG_DIR) $(COV_DIR)

clean:

rm -rf csrc simv* *.daidir ucli.key *.vpd $(COMP_LOG) $(SIM_LOG_DIR) $(COV_DIR)

.PHONY: all clean setup run $(TESTS)使用方法:

make setup: 创建日志和覆盖率目录。make all或make run: 运行所有测试。make test_adder: 只运行加法器测试。make clean: 清理所有生成的文件。

6. 性能优化与最佳实践

6.1 编译优化

- 增量编译 (

-Mupdate): 对于大型项目,每次只重新编译已修改的文件及其依赖项,可以显著减少编译时间。 - 并行编译 (

-j<n>) : 在多核CPU上,使用-j选项(如-j8)可以并行执行编译任务,加快编译速度。 - 使用文件列表 (

-f): 将所有源文件路径整理到文件列表(filelist)中,使编译命令更简洁,也便于脚本化管理。 - 优化级别: VCS提供不同的优化级别,但在开发初期,建议关闭或使用较低的优化,以保留完整的调试信息。

6.2 仿真加速

- 选择正确的波形格式: 避免在大型回归测试中使用VCD,优先选择VPD或FSDB。在不需要波形时,完全关闭波形dump可以获得最大加速。

- 门级仿真优化 : 对于门级网表仿真,使用

+vcs+vcdpluson+fsdb等选项可以优化性能。 - 避免过度调试 :

-debug_access+all会带来性能开销。在不需要深入调试时,可以使用-debug_access+r(只读)或更细粒度的调试选项。 - 使用VCS Native Testbench (NTB): 对于算法密集型或需要与C/C++/SystemC交互的Testbench,使用NTB可以获得比纯Verilog/SV更高的性能。

6.3 内存管理

- 64位模式 (

-full64): 对于超过2GB内存需求的设计,必须使用64位模式进行编译和仿真。 - 合理dump信号 : 不要dump所有信号,特别是对于大型设计。只dump调试必需的模块和信号。可以使用

$vcdplusbop和$vcdpluson的参数来精确控制dump范围。 - 分段dump: 对于长时间仿真,可以分段生成波形文件,避免单个文件过大。

6.4 多核并行

- VCS支持在仿真期间利用多核CPU进行并行计算,特别是对于事件驱动的仿真。相关选项如

-parallel可能需要特定配置和设计风格才能发挥最大效用。

7. 常见问题与解决方案

7.1 编译错误

7.1.1 常见编译错误及解决方案

| 错误信息 | 可能原因 | 解决方案 |

|---|---|---|

vcs: command not found |

VCS未安装或未添加到PATH | 确认VCS已安装,并在终端中运行 echo $PATH 检查VCS路径是否在其中 |

No such file or directory |

源文件或库文件路径错误 | 检查文件路径是否正确,使用绝对路径或确保相对路径正确 |

syntax error |

Verilog/SystemVerilog语法错误 | 检查代码语法,确保符合Verilog/SystemVerilog标准 |

undefined reference |

未定义的模块或信号 | 检查模块和信号的定义,确保在编译时包含所有相关文件 |

license error |

License问题 | 确认已正确安装并配置License,使用 lmstat -a -c <port>@<server> 检查License状态 |

7.1.2 编译优化建议

- 增量编译 : 使用

-Mupdate选项,只编译修改过的文件,节省编译时间。 - 并行编译 : 利用多核CPU,使用

-j选项进行并行编译,如-j8。 - 合理使用优化选项: 根据需要选择合适的优化级别,开发阶段建议使用较低优化以便于调试。

7.2 仿真问题

| 问题描述 | 可能原因 | 解决方案 |

|---|---|---|

| 仿真挂起 (hang) | 1. 零延迟循环 (zero-delay loop)。 2. Testbench激励未正常结束。 3. 等待一个永远不会发生的事件。 | 1. 检查代码中 always @(*) 或 assign 是否存在组合逻辑环路。 2. 确保Testbench中有 $finish,并且所有激励都能在预期时间内完成。 3. 使用调试器检查程序挂在何处,分析事件触发条件。 |

| 结果不符合预期 | 1. RTL逻辑错误。 2. Testbench激励错误。 3. 时序问题(setup/hold violation)。 4. 未初始化的寄存器。 | 1. 使用DVE/Verdi单步调试,检查信号值。 2. 检查激励时序和数据是否正确。 3. 对于门级仿真,检查时序报告。 4. 确保所有寄存器都有正确的复位逻辑。 |

X态传播 |

1. 信号未初始化。 2. 多驱动源冲突。 3. 读取内存时地址越界。 4. 时序违例(在门级仿真中)。 | 1. 检查复位逻辑,确保所有reg都被初始化。 2. 检查是否有多个assign或always块驱动同一个wire。 3. 在波形中查看信号变化和时钟边沿的关系。 |

7.3 License问题

| 问题描述 | 可能原因 | 解决方案 |

|---|---|---|

| 无法获取License | 1. License服务器未运行。 2. 网络不通或防火墙阻挡。 3. License已过期或被占用。 | 1. 联系管理员确认License服务器状态。 2. ping <server_name> 检查网络连接。 3. 使用 lmstat 命令检查License使用情况。添加 +vcs+lic_wait 仿真选项可以在没有可用license时排队等待。 |

| 特定功能License失败 | 例如,无法使用覆盖率或UVM功能。 | 确认你拥有的License包含了VCS-MX或支持特定功能的套件。 |

7.4 性能问题

| 问题描述 | 可能原因 | 解决方案 |

|---|---|---|

| 仿真速度慢 | 1. Dump了过多的波形信号。 2. 设计规模巨大。 3. Testbench中有大量计算或文件I/O。 | 1. 减少$dumpvars的范围,或使用VPD/FSDB代替VCD。 2. 使用性能优化选项,如门级仿真加速。 3. 将Testbench中的复杂计算移到DPI-C或C++模型中。 |

| 内存占用过高 | 1. 设计规模大。 2. 波形文件过大。 3. 编译时未用64位模式。 | 1. 必须使用 -full64 模式。 2. 限制波形dump的深度和范围,或分段dump波形。 3. 检查是否有数据结构在仿真中无限增长。 |

8. 附录

8.1 VCS命令速查表

| 命令 | 功能 | 示例 |

|---|---|---|

vcs |

编译命令 | vcs -full64 -sverilog -debug_access+all -f filelist.f |

./simv |

运行仿真 | ./simv -l sim.log |

dve |

启动DVE调试 | dve -vpd vcdplus.vpd & |

gtkwave |

启动GTKWave | gtkwave waveform.vcd |

iverilog |

Icarus Verilog编译 | iverilog -o sim.out -s fsm_demo_tb fsm_demo_tb.v fsm_demo.v |

vvp |

运行Icarus Verilog仿真 | vvp ./sim.out |

8.2 环境变量参考

| 变量 | 功能 | 示例 |

|---|---|---|

PATH |

可执行文件搜索路径 | /usr/local/bin:/usr/bin:/bin |

LD_LIBRARY_PATH |

动态链接库搜索路径 | /usr/local/lib:/usr/lib |

VCS_HOME |

VCS安装路径 | /opt/synopsys/vcs |

DVE_HOME |

DVE安装路径 | /opt/synopsys/dve |

VERDI_HOME |

Verdi安装路径 | /opt/synopsys/verdi |

8.3 资源链接

8.4 CPU RTL最佳实践代码

下面是一个简化的RISC-V单周期CPU核心的RTL代码示例,用于演示结构化和可读性强的代码风格。这个示例包含指令获取、解码和执行的基本逻辑,并支持RV32I指令集的子集。

verilog

// A simple single-cycle RISC-V CPU core

// Supports a subset of RV32I: LUI, AUIPC, JAL, JALR, BEQ, BNE, ADDI, ADD, SUB, etc.

module mini_rv32i_core (

input wire clk,

input wire rst_n,

// Instruction Memory Interface

output wire [31:0] imem_addr,

input wire [31:0] imem_rdata,

// Data Memory Interface (simplified for this example)

output wire [31:0] dmem_addr,

output wire [31:0] dmem_wdata,

output wire [3:0] dmem_we,

input wire [31:0] dmem_rdata

);

// Program Counter

reg [31:0] pc;

wire [31:0] pc_next;

wire [31:0] pc_plus_4 = pc + 32'd4;

// Instruction Fetch

assign imem_addr = pc;

wire [31:0] instr = imem_rdata;

// Instruction Decode

wire [6:0] opcode = instr[6:0];

wire [2:0] funct3 = instr[14:12];

wire [6:0] funct7 = instr[31:25];

wire [4:0] rd = instr[11:7];

wire [4:0] rs1 = instr[19:15];

wire [4:0] rs2 = instr[24:20];

// Immediate Generation

wire [31:0] imm_i = {{21{instr[31]}}, instr[30:20]};

wire [31:0] imm_s = {{21{instr[31]}}, instr[30:25], instr[11:7]};

wire [31:0] imm_b = {{20{instr[31]}}, instr[7], instr[30:25], instr[11:8], 1'b0};

wire [31:0] imm_u = {instr[31:12], 12'b0};

wire [31:0] imm_j = {{12{instr[31]}}, instr[19:12], instr[20], instr[30:21], 1'b0};

// Register File

reg [31:0] reg_file [0:31];

wire [31:0] rs1_data = (rs1 == 5'b0) ? 32'b0 : reg_file[rs1];

wire [31:0] rs2_data = (rs2 == 5'b0) ? 32'b0 : reg_file[rs2];

wire [31:0] wb_data;

wire reg_we;

integer i;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

for (i = 0; i < 32; i = i + 1) begin

reg_file[i] <= 32'b0;

end

end else if (reg_we && rd != 5'b0) begin

reg_file[rd] <= wb_data;

end

end

// Control Signals (simplified)

wire is_jal = (opcode == 7'b1101111);

wire is_jalr = (opcode == 7'b1100111);

wire is_branch= (opcode == 7'b1100011);

wire is_load = (opcode == 7'b0000011);

wire is_store = (opcode == 7'b0100011);

wire is_r_type= (opcode == 7'b0110011);

wire is_i_type= (opcode == 7'b0010011);

assign reg_we = is_r_type | is_i_type | is_load | is_jal | is_jalr;

// ALU

// ... A complete ALU implementation would be here ...

wire [31:0] alu_result;

// This is a placeholder for ALU logic

assign alu_result = (is_r_type && funct3 == 3'b000) ? (rs1_data + rs2_data) : // ADD

(is_i_type && funct3 == 3'b000) ? (rs1_data + imm_i) : // ADDI

pc_plus_4; // Default for JAL/JALR

// Branch Condition

wire branch_taken = (is_branch) &&

((funct3 == 3'b000 & (rs1_data == rs2_data)) | // BEQ

(funct3 == 3'b001 & (rs1_data != rs2_data))); // BNE

// PC Next Logic

assign pc_next = branch_taken ? (pc + imm_b) :

is_jal ? (pc + imm_j) :

is_jalr ? ((rs1_data + imm_i) & ~32'h1) :

pc_plus_4;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

pc <= 32'h80000000; // Typical reset vector

end else begin

pc <= pc_next;

end

end

// Writeback Logic

assign wb_data = is_load ? dmem_rdata : alu_result;

// Data memory signals

assign dmem_addr = rs1_data + imm_s; // Simplified address for load/store

assign dmem_wdata = rs2_data;

assign dmem_we = {4{is_store}}; // Simplified, assumes 32-bit store

endmodule