一、 概述

经过前几个章节的介绍,关于DDS配置和用法已经了解,并可以通过aclken来控制何时输出波形,在本章节,我们使用两个通道同时储存两种波形,由于每次突发只能传输256个数据,那么每个通道传输10次写突发,共2560*2个数据,这样将这5120个数据存储进DDR4中。

二、 存储波形数据

使用通道0和通道1向DDR4中写入波形数据,,由interconnect来分配通道的使用权。其中需要考虑的是何时产生写开始,合理分配写地址。因为只截取5120个数据,不需要考虑写突发长度,每次突发长度都为256。

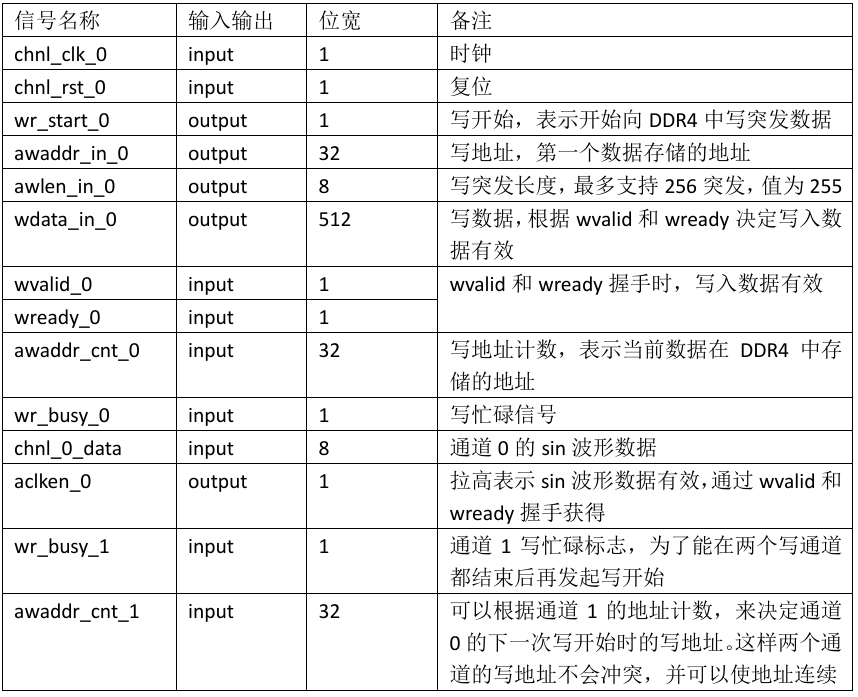

通道0接口列表:

产生写开始信号:

先定义写开始信号,第一次的写开始信号可以由计数器定时产生,后面的写开始需要等待通道0和通道1全都空闲时再发起。共发起10次。

always @(posedge chnl_clk_0) begin

if (chnl_rst_0) begin

wr_start_0_cnt <= 0;

end

else if (wr_start_0) begin

wr_start_0_cnt <= wr_start_0_cnt + 1;

end

end

always @(posedge chnl_clk_0) begin

if (chnl_rst_0) begin

clk_cnt <= 0;

end

else if (clk_cnt <= 'd999) begin

clk_cnt <= clk_cnt + 1;

end

end

always @(posedge chnl_clk_0) begin

wr_busy_0_r <= wr_busy_0;

end

always @(posedge chnl_clk_0) begin

if (chnl_rst_0) begin

wr_idle_flag_0 <= 0;

end

else if (wr_idle_flag_0 == 1 && wr_busy_1 == 0) begin

wr_idle_flag_0 <= 0;

end

else if (wr_busy_0 == 0 && wr_busy_0_r == 1) begin

wr_idle_flag_0 <= 1;

end

end

always @(posedge chnl_clk_0) begin

if (chnl_rst_0) begin

wr_start_0 <= 0;

end

else if (wr_idle_flag_0 == 1 && wr_busy_1 == 0 && wr_start_0_cnt <= 'd9) begin

wr_start_0 <= 1;

end

else if (clk_cnt == 'd990) begin

wr_start_0 <= 1;

end

else begin

wr_start_0 <= 0;

end

end

在写开始有效的同时,产生写地址和写突发长度,对于写突发长度,固定为255。对于写地址,因为本次的写开始为通道0和通道1全部突发结束后再产生的写开始信号,在两通道同时产生写开始时,验证过interconnect会先写通道0,再写通道1。所以在这里使用通道1的地址计数作为写地址。这样就可以将DDR4的地址连续写入数据。

always @(posedge chnl_clk_0) begin

if (chnl_rst_0) begin

awaddr_in_0 <= 0;

end

else if (wr_idle_flag_0 == 1 && wr_busy_1 == 0 && wr_start_0_cnt <= 'd9) begin

awaddr_in_0 <= awaddr_cnt_1;

end

else if (clk_cnt == 'd990) begin

awaddr_in_0 <= 0;

end

else begin

awaddr_in_0 <= 0;

end

end

always @(posedge chnl_clk_0) begin

if (chnl_rst_0) begin

awlen_in_0 <= 0;

end

else if (wr_idle_flag_0 == 1 && wr_busy_1 == 0 && wr_start_0_cnt <= 'd9) begin

awlen_in_0 <= 'd255;

end

else if (clk_cnt == 'd990) begin

awlen_in_0 <= 'd255;

end

else begin

awlen_in_0 <= 0;

end

end

对于写数据,在wvalid和wready握手时,将sin波形数据赋值给DDR4写数据。

always @(posedge chnl_clk_0) begin

if (chnl_rst_0) begin

wdata_in_0 <= chnl_0_data;

end

else if (wvalid_0 && wready_0) begin

wdata_in_0 <= chnl_0_data;

end

end

assign aclken_0 = wvalid_0 & wready_0;

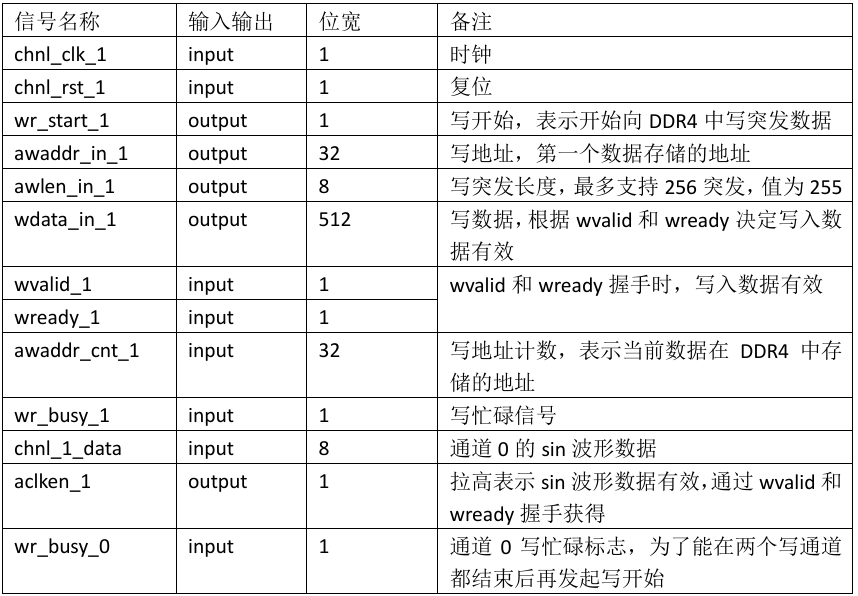

通道1接口列表:

对于产生写开始信号,与通道0的方式相同,不同点在与写地址的产生。

对于通道1的写地址,每次通道0的写长度都为256,那么通道2发起的写地址就为当前写地址计数+'h4000。

assign aclken_1 = wvalid_1 & wready_1;

always @(posedge chnl_clk_1) begin

if (chnl_rst_1) begin

wr_start_1_cnt <= 0;

end

else if (wr_start_1) begin

wr_start_1_cnt <= wr_start_1_cnt + 1;

end

end

always @(posedge chnl_clk_1) begin

if (chnl_rst_1) begin

clk_cnt <= 0;

end

else if (clk_cnt <= 'd999) begin

clk_cnt <= clk_cnt + 1;

end

end

always @(posedge chnl_clk_1) begin

wr_busy_1_r <= wr_busy_1;

end

always @(posedge chnl_clk_1) begin

if (chnl_rst_1) begin

wr_idle_flag_1 <= 0;

end

else if (wr_idle_flag_1 == 1 && wr_busy_0 == 0) begin

wr_idle_flag_1 <= 0;

end

else if (wr_busy_1 == 0 && wr_busy_1_r == 1) begin

wr_idle_flag_1 <= 1;

end

end

always @(posedge chnl_clk_1) begin

if (chnl_rst_1) begin

wr_start_1 <= 0;

end

else if (wr_idle_flag_1 == 1 && wr_busy_0 == 0 && wr_start_1_cnt <= 'd9) begin

wr_start_1 <= 1;

end

else if (clk_cnt == 'd990) begin

wr_start_1 <= 1;

end

else begin

wr_start_1 <= 0;

end

end

always @(posedge chnl_clk_1) begin

if (chnl_rst_1) begin

awaddr_in_1 <= 0;

end

else if (wr_idle_flag_1 == 1 && wr_busy_0 == 0 && wr_start_1_cnt <= 'd9) begin

awaddr_in_1 <= awaddr_cnt_1 + 'h4000;

end

else if (clk_cnt == 'd990) begin

awaddr_in_1 <= 'h4000;

end

else begin

awaddr_in_1 <= 0;

end

end

always @(posedge chnl_clk_1) begin

if (chnl_rst_1) begin

awlen_in_1 <= 0;

end

else if (wr_idle_flag_1 == 1 && wr_busy_0 == 0 && wr_start_1_cnt <= 'd9) begin

awlen_in_1 <= 'd255;

end

else if (clk_cnt == 'd990) begin

awlen_in_1 <= 'd255;

end

else begin

awlen_in_1 <= 0;

end

end

always @(posedge chnl_clk_1) begin

if (chnl_rst_1) begin

wdata_in_1 <= chnl_1_data;

end

else if (wvalid_1 && wready_1) begin

wdata_in_1 <= chnl_1_data;

end

end

三、 总结

本章节使用通道0和通道1来同时存储两个sin波形数据,下一章节通过仿真来更直观的观察并了解两个通道存储波形的过程。

本文章由威三学社出品

对课程感兴趣可以私信联系