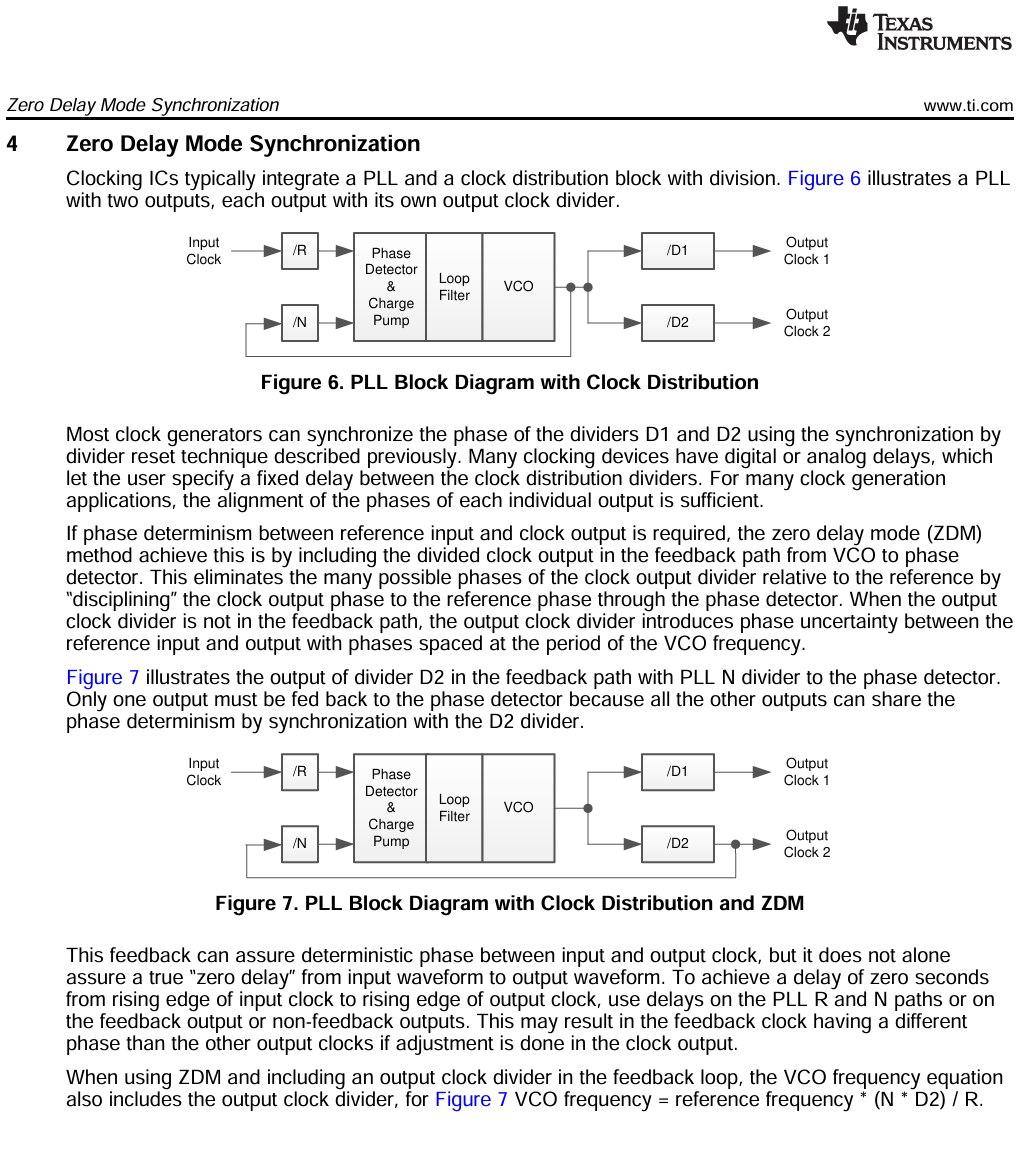

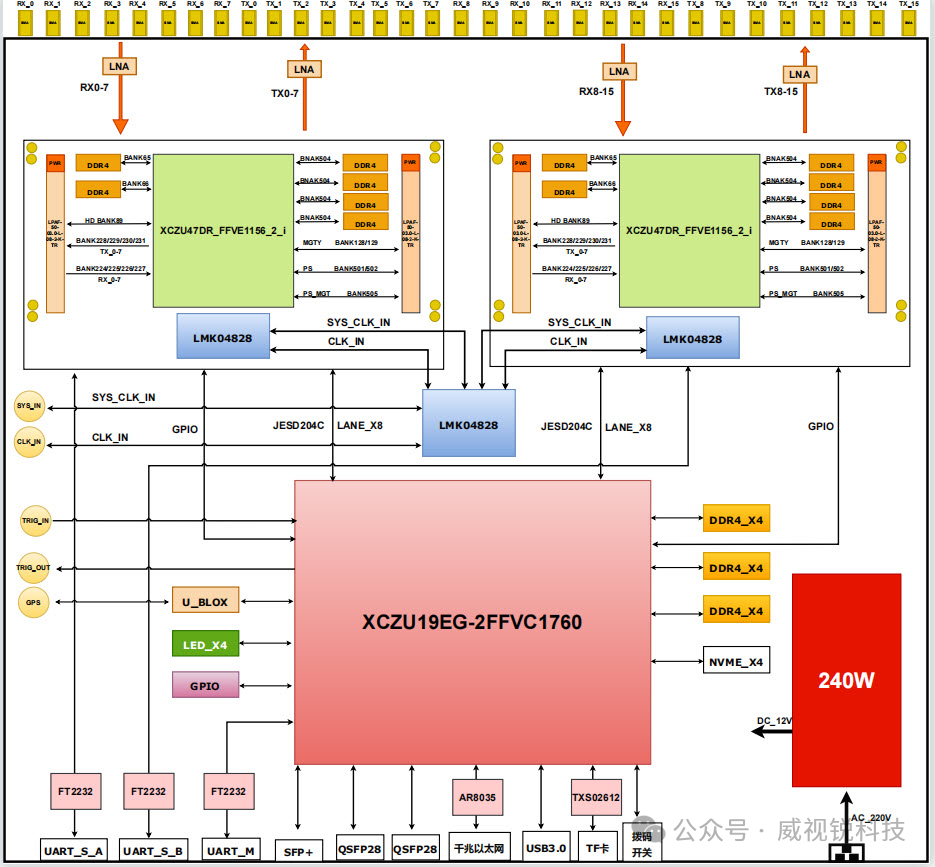

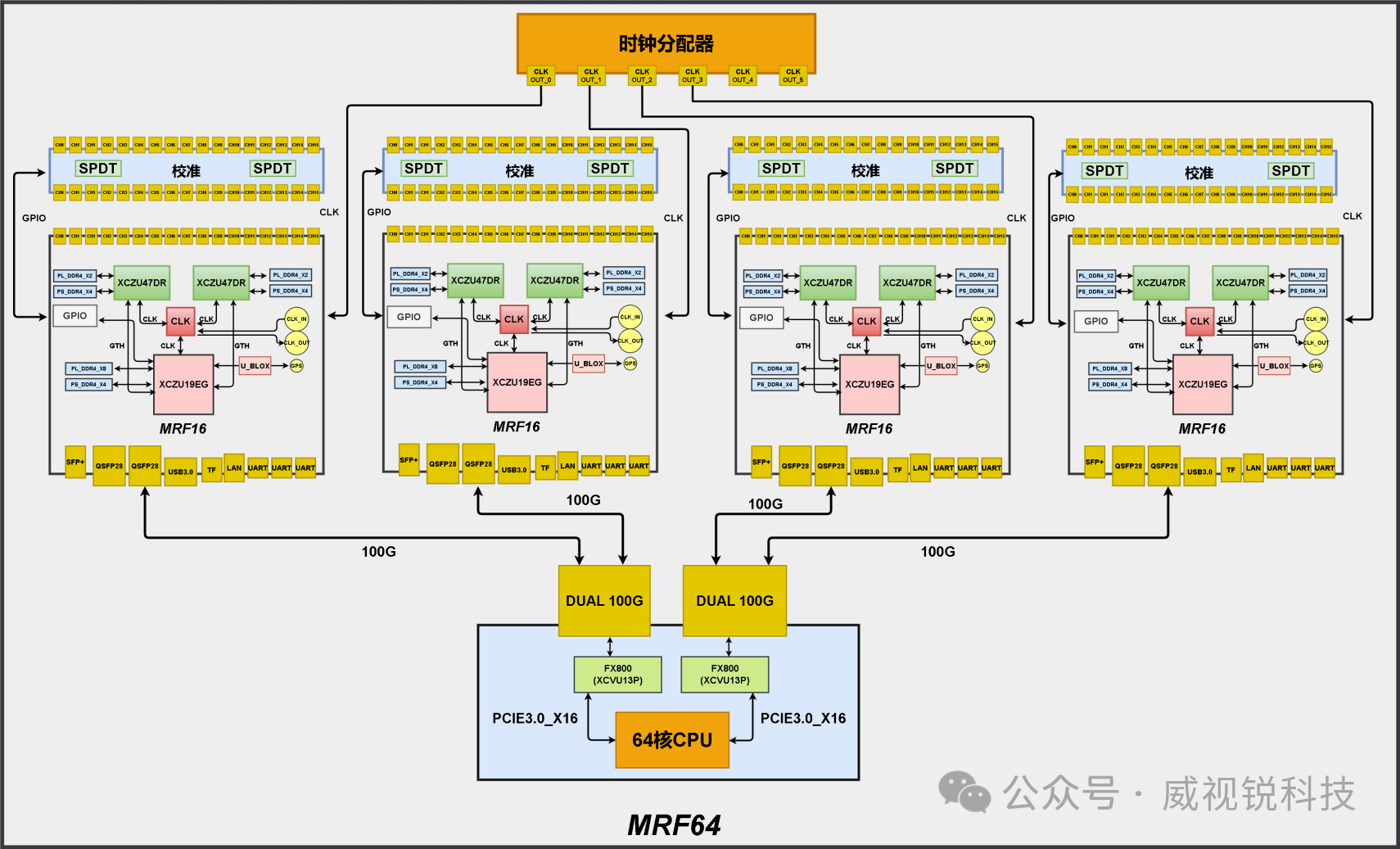

挖个坑,验证测试多片47/49dr同步方案可行性,每个LMK04828采用 Zero delay mode (ZDM)

参考资料:

1、https://iwave-global.com/articles/multi-board-synchronization-on-rfsoc-board-and-systems/

3、https://www.interwiser.com/?mod=cases_detail&id=7

5、https://www.ti.com/lit/ds/symlink/lmk04828.pdf?ts=1753089154048

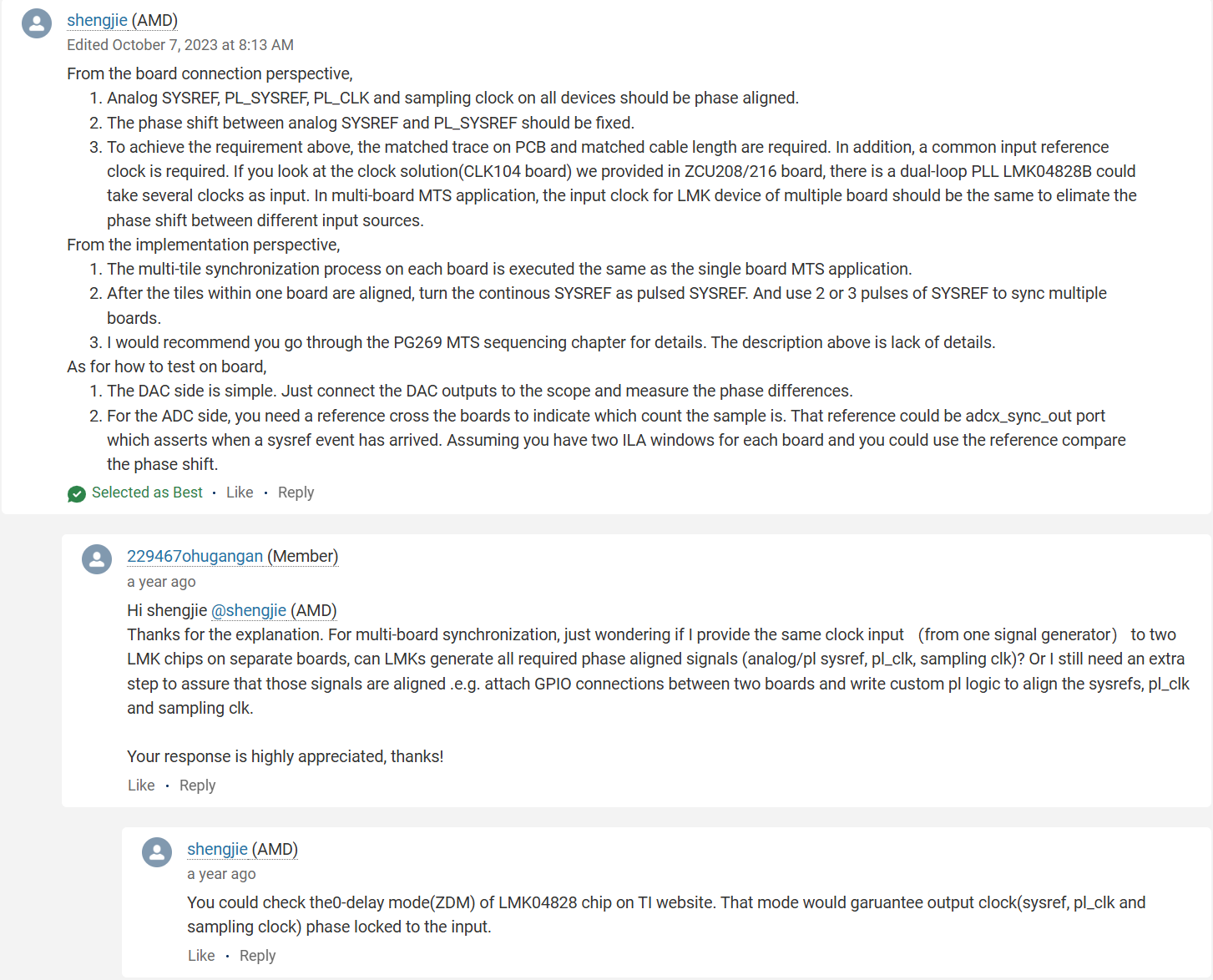

1、所有RFSoC上的Analog SYSREF、PL_SYSREF、PL_CLK 和 sampling clock 应该相位对齐

2、各个LMK04828 需要一个公共输入参考时钟,消除不同输入源之间的相位差

3、LMK04828 芯片的ZDM模式将确保输出时钟(SYSREF、PL_CLK 和 sampling clock)与公共输入参考时钟相位锁定

图来源:https://mp.weixin.qq.com/s/KAyK8p3yLFvkCv-GOao4cw

图来源:https://www.interwiser.com/?mod=cases_detail&id=7

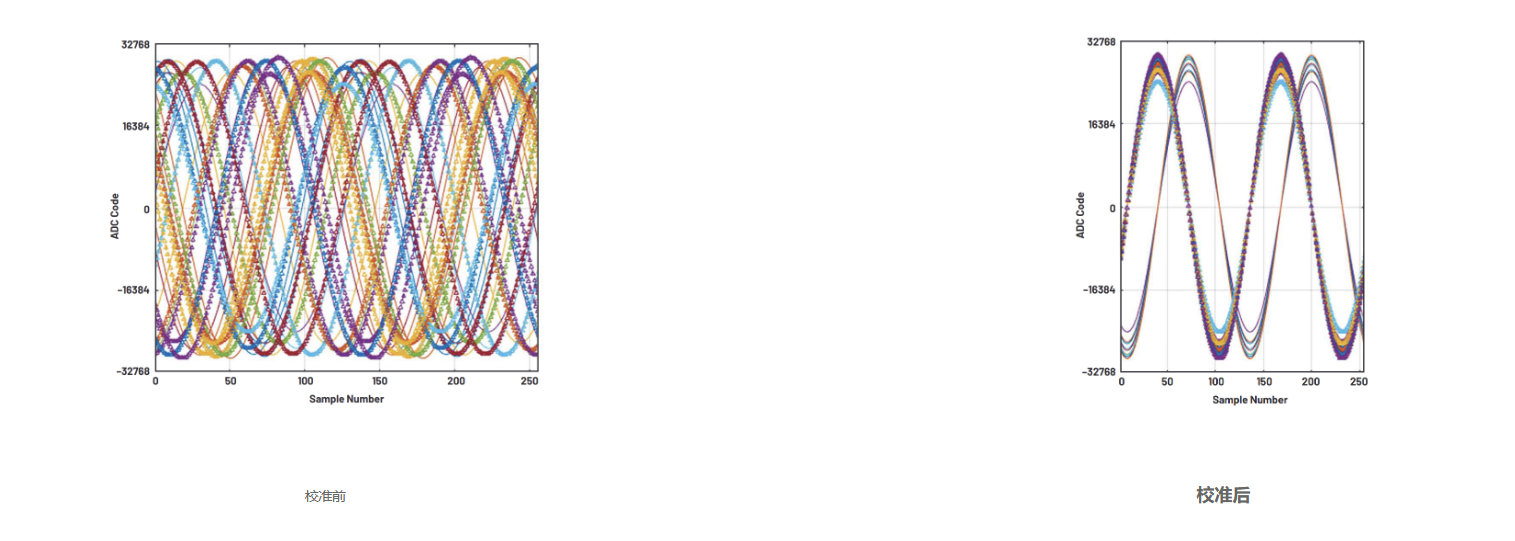

看看各个通道间的相位一致性和幅度一致性