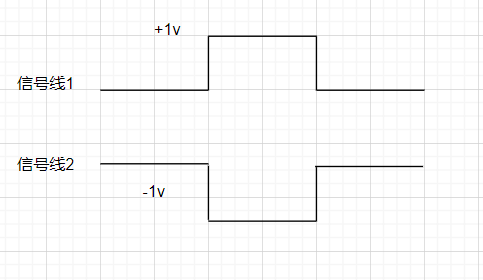

一、标准的差模干扰(等大反向)

标准的差模干扰是两根信号线上的干扰是大小相等,方向相反的干扰信号,但是这种太过理想,在实际电路中这种出现的概率比较小。

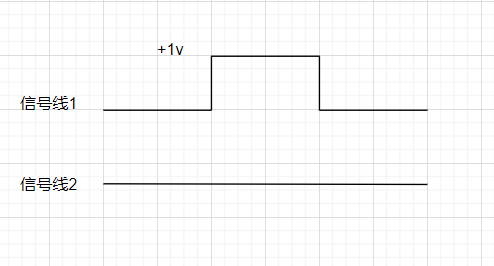

二、比较常见的差模干扰

一根信号线上有干扰,一根信号没有干扰。这个是比较常见的差模干扰,可以等效为信号线1上面+0.5v的干扰,信号线2上面-0.5v的干扰。

三、差模干扰说明

只要两根信号线上的干扰产生不一样的干扰,就可以认为是差模干扰。

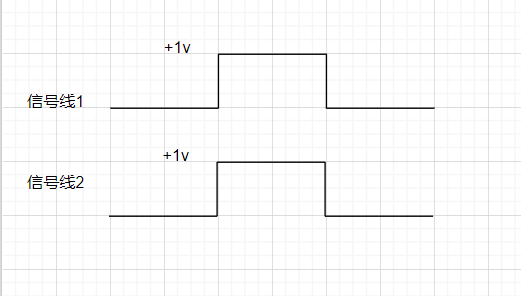

四、标准的共模干扰(等大同相)

两根信号线上的干扰是大小相同,相位也相同,就是比较标准的共模干扰,但是这种共模干扰的出现是比较理想的。

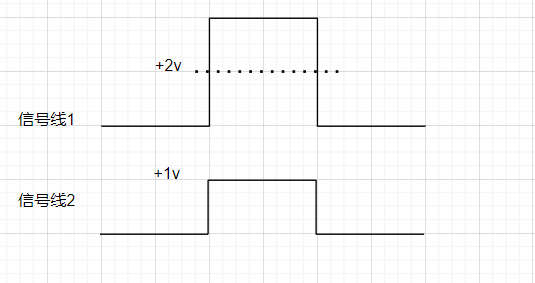

五、共模和差模干扰同时出现

信号线1上面是2v的干扰,信号线2上面是1v的干扰,这个可以将信号线的+2v等效为两个+1v,那么可以等效为(二)和(四),也就是相同的1v是共模干扰,那么多的1v就是差模干扰,说明这个图示既有共模干扰,也有差模干扰。

六、差模干扰和共模干扰

1.差模干扰和共模干扰是电路设计中的两种干扰模式。

2.其中差模干扰发生在信号线之间,两条信号线之间的电压波动。

3.共模干扰是信号线与GND之间的干扰。

七、差模干扰

1.干扰信号出现在两条信号线之间或者电源线之间,方向在两条线上面是相反的

2.干扰电流沿着设计好的信号路径流动,在去路和回路上面大小相等,方向相反

3.差模干扰在信号线L1和信号线L2之间形成回路

4.差模干扰的路径与有用信号的路径是完全一致的

八、差模干扰产生的原因

1.磁场耦合: 变化的磁场(如附近通电导线、变压器、电机)穿过信号线形成的环路,根据法拉第电磁感应定律在环路中感应出差模电压。

2.直接传导: 来自同一电源网络的其他设备的开关噪声、浪涌等通过电源线直接传导进来。

3.地线电位差: 如果电路两端的地电位存在差异(尤其在长导线或大电流地线情况下),这个电位差会直接串联叠加在信号回路中,表现为差模干扰。

九、共模干扰产生

电场耦合: 附近的高压源或快速变化的电压源(如开关电源、继电器、荧光灯镇流器)通过寄生电容耦合到设备电缆或内部电路上。

地环路: 当设备通过不同路径(如电源安全地和信号地)连接到大地时,由于大地电位差或大电流流过地线阻抗,会在不同接地点之间形成共模电压。

共模驱动源: 电路内部元件(如开关管、散热器)对地的快速电压变化(dv/dt)通过寄生电容耦合到其他电路。