1:记录一下在今的天仿真的时候,对信号打拍操作,发现打拍失败。

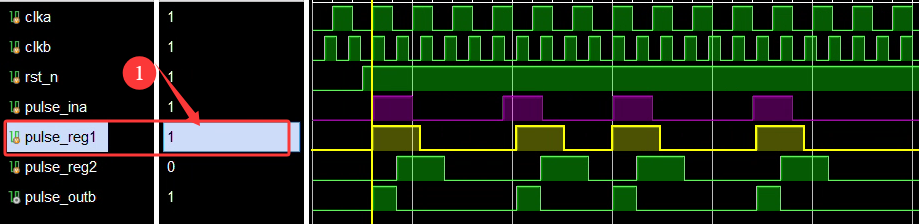

打拍失败现象如下:

verilog代码如下:

cpp

always @ (posedge clkb or negedge rst_n)

if (!rst_n)

begin

pulse_reg1 <= 0;

pulse_reg2 <= 0;

end

else

begin

pulse_reg1 <= pulse_ina ;

pulse_reg2 <= pulse_reg1 ;

end仿真代码如下:

cpp

module sim_slow2fast_cdc ( );

reg clka ;

reg clkb ;

reg rst_n ;

reg pulse_ina;

wire pulse_outb;

slow2fast_cdc slow2fast_cdc_inst (

.clka (clka) ,

.clkb (clkb) ,

.rst_n (rst_n) ,

.pulse_ina (pulse_ina) ,

.pulse_outb (pulse_outb)

);

always #10 clka = ~clka;

always #6 clkb = ~clkb;

initial begin

clka = 0;

clkb = 0;

rst_n = 0;

pulse_ina = 0;

#25

rst_n = 1; // 复位无效

#5 // 对齐

clk_come; #45

clk_come; #35

clk_come; #50

clk_come;

end

task clk_come;

begin

pulse_ina = 1; // 来一个慢时钟下的高脉冲

#20

pulse_ina = 0;

end

endtask

endmodule2:现象:可以看见pulse_reg1将pulse_ina信号采集并没有延迟1拍,从而形成打拍失败的结果;

3:问题原因:因为我们这个pulse_ina是模拟外部信号进入,是reg变量,我这里是D触发器要去采集pulse_ina,这里仿真代码是使用的是阻塞赋值;故而出现仿真打拍失败。

4:解决办法:将仿真文件里面的pulse_ina的阻塞赋值改成非阻塞赋值,即可解决。

修改之后仿真代码:

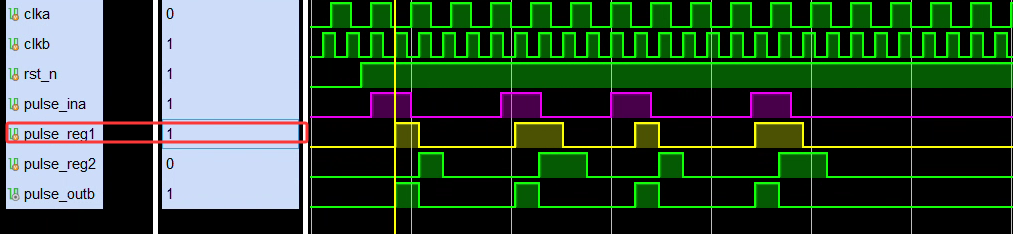

5:仿真结果如下;

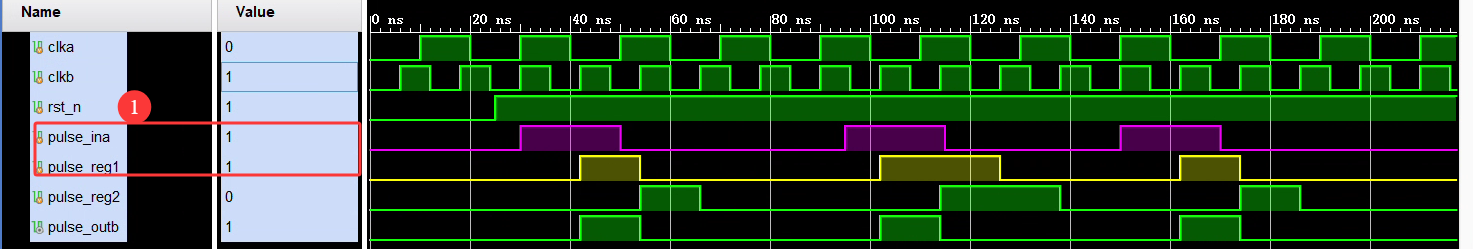

放大图效果:

6:总结:打拍成功;