【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

前面说过,传统的纯软件开发,在国内的大背景下面是很难存活的。但是如果是把软件,构建在硬件基础之上,并且在上面形成一定的优势,这样的产品是可以销售出去的。当然,软硬结合的方式很多,今天就来谈一谈。

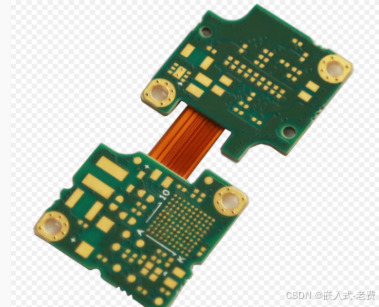

1、纯嵌入式方式

纯嵌入式,就是把软件借助于mcu、soc、dsp或者是fpga来实现。这是大多数嵌入式开发的方式,也是最容易理解的方式。这种方式的好处就是简单明了,缺点就是容易变成一锤子买卖,没有复购。

2、上位机+嵌入式模块的方式

和纯嵌入式方式相比较,这种方式的好处就是多一个上位机标定。一般来说,嵌入式产品都会实现一个功能,或者是算法。但是这些算法需要覆盖到不同的客户,势必需要标定不同的参数。这个时候,就需要通过上位机来标定参数,最后下载到嵌入式模块上面去完成。这些模块一般销量不大,但是价格ok,比较适合规模比较小的企业去完成。

3、linux+mcu的模式

很多的产品,单一soc,或者是单一mcu,都是没有办法完成的。比如是soc肯定需要实现很多的交互功能,而mcu则实现很多的实时控制功能。在这两个中间需要平衡的话,只能是soc内置mcu,或者是通过soc+外置mcu的方式来解决。很多的企业都是专注于soc厂商的方案,或者是只搞mcu,两者结合也是非常好的一个方式。

4、cpu+fpga的方式

如果说linux+mcu还算可以接受的话,那么cpu+fpga的方式确实难度要高不少。这种方式,目前来说主要是三种通信手段,第一是mcu+fpga,以agm芯片为主;还有一种是soc+fpga,可以跑linux,以zynq为主;最后的话,就是分立式元器件,即soc归soc,fpga归fpga,两者通过pcie、spi、iic等方式通信。fpga具有天生的并发性,如果能共享内存,通过内存实现通信,其实这是最好的处理方式。

5、差异化的创新模式

很多嵌入式产品,大家都是按照soc芯片厂的demo去做,这样实现可能速度比较快,但是缺点就是没有自己的特点,没有办法做出差异性。这个时候,我们就应该挖掘嵌入式的本质,努力去寻找替代解决方案,比如说能不能把高性能soc做分解;能不能用mcu+fpga代替;能不能用mcu代替;能不能用硬件去实现等等。

很多东西长期存在没有改进,一方面可能是由于毛利高,另外一方面可能也是大家觉得体量不大,没有改进的动力。但是现在是一个行业重新洗牌的时机,这种情况下其实要求我们更要拿出独树一帜的方案,而不仅仅是降价,不然根本没有竞争力的。

6、产品第一

很多时候,客户并不在乎你的方案,他只考虑做什么、实现什么功能、成本。至于怎么实现的,很多时候并不在意这些。所以最终,有一部分方案商是会自己去做产品的,能不能做成功就是另外一回事了。