第二部分:ECC (30, 24)RTL实现实战 - 精雕细琢的硬件卫士

理论是基石,实现是关键。本部分将 手把手构建参数化、可综合、高可靠的ECC编解码器 。本部分将以MIPI 协议中Packet Header 用到的ECC(30,24) 为例子,详细介绍其 verilog实现。

1. 模块架构:职责分明

层模块 Verilog

module ecc_correction (

i_clk ,

i_rst ,

i_data ,

i_ecc ,

i_valid ,

o_valid ,

o_errortype ,

o_data_rcv

);

//... 实例化syndrome_gen

//... 实例化syndrome_decoder

endmodule

module syndrome_decoder(

clk ,

rst ,

addr ,

ena ,

syn_code

);

//... 实例化sprom 查找表

endmodule

module sprom(

clk,

rst_n,

addr,

dout,

clk_en

);// 在 ecc_correction 模块内部

localparam int PARITY_WIDTH = $clog2(DATA_WIDTH) + 1; // 校验位宽计算公式 p = ceil(log2(k)) + 1

localparam int TOTAL_WIDTH = DATA_WIDTH + PARITY_WIDTH; // 编码后总位宽

✅ 工程优势: 使用 $clog2() 系统函数自动计算 校验位宽 PARITY_WIDTH 和总位宽 TOTAL_WIDTH。用户只需指定 DATA_WIDTH,模块自动适配, 极大提升复用性 。

2. 编码器(syndrome_gen)实现: 并行异或的艺术

Hamming code编码

assign o_ecc[7:6] = 2'b00;

assign o_ecc[5] = i_data[10]^i_data[11]^i_data[12]^i_data[13]^i_data[14]^i_data[15]^i_data[16]^i_data[17]^i_data[18]^i_data[19]^i_data[21]^i_data[22]^i_data[23];

assign o_ecc[4] = i_data[4]^i_data[5]^i_data[6]^i_data[7]^i_data[8]^i_data[9]^i_data[16]^i_data[17]^i_data[18]^i_data[19]^i_data[20]^i_data[22]^i_data[23];

assign o_ecc[3] = i_data[1]^i_data[2]^i_data[3]^i_data[7]^i_data[8]^i_data[9]^i_data[13]^i_data[14]^i_data[15]^i_data[19]^i_data[20]^i_data[21]^i_data[23];

assign o_ecc[2] = i_data[0]^i_data[2]^i_data[3]^i_data[5]^i_data[6]^i_data[9]^i_data[11]^i_data[12]^i_data[15]^i_data[18]^i_data[20]^i_data[21]^i_data[22];

assign o_ecc[1] = i_data[0]^i_data[1]^i_data[3]^i_data[4]^i_data[6]^i_data[8]^i_data[10]^i_data[12]^i_data[14]^i_data[17]^i_data[20]^i_data[21]^i_data[22]^i_data[23];

assign o_ecc[0] = i_data[0]^i_data[1]^i_data[2]^i_data[4]^i_data[5]^i_data[7]^i_data[10]^i_data[11]^i_data[13]^i_data[16]^i_data[20]^i_data[21]^i_data[22]^i_data[23];3.解码器(syndrome_decoder)实现: 查找表

ECC Correction 模块的核心模块,由解码地址查询出错位置,纠正单bit错误,标注两位及以上的错误。功能由C代码实现,生成一个可查询的文件。

4. 校正错误码

assign o_data_rcv = header^syn_code[31:0]; // 对被检测到的单比特错误取反

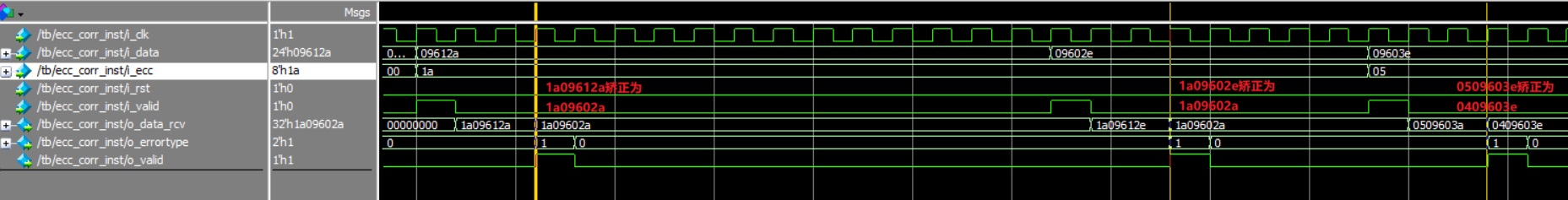

5.仿真波形

6. 总结与附件

总结:

通过以上实现,我们成功将汉明码理论转化为一个参数化、可综合的硬件模块。它能够实时检测并尝试纠正单位错,检测双位错(标记为不可纠正),为芯片数据完整性提供基础保障。

附件:

随本文提供的附件包括:ECC校正实现的Verilog 、testbench 和仿真 script, 以及C和Python源代码

sim --- simulation script

src --- source code

tb --- test bench files

tool --- C code and Python script