文章目录

- [1. 与ILA的区别](#1. 与ILA的区别)

- [2. 使用Reveal步骤](#2. 使用Reveal步骤)

- 3.Reveal注意事项

- 4.传送门

1. 与ILA的区别

Reveal是Lattice Diamond集成开发环境用于在线监测信号的工具,ILA是xilinx的Vivado集成开发工具的在线逻辑分析仪,同Reveal一样,均可以在项目运行过程中,通过JTAG检测当前的信号状态。但二者的使用方式有些差异,ILA是通过IP核的形式,用户生成自定义的配置,然后在工程中具体位置例化。而Lattice的Reveal工具像IP配置一样,通过配置要检测的信号,生成后缀为rvl的文件,然后在综合生成bit流之前,将其设置为active文件。然后bit通过jtag写入fpga,在使用另外一个工具查看。由于Reveak是与工程是绑定的,也就是可以在另外一个工程中下载本工程的bit文件,但是无法在其他工程中打开本工程的Reveal工具,此外,ILA的触发条件灵活,支持多级触发、边沿/电平/组合条件。所以个人感觉还是ILA更为灵活一些。

2. 使用Reveal步骤

这里创建了一个简单的demo工程进行演示。需要用 Lattice Diamond/Radiant 插入 Reveal Inserter,然后通过 Reveal Analyzer 软件独立连接。

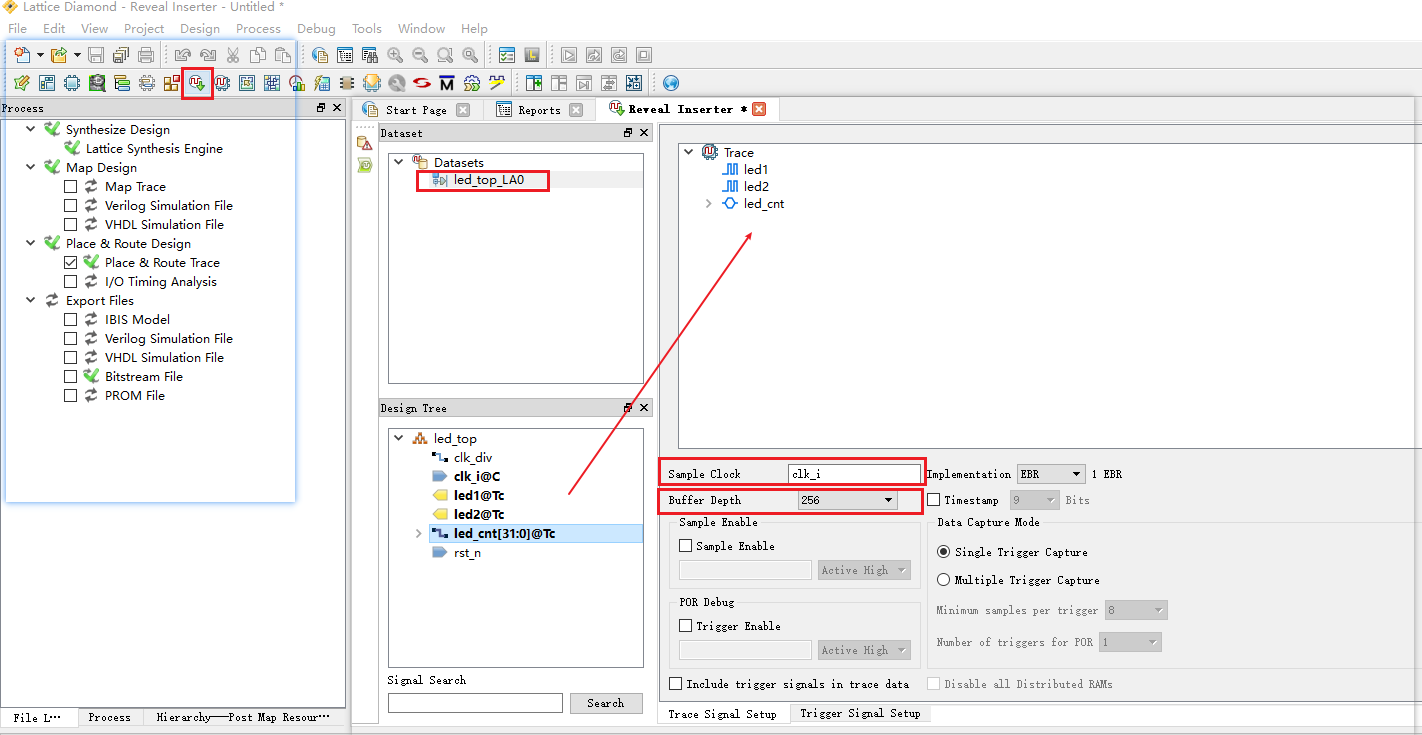

①当工程生成bit文件之后,点击如图所示的工具栏的Reveal Inserter按钮打开Trace Signal Setup页面。led_top_LA0处是core的位置,一个core可以监测一个时钟域的信号,相当于ILA实例化的一个IP,将需要监测的信号拖至Trace下面,下方设置采样时钟和Buffer深度,这个深度与其占用的FPGA资源是相关的。

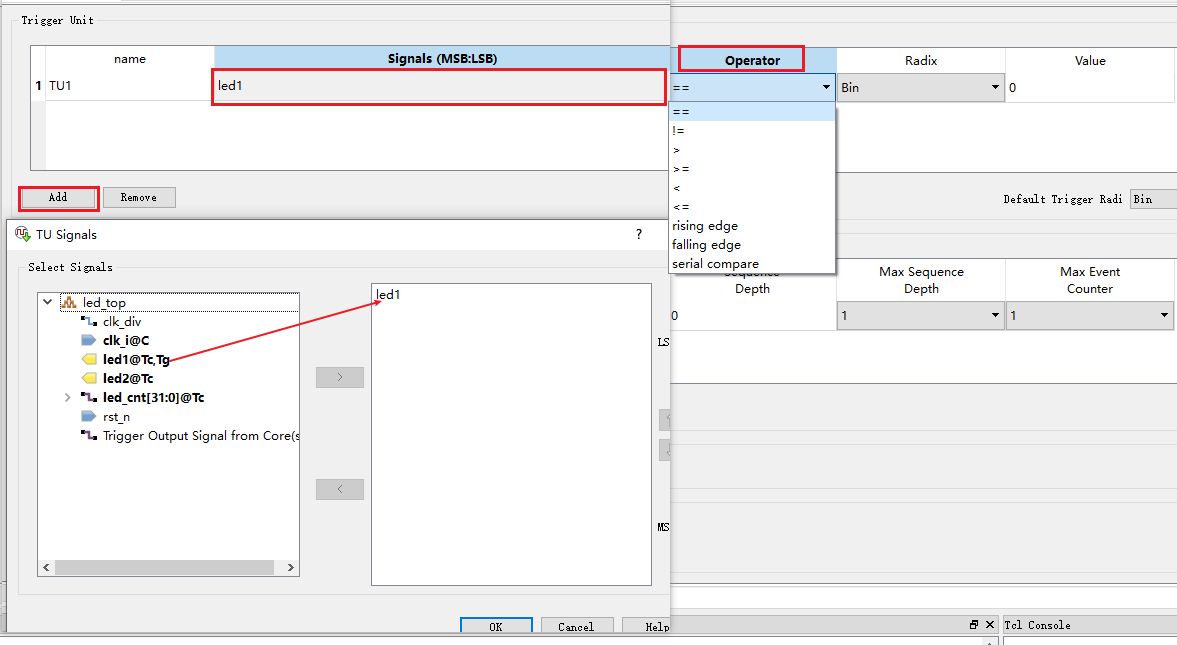

②切换至Trigger Signal Setup设置触发条件触发信号。Trigger Unit区域显示的是触发条件,可以点击Add添加多个条件,双击图中led1处可以选择触发信号,Operator处选择触发条件

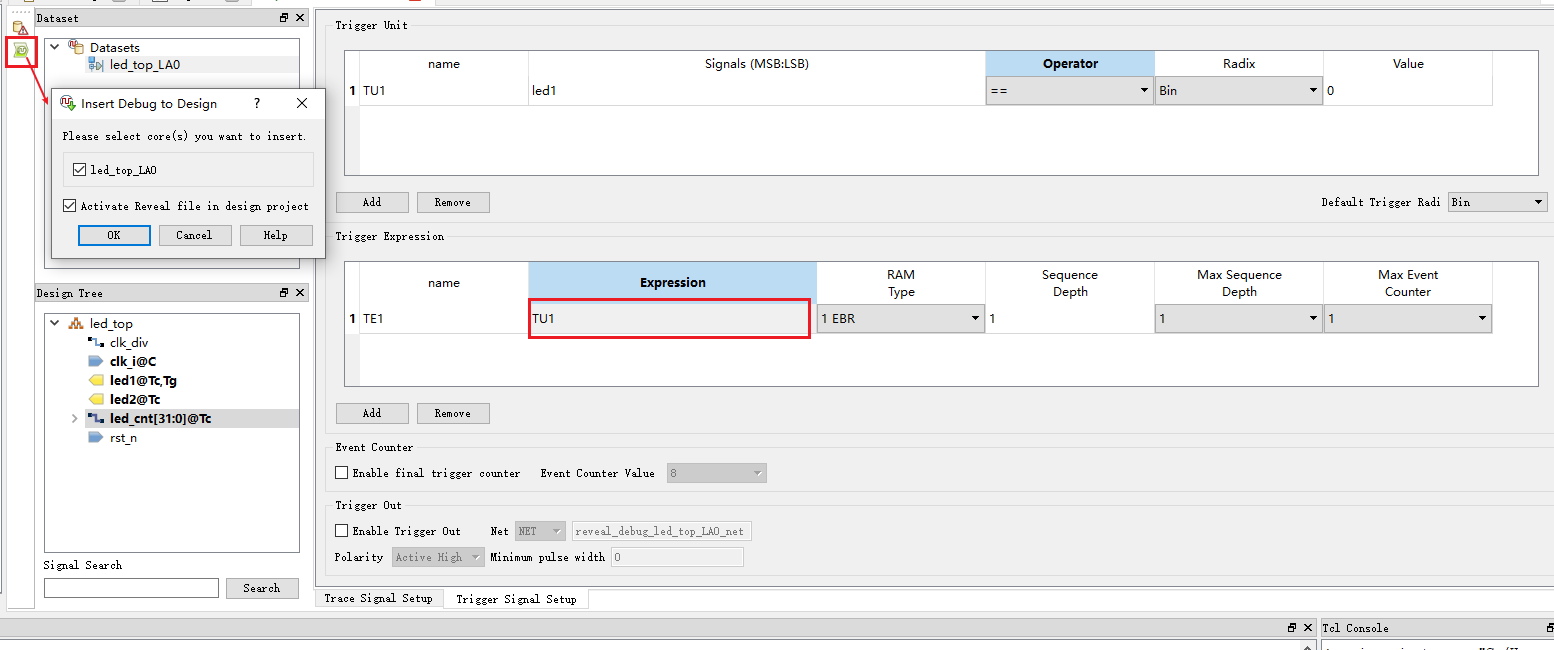

③接着上个页面在Trigger Expression界面选择要触发的信号,若上面有多个,这里可以选择任一个,设置完毕后点击图中绿色按钮保存。按照我的文件保存习惯,会把reveal相关的文件存在工程目录下的ILA文件夹里。

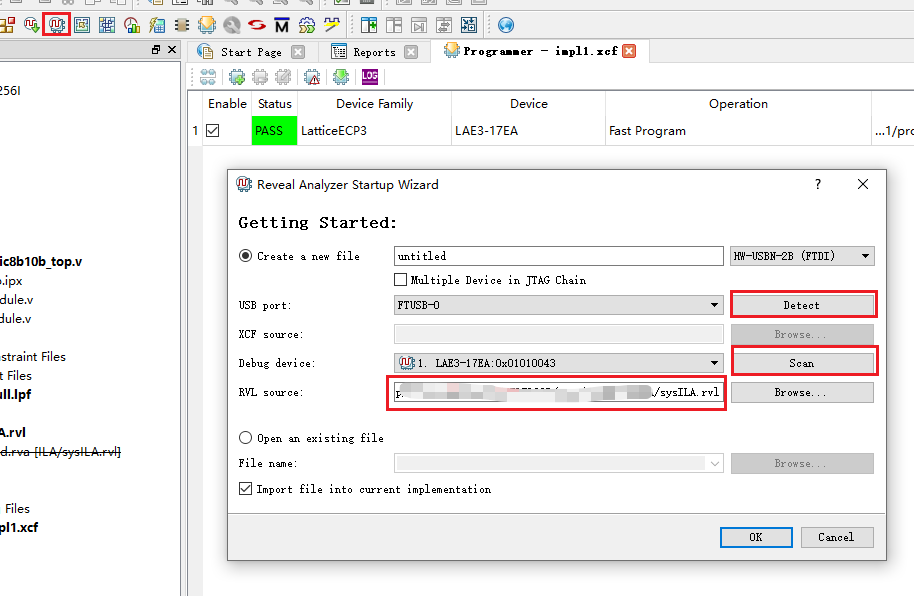

④将bit文件烧写进fpga,然后选择图中Reveal Analyzer按钮弹出界面创建rva文件用于a在线监测。Detect会查询发现当前在线USB Port,Scan则会显示当前调试的设备,在RVL source处选择上面生成的rvl文件,点击OK生成rva文件(我将其与rvl放在一个文件夹管理)。

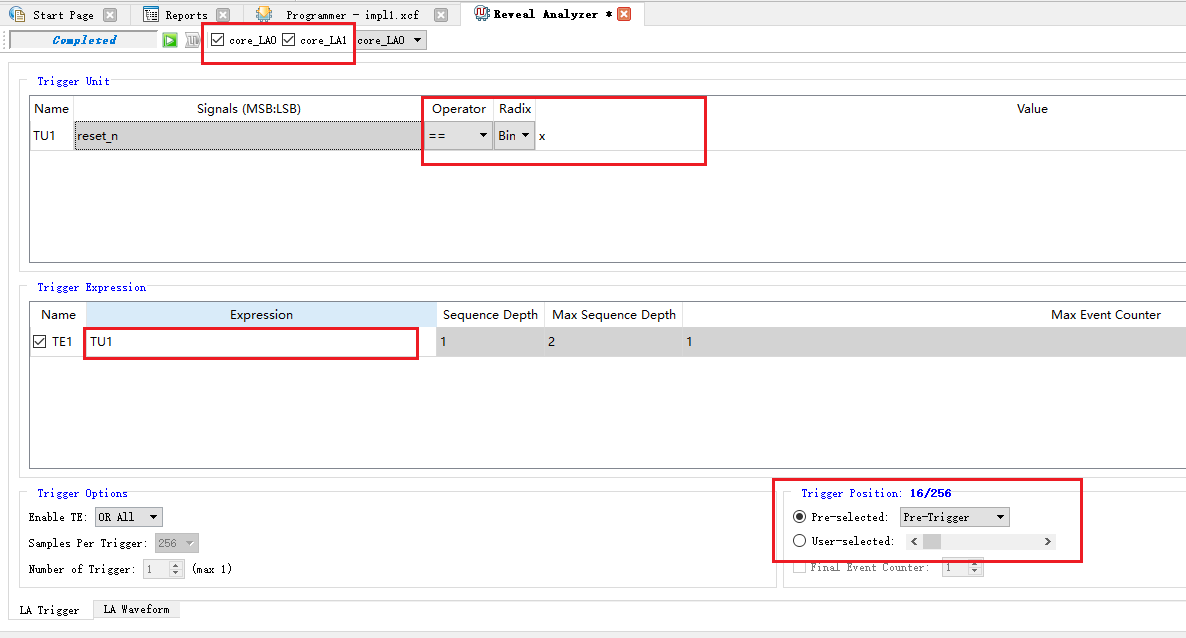

⑤如图所示,当有多个core时可以通过勾选的方式选择哪个或多个core在运行,然后在Trigger Unit界面设置信号触发的条件,在右下角设置触发区域在UI界面中的区域,当资源有限时, 选择合适的区域触发可以有效减少资源使用。

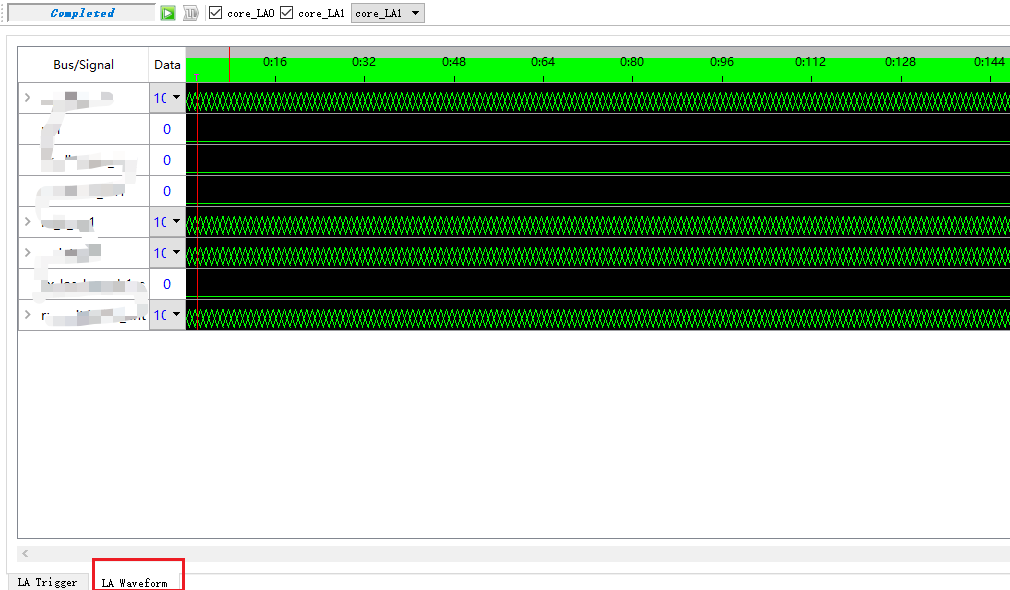

⑥最后会看到信号波形如下所示。

3.Reveal注意事项

1.如何更新reveal的信号?

A:如果有IP核,就重新生成一个IP核,如果没有就关闭工程重新打开一下。

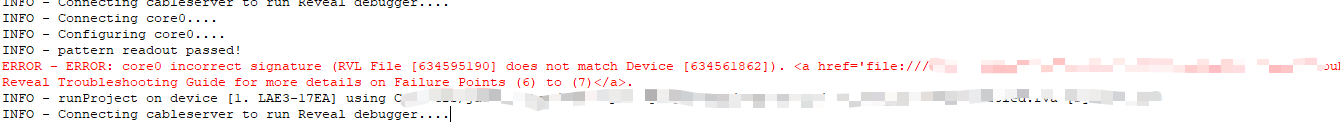

2.当bit文件与本工程的ILA不一致时,会报如下错误,因此要注意工程与bit文件一致操作。

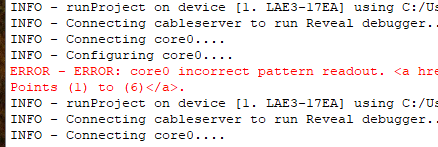

3.在Reveal操作器件如果JTAG断开连接,会提示如下错误。

4.传送门

|-----|

| END |

📡文章原创,首发于CSDN论坛。

📡欢迎点赞♥♥收藏⭐⭐打赏💵💵!

📡欢迎评论区或私信指出错误💉,提出宝贵意见或疑问😱。