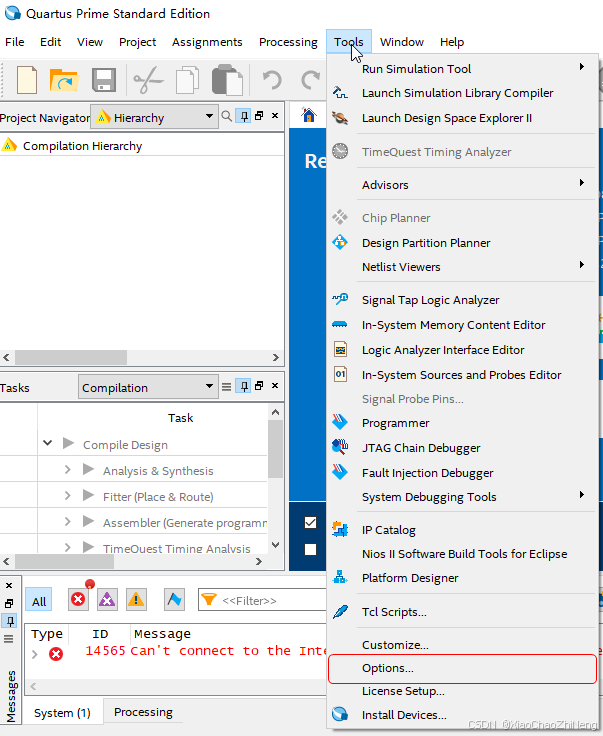

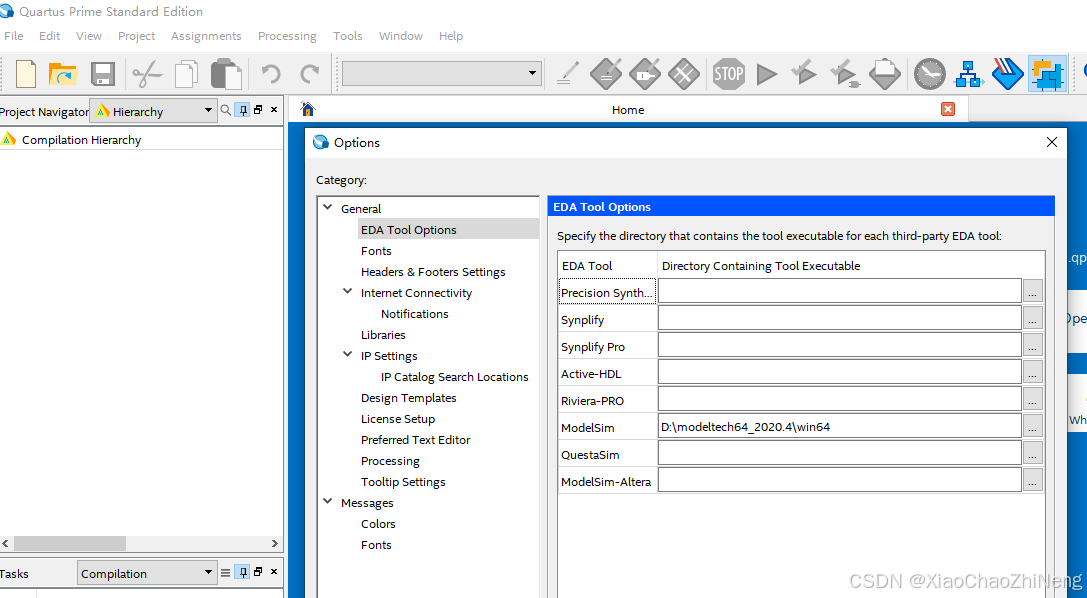

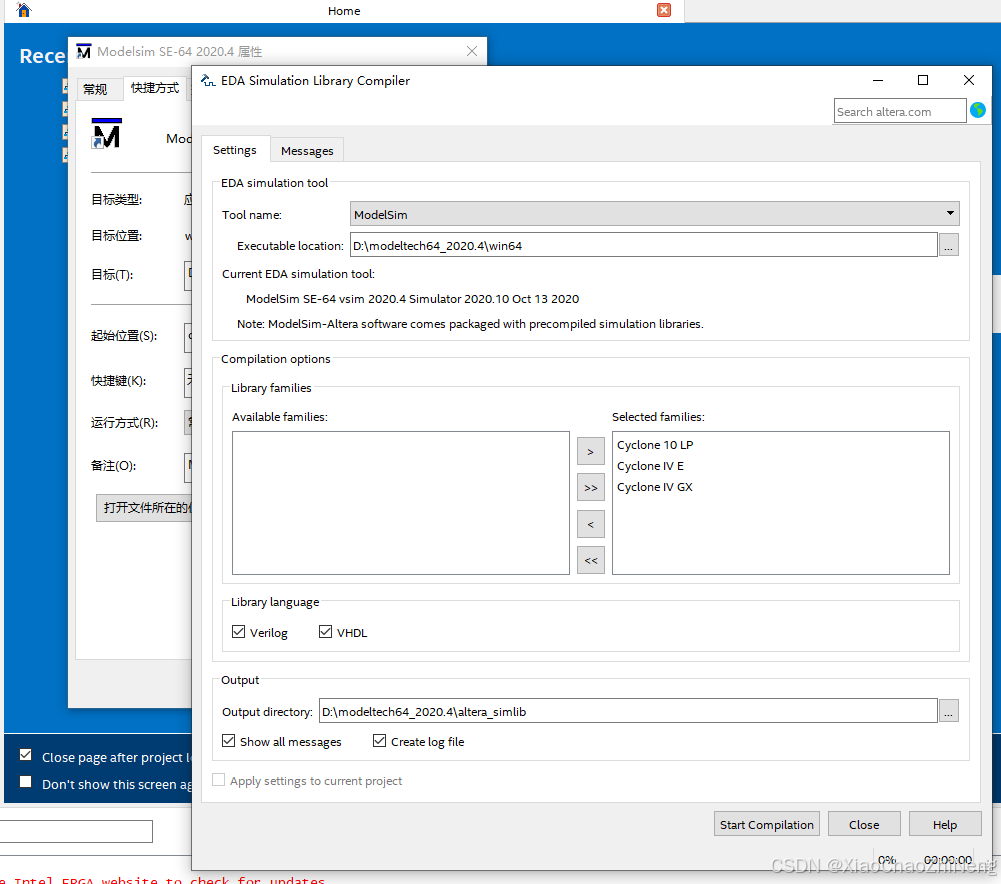

1 关联Modelsim配置

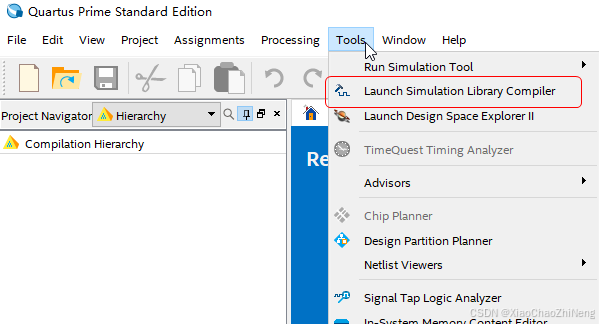

2 器件库编译

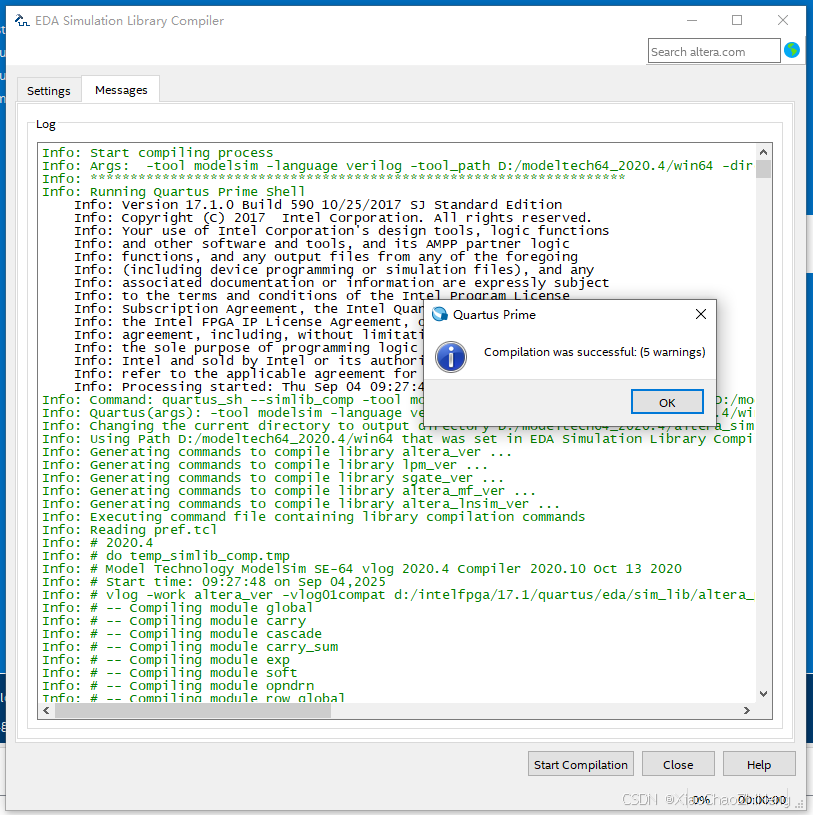

Info: Start compiling process

Info: Args: -tool modelsim -language verilog -tool_path D:/modeltech64_2020.4/win64 -directory D:/modeltech64_2020.4/altera_simlib -log modelsim_verilog_no_rtl -rtl_only

Info: *******************************************************************

Info: Running Quartus Prime Shell

Info: Version 17.1.0 Build 590 10/25/2017 SJ Standard Edition

Info: Copyright (C) 2017 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and its AMPP partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the applicable agreement for further details.

Info: Processing started: Thu Sep 04 09:27:46 2025

Info: Command: quartus_sh --simlib_comp -tool modelsim -language verilog -tool_path D:/modeltech64_2020.4/win64 -directory D:/modeltech64_2020.4/altera_simlib -log modelsim_verilog_no_rtl -rtl_only

Info: Quartus(args): -tool modelsim -language verilog -tool_path D:/modeltech64_2020.4/win64 -directory D:/modeltech64_2020.4/altera_simlib -log modelsim_verilog_no_rtl -rtl_only

Info: Changing the current directory to output directory D:/modeltech64_2020.4/altera_simlib ..

Info: Using Path D:/modeltech64_2020.4/win64 that was set in EDA Simulation Library Compiler Options

Info: Generating commands to compile library altera_ver ...

Info: Generating commands to compile library lpm_ver ...

Info: Generating commands to compile library sgate_ver ...

Info: Generating commands to compile library altera_mf_ver ...

Info: Generating commands to compile library altera_lnsim_ver ...

Info: Executing command file containing library compilation commands

Info: Reading pref.tcl

Info: # 2020.4

Info: # do temp_simlib_comp.tmp

Info: # Model Technology ModelSim SE-64 vlog 2020.4 Compiler 2020.10 Oct 13 2020

Info: # Start time: 09:27:48 on Sep 04,2025

Info: # vlog -work altera_ver -vlog01compat d:/intelfpga/17.1/quartus/eda/sim_lib/altera_primitives.v

Info: # -- Compiling module global

Info: # -- Compiling module carry

Info: # -- Compiling module cascade

...............

...............

...............

Info: # -- Loading package cycloneiv_pllpack

Info: # -- Loading entity cycloneiv_mn_cntr

Info: # -- Loading entity cycloneiv_scale_cntr

Info: # -- Loading entity cycloneiv_dffe

Info: # -- Loading entity cycloneiv_pll_reg

Info: # -- Compiling entity cycloneiv_pll

Info: # -- Compiling architecture vital_pll of cycloneiv_pll

Info: # End time: 09:28:21 on Sep 04,2025, Elapsed time: 0:00:00

Info: # Errors: 0, Warnings: 1

Info: # Model Technology ModelSim SE-64 vcom 2020.4 Compiler 2020.10 Oct 13 2020

Info: # Start time: 09:28:21 on Sep 04,2025

Info: # vcom -work cycloneiv -93 d:/intelfpga/17.1/quartus/eda/sim_lib/cycloneiv_components.vhd

Info: # -- Loading package STANDARD

Info: # -- Loading package TEXTIO

Info: # -- Loading package std_logic_1164

Info: # -- Loading package VITAL_Timing

Info: # -- Loading package VITAL_Primitives

Info: # -- Loading package cycloneiv_atom_pack

Info: # -- Compiling package cycloneiv_components

Info: # End time: 09:28:21 on Sep 04,2025, Elapsed time: 0:00:00

Info: # Errors: 0, Warnings: 0

Info: Successfully compiled the libraries

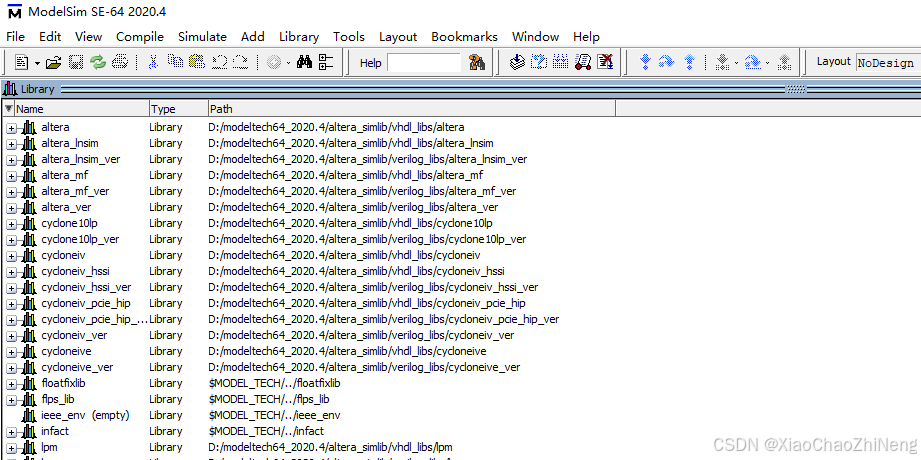

Info: Compilation was successful. 0 errors, 5 warnings3 关联库

altera_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/altera_ver

lpm_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/lpm_ver

sgate_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/sgate_ver

altera_mf_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/altera_mf_ver

altera_lnsim_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/altera_lnsim_ver

cyclone10lp_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/cyclone10lp_ver

cycloneive_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/cycloneive_ver

cycloneiv_hssi_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/cycloneiv_hssi_ver

cycloneiv_pcie_hip_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/cycloneiv_pcie_hip_ver

cycloneiv_ver = D:/modeltech64_2020.4/altera_simlib/verilog_libs/cycloneiv_ver

altera = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/altera

lpm = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/lpm

sgate = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/sgate

altera_mf = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/altera_mf

altera_lnsim = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/altera_lnsim

cyclone10lp = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/cyclone10lp

cycloneive = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/cycloneive

cycloneiv_hssi = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/cycloneiv_hssi

cycloneiv_pcie_hip = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/cycloneiv_pcie_hip

cycloneiv = D:/modeltech64_2020.4/altera_simlib/vhdl_libs/cycloneiv将上述库信息,更新到安装目录下的modelsim.ini文件,重启modelsim,可看到库文件已经映射到工具中。

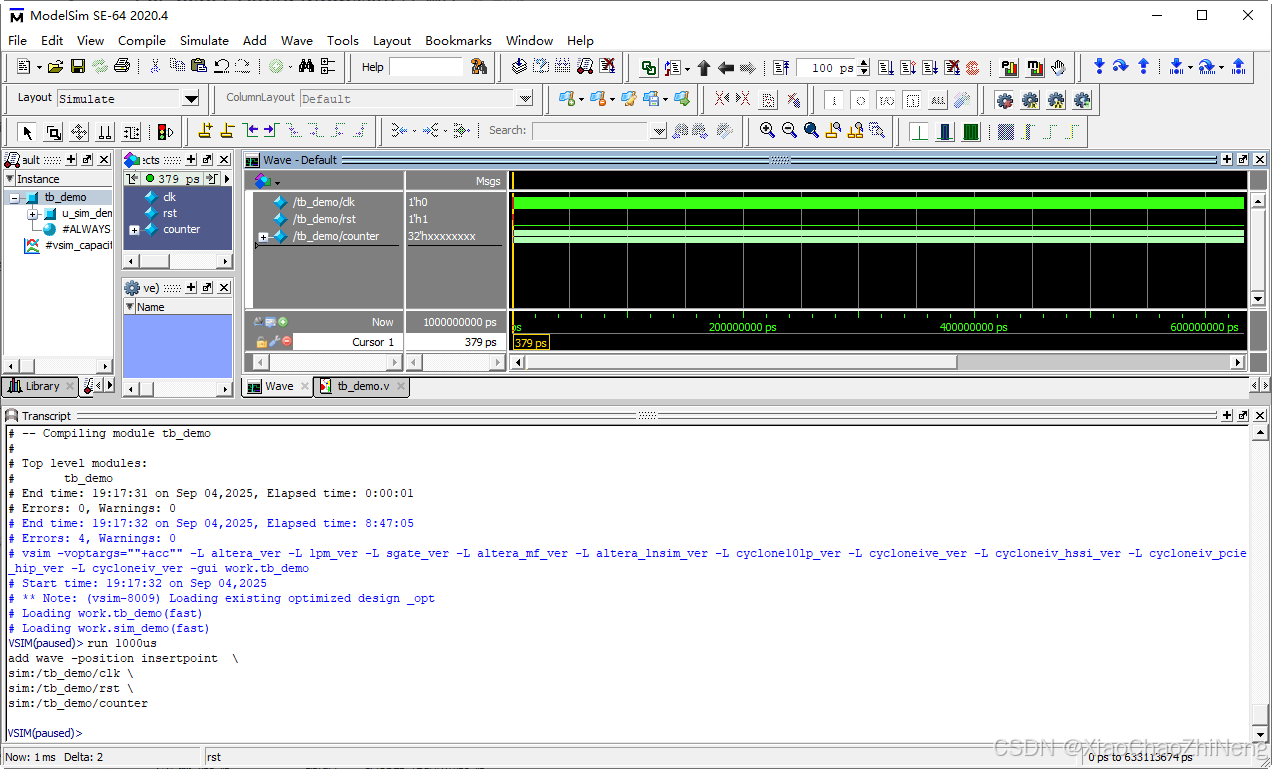

4 仿真运行

vlib work

vlog "../src/sim_demo.v"

vlog "tb_demo.v"

vsim -voptargs="+acc" -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cyclone10lp_ver -L cycloneive_ver -L cycloneiv_hssi_ver -L cycloneiv_pcie_hip_ver -L cycloneiv_ver -gui work.tb_demo

log -r /*