文章目录

前言

相关参考链接

问题描述

写在后面

前言

由于本人的水平有限,写的博文中难免有些疏漏,欢迎大家批评指正,只知道这样配置可以实现效果,具体原理更是一知半解。

相关参考链接

不得不说现在的AI是越来越强大了,遇到不懂的问题直接问DeepSeek能解决99%的问题。

我最开始遇到这个问题,在网上找了很久都没有找到相关讲解,然后直接将FIR IP核的数据手册pg149,发给deepseek让它帮我分析,最终就找到问题了。

问题描述

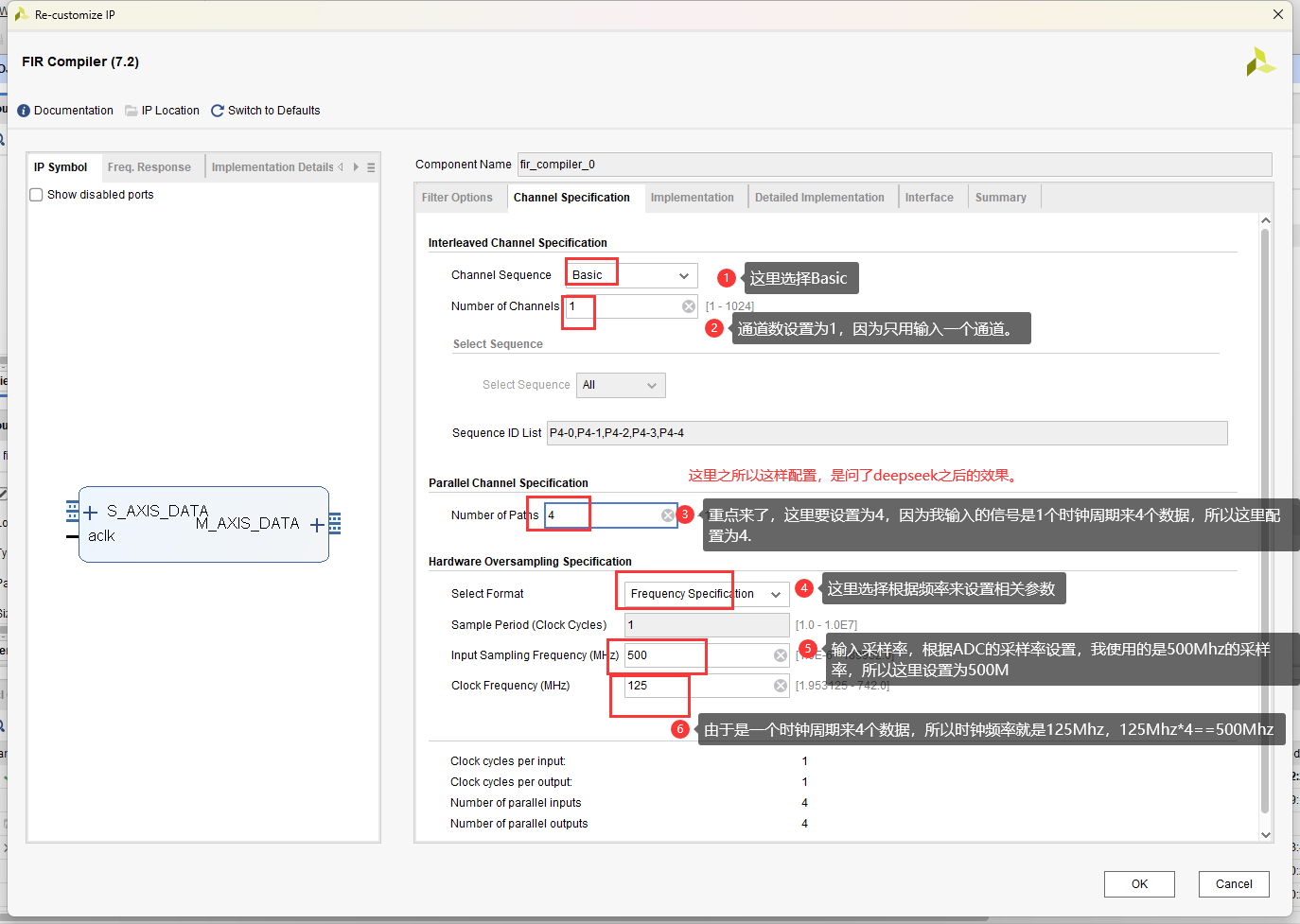

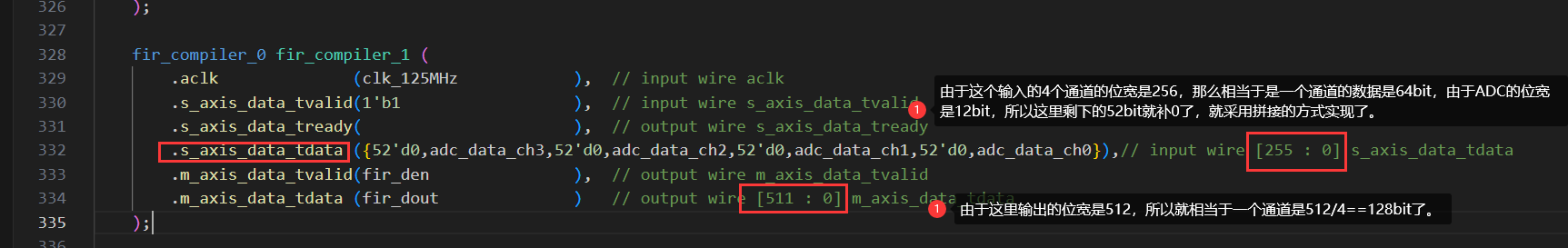

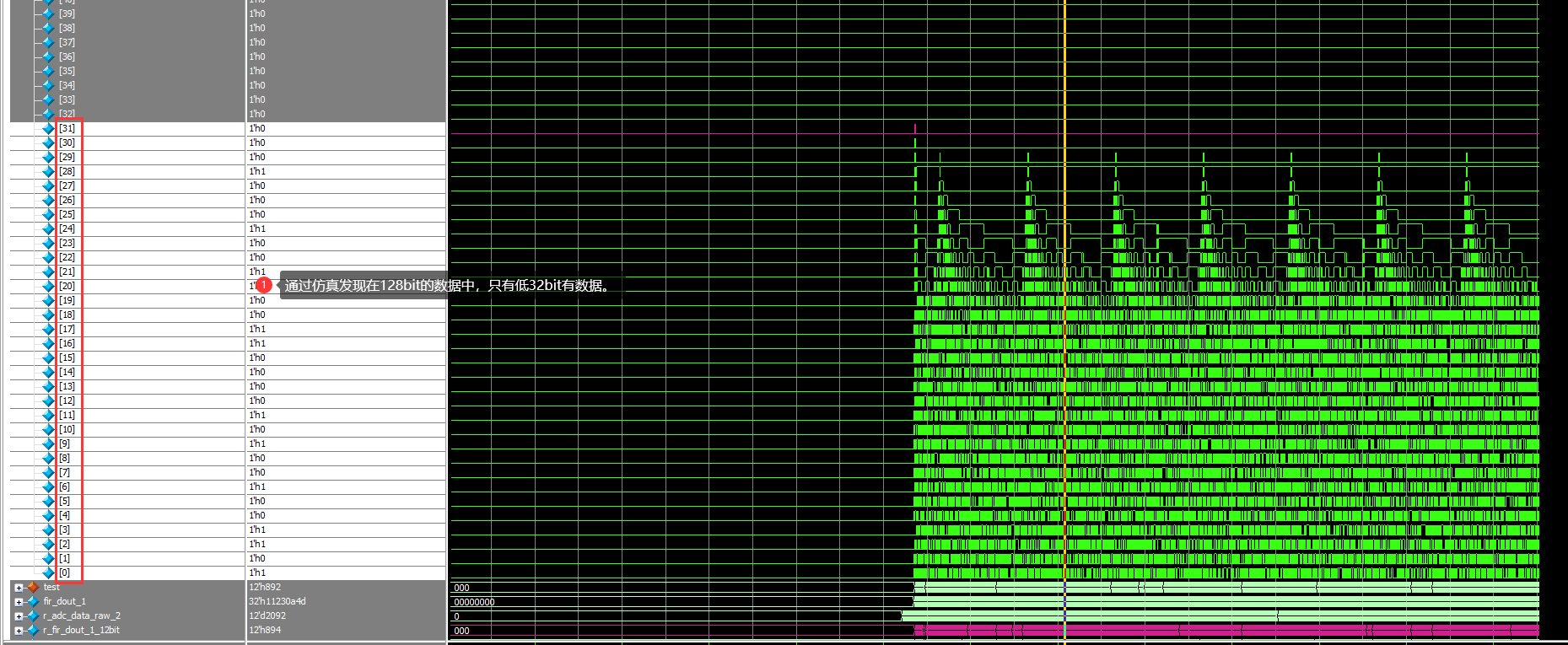

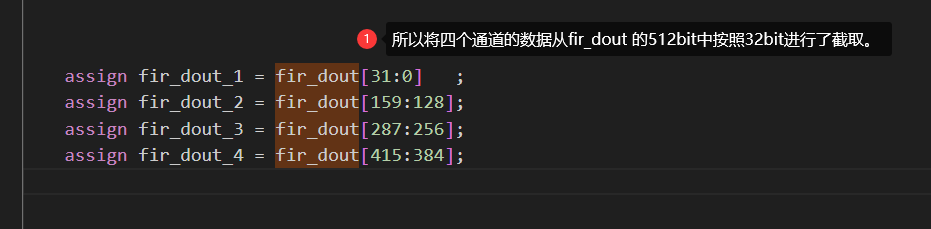

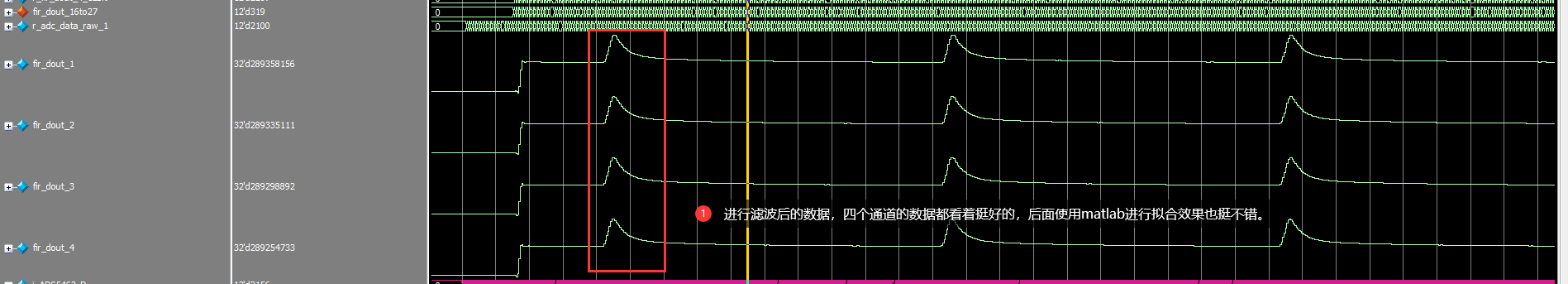

在项目中使用了一款500Mhz采样率ADC,由于硬件电路杂波信号太多,硬件电路滤波效果不佳,考虑使用xilinx 的FIR IP核进行数字滤波。但内部对ADC的数据处理是125Mhz的一个时钟周期来4个数据,也就是125Mhz*4 == 500Mhz。

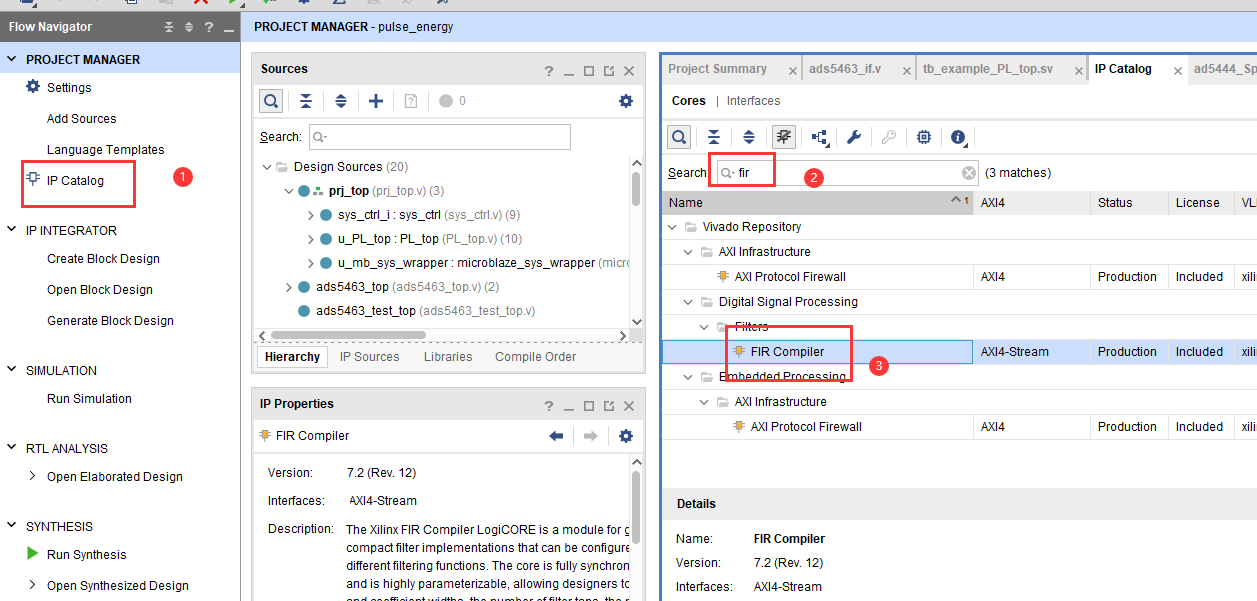

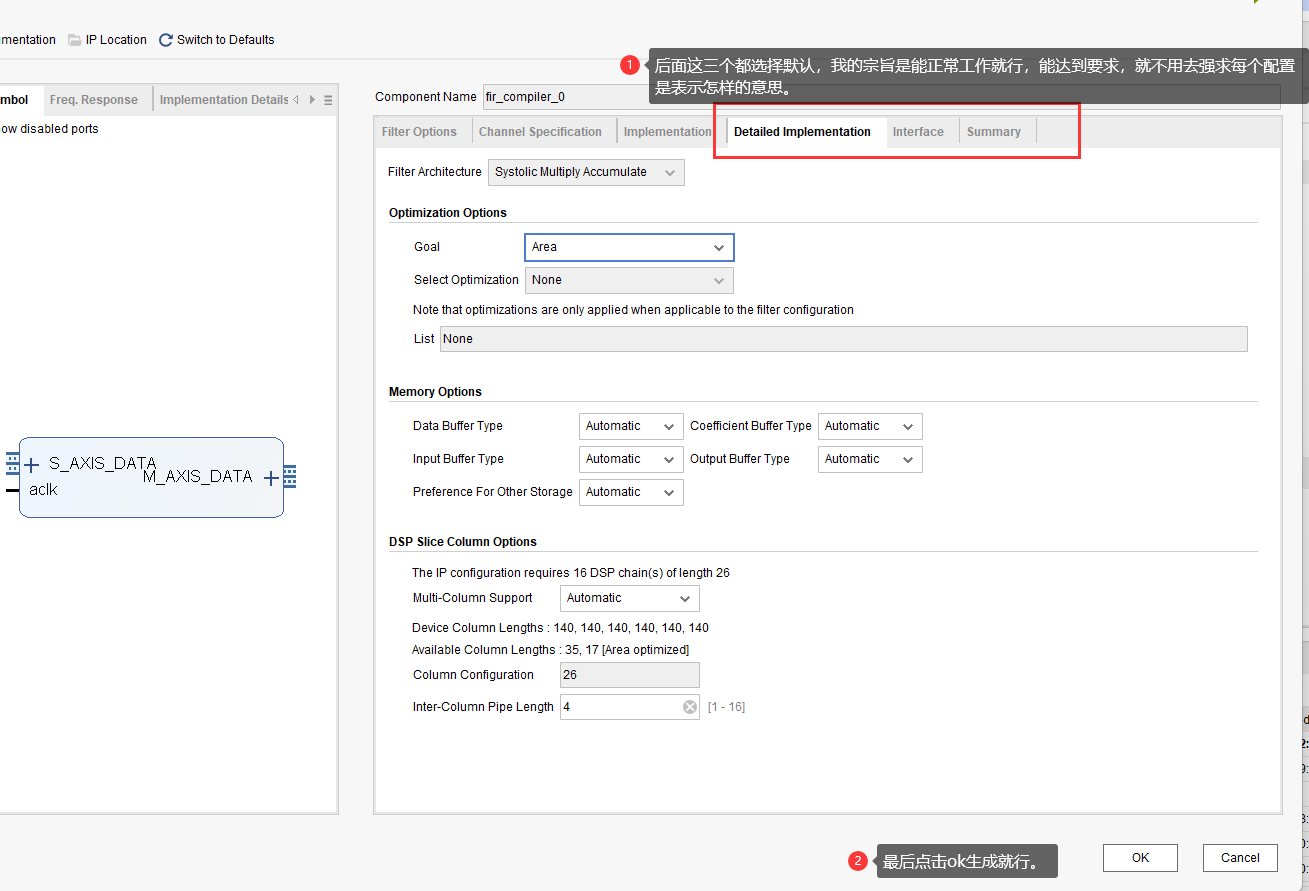

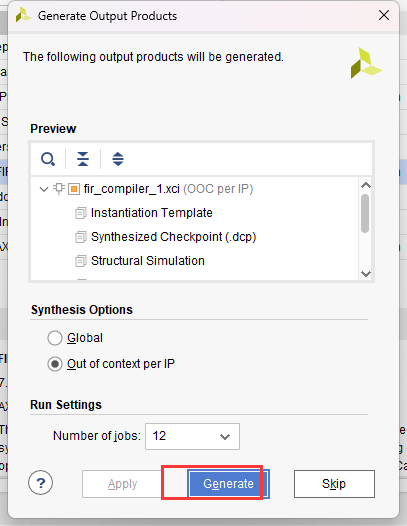

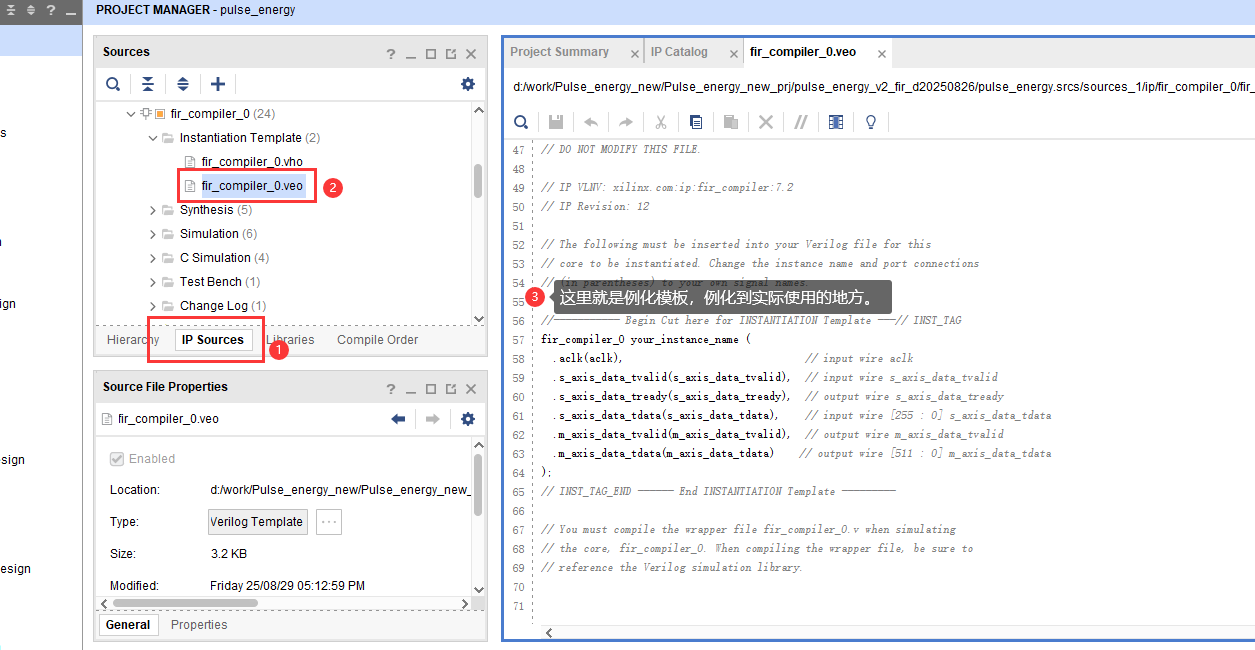

FIR IP核相关配置

0、说明

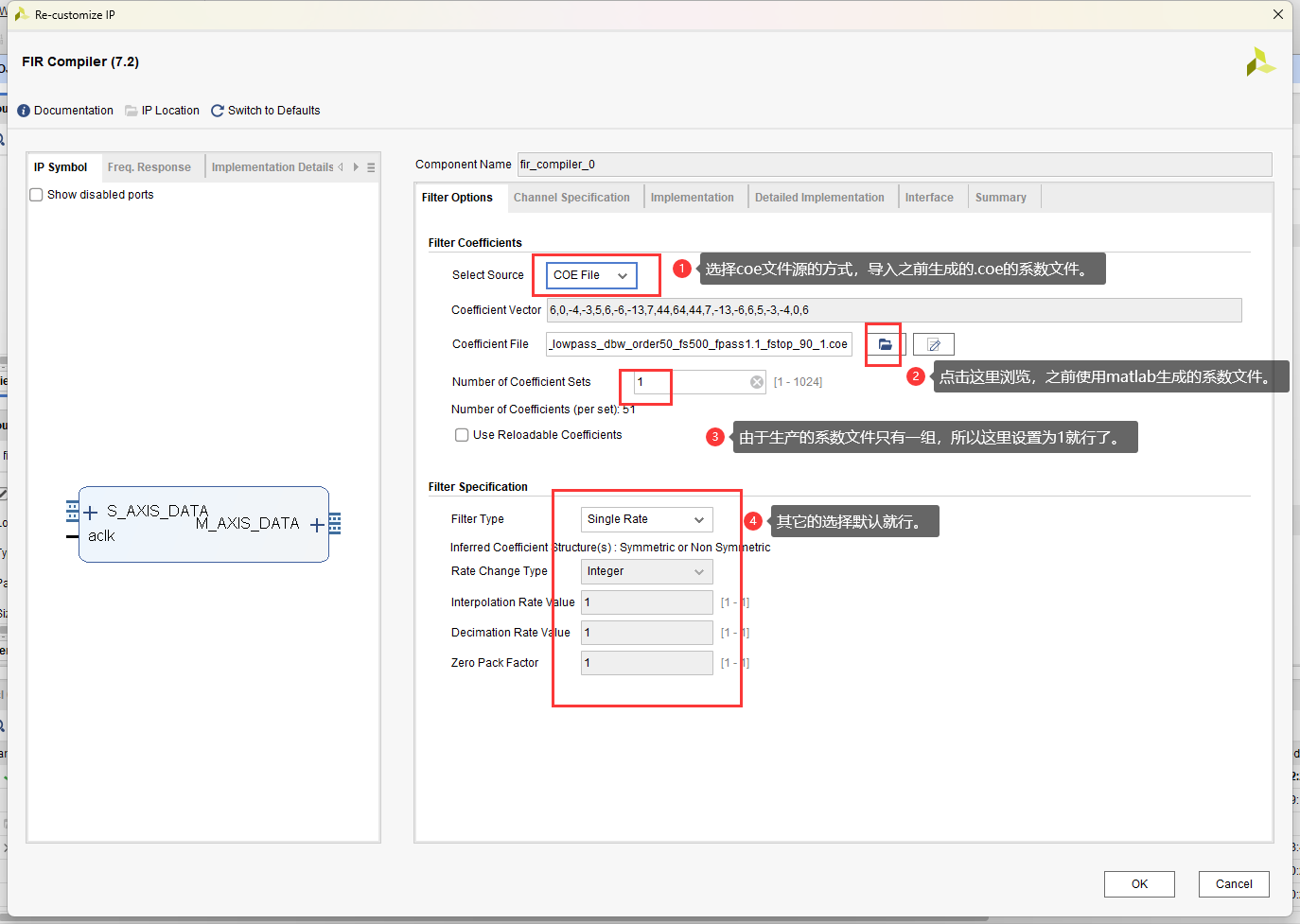

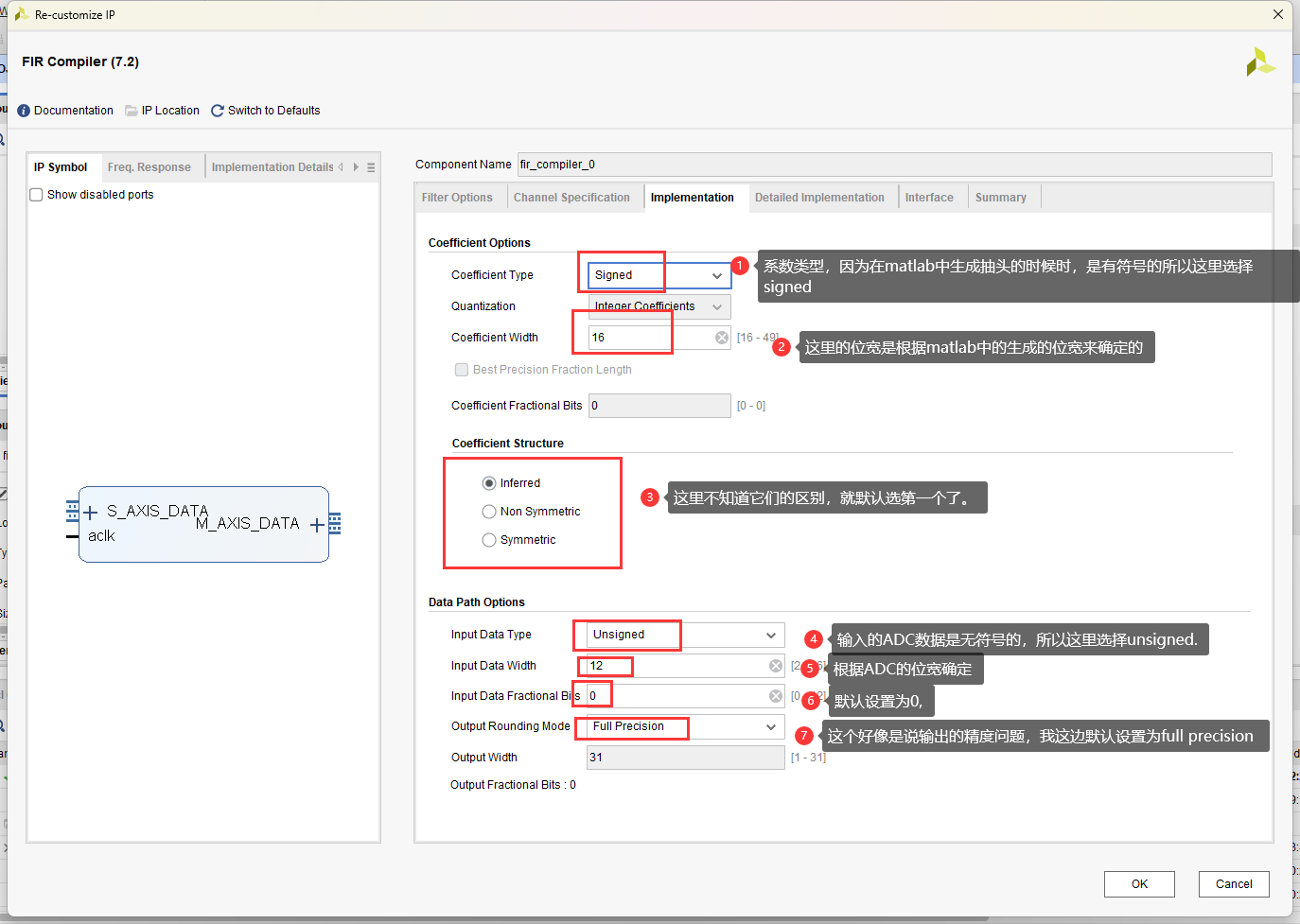

ADC采样率500Mhz,待滤波信号为1Mhz,待滤波信号的位宽为12bit,且是无符号的,系数的位宽是16bit有符号。

1、

2、

3、

4、

5、

6、

7、

8、

9、

10、

11、

写在后面

不忘初心:写博客的主要目的就是记录自己容易忘记的东西,和自己在工作、学习中踩的坑。因为自己在学习或工作中,遇到某个问题,在网上找资料,但资料很多,感觉很多人描述的都是偏理论多一点,实际怎样解决没有怎样详细介绍,对于我这种具体要点什么位置,都需要有教程的那种人来说,非常难受。所以遇到问题,在网上找到解决方式,总结一下,方便后续自己观看。