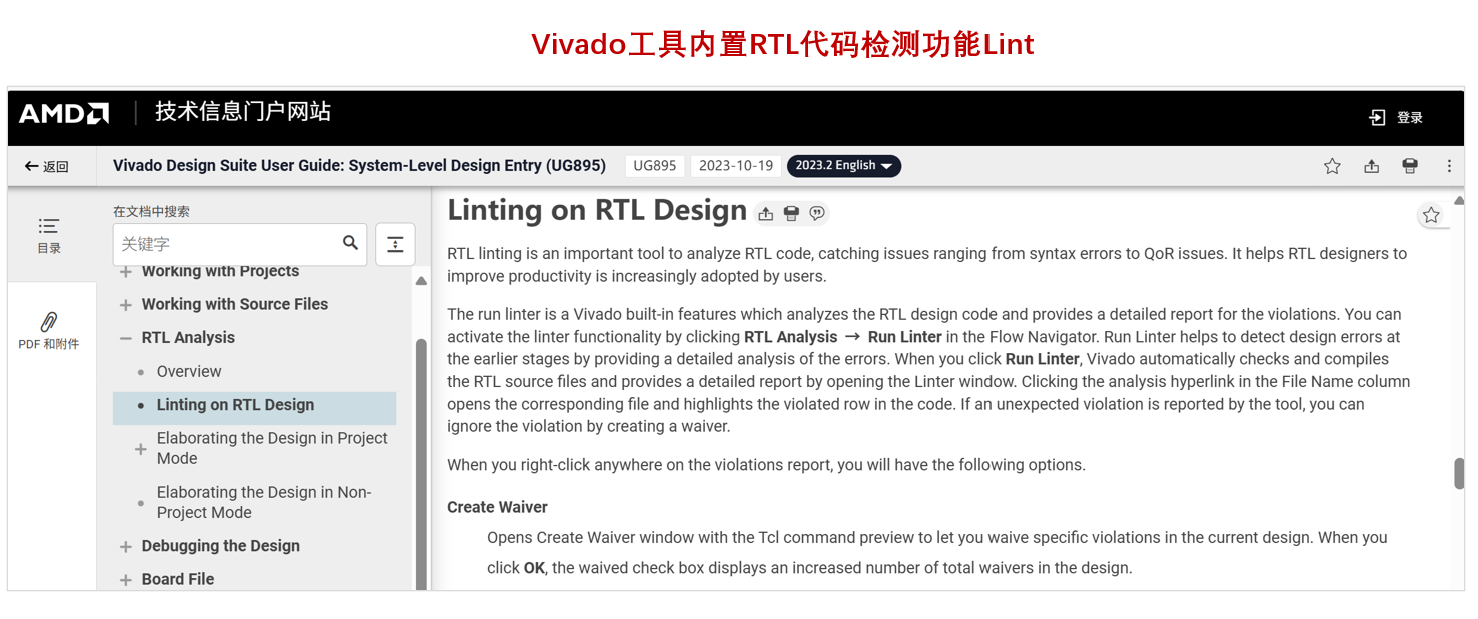

在2023年发布的Vivado 2023.2版本中,首次集成了静态检查功能(Lint工具):对RTL设计代码进行分析,并提供违例行为的详细报告,帮助用户在综合之前,尽早发现设计中的潜在问题。

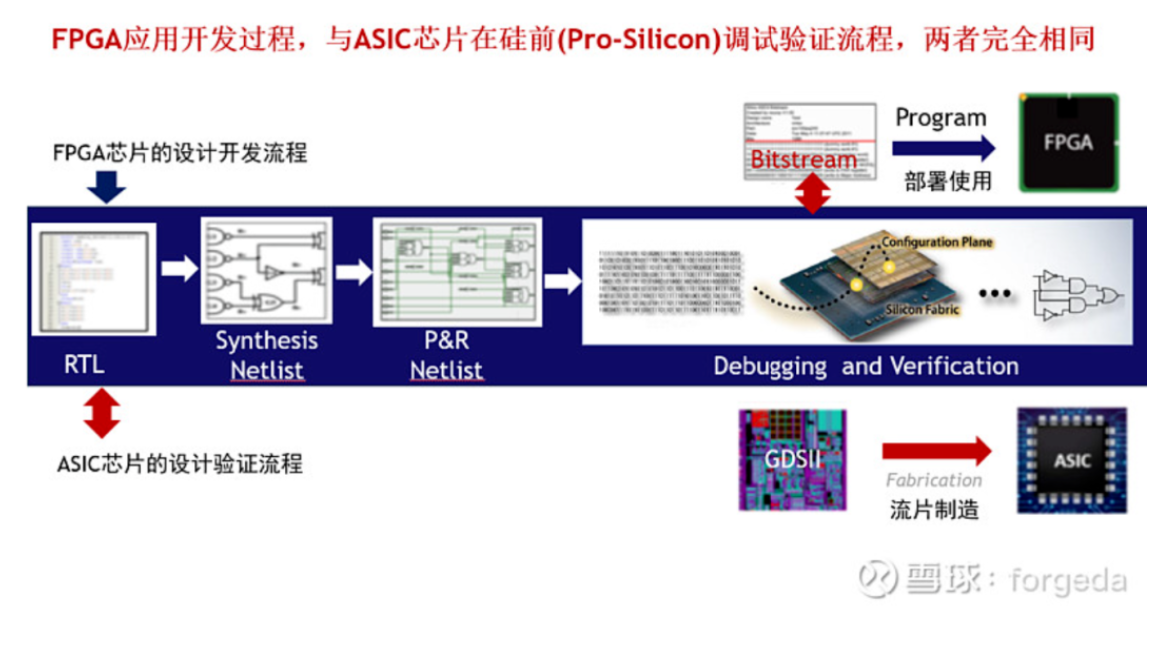

FPGA芯片作为"平民版"ASIC,FPGA应用设计与ASIC的硅前调试验证,拥有完全相同的工作流程。行业龙头赛灵思更是身体力行,将以往那些服务ASIC设计的高级"小"功能,不断引入并逐渐融入整合到自己的专用EDA软件,服务用户日常的FPGA开发设计。

对设计中BUG报告得越晚,意味着用户付出的时间成本等代价就越高。

特别是随着FPGA自身的技术进化,芯片规模越来越大,结构日趋复杂,相应的设计开发任务更为繁琐繁重。

特别是对大容量乃至超大容量的单FPGA来说,用户花费在等待完成布局布线上的时间开销,越来越长。如果RTL代码中的问题,还要像以往那样,只能在综合阶段,甚至布局布线阶段,才能报告错误的话,将会更加低效。

套用EDA硬件辅助验证的行话,用户将无法加速设计左移(Shift-left)

例如,在一个庞大的Vivado工程中,由于错误地定义了latch、reg或wire,可能就需要等待长达1个小时才能收到错误报告。

但是通过在Vivado内置的Linter按钮(Run Linter),至少在用户知晓并熟练使用的这个"理想"层面,n那么用户就能够在RTL代码的早期阶段,发现问题,不会再使之继续"逃逸"到布局布线阶段。

从而可避免那些不必要的时间开销。

新瓶装旧酒,香甜且醇厚

ASIC芯片行业一直在追逐的"加速设计左移"风潮,提供各种专业EDA工具的第三方服务商,无疑是提供助推器的造势者,引领风潮,与客户互相成就。

初代RTL代码检查工具nLint ,并非新鲜事,而是二十年前就面市的大龄"青壮年",其提供商NOVAS公司,2008年被台湾源笙(SpringSoft)公司收购。EDA巨头新思科技在2012年收购源笙公司后,进一步将nLint工具,升级为今天的SpyGlass Lint。

在国产EDA工具这个投资象限,按照"每个工具都值得重新做一遍"的产品定位,仅在Lint 这个单点功能上,包括合见工软,新华章、英诺达、泛联新安和九霄智能等国产EDA新锐,都有专门对标SpyGlass Lint的软件工具。

只不过这股风潮,现在才刮到了FPGA行业龙头赛灵思。

按照使用过SpyGlass Lint工具的用户体验感受,也是FPGA资深工程师的原话来说:

"由于SpyGlass与Vivado IP不兼容,因此在进行仿真前需要使用BlackBox来屏蔽Vivado IP,这一过程相对繁琐。而有了Vivado自带的Lint检查工具,我们能够更便捷地进行语法检查,无需额外的配置与屏蔽步骤,大大提高了设计流程的便利性"。

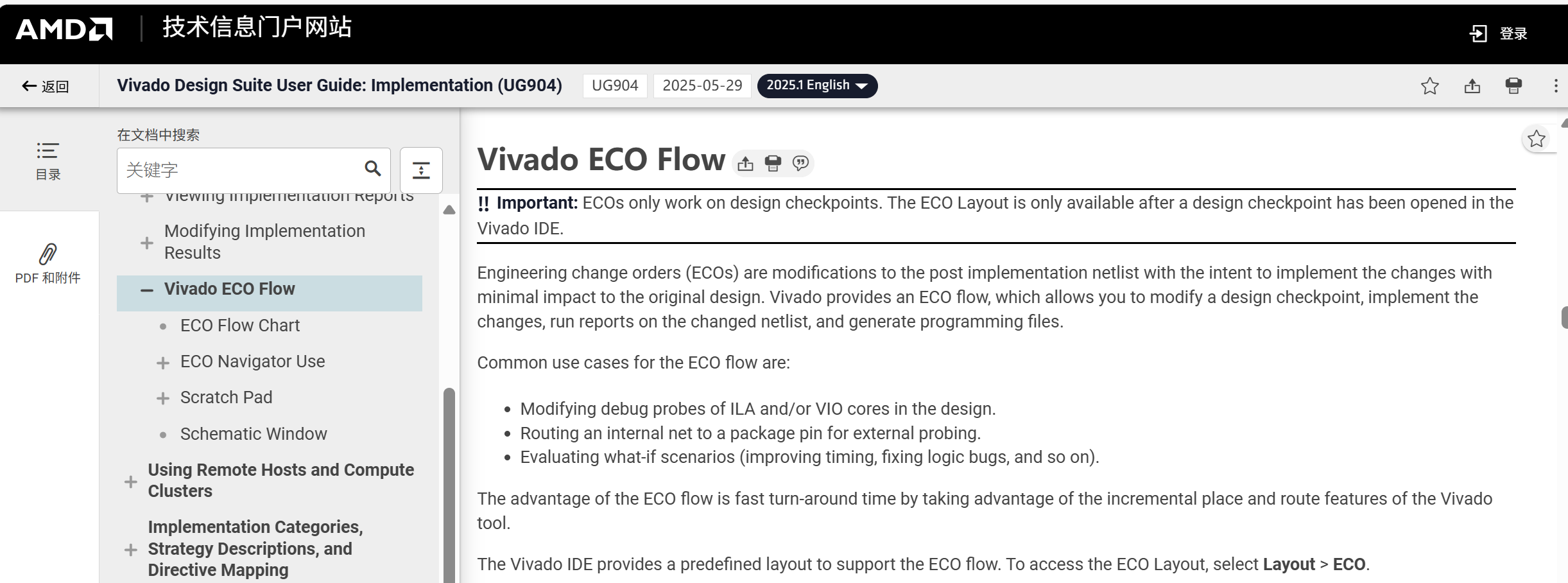

从无到有,不只是静态检查工具Lint,还包括ECO(Engineering Change Order)功能。

同样是源于ASIC设计领域的ECO,在FPGA设计工具中,也同样具备。

用途是用户能够在FPGA应用设计的后期,快速灵活地做小范围修改,不影响已经验证的电路功能和时序。

在Xilinx(AMD)公司在其早期ISE工具集中,用户是通过FPGA Editor工具实现。

但用赛灵思首席工程师Austin Lease的话说,"尽管FPGA Editor工具非常强大,但使用起来也很复杂。因此,通常只有专家级ASIC设计工程师才会使用到这个编辑器工具"(摘自新思科技《FPGA原型设计最佳实践》一文中的"FPGA芯片现状与EDA工具",2011)。

目前,该功能已集成到Vivado中,可以直接在界面或者通过Tcl命令完成。用户能够对电路节点进行精细控制和修改,就像生物医药领域的"基因剪刀手"一样使用。

从以前的专家级EDA硬件辅助验证平台,扩展到日常FPGA应用设计也够使用,渐成趋势。

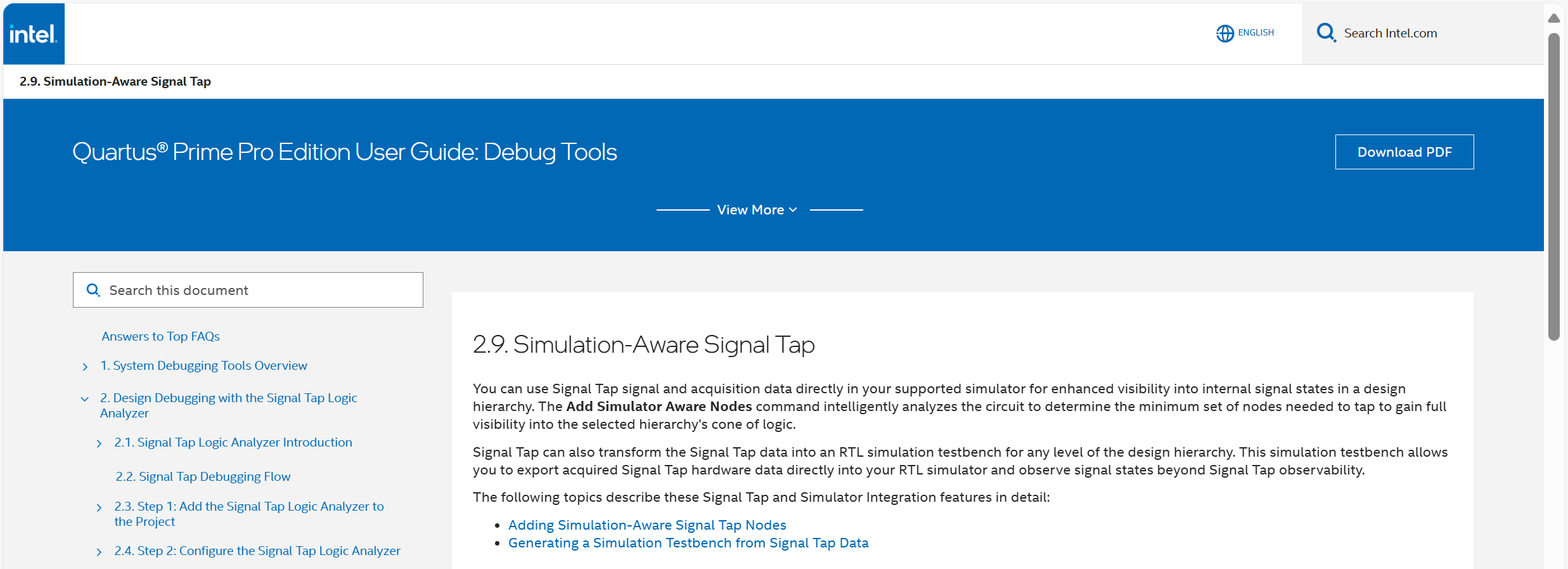

除了AMD(Xilinx),行业排名第二的Altera,2024年新增名为"Simulation-Aware Signal Tap",简单说来,就是将Signal Tap在线抓取的信号数据,直接与仿真器关联,推算出所有的寄存器和线网的值。

可观测能力可提升数十倍。

类似的调试验证能力,从最早只有先进的硬件仿真平台Zebu才提供,逐渐成为行业标配,在2016年,成为新思科技推出其高性能原型验证系统(HAPS80)时,着重宣传的亮点之一,现已成为行业标配,是各家公司提供EDA硬件辅助验证服务,硬件仿真和原型系统两大行业产品的基础功能。

以往只服务ASIC芯片设计领域,隐藏在那些"高大上"的复杂大软件/高端设备的FPGA调试验证功能,正以软硬件解耦合、软件再次解耦合,以润物细无声的方式,逐步引入到FPGA厂商的设计工具集合中。

更好应对FPGA容量规模越来越大,应用开发设计更趋复杂繁琐的趋势。

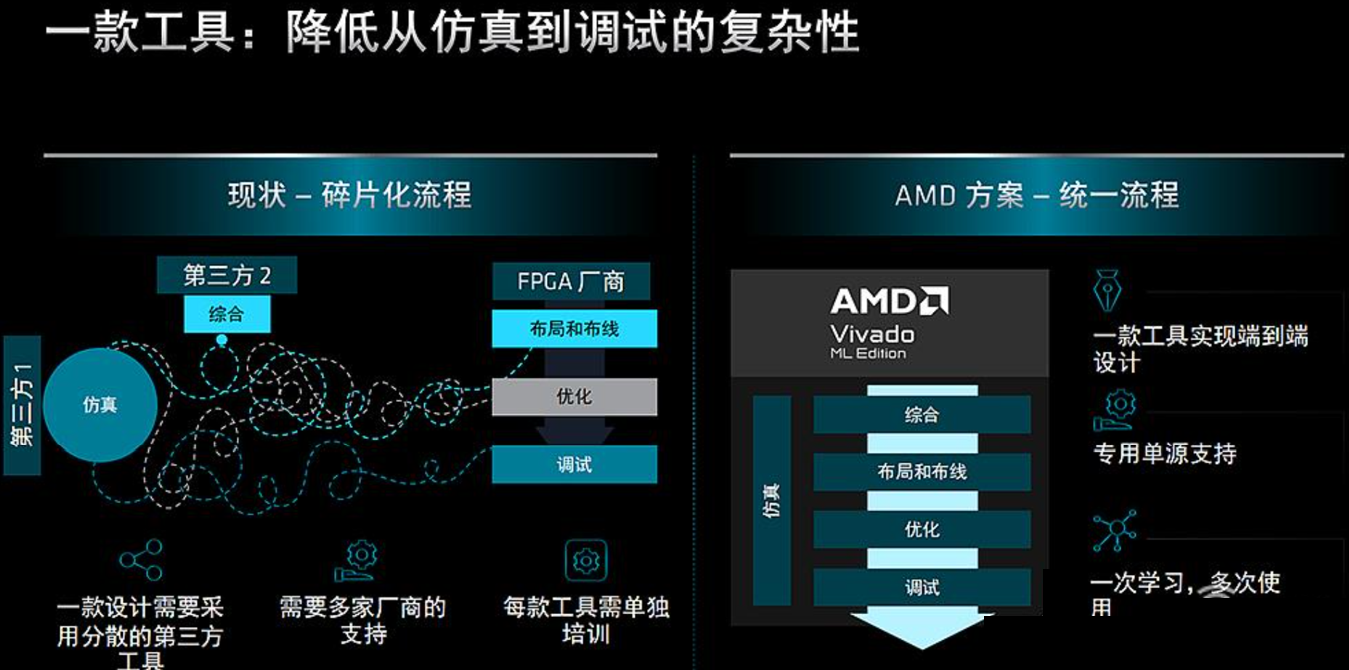

2024年,AMD(Xilinx)在发布UltraScale+ Spartan系列FPGA时,豪言要"一款工具,统一流程",降低从仿真到调试的复杂性。传达的一个明确的信号是,异构融合化的FPGA、越来越ASIC化,尝试正在自家的EDA软件上,铺就一条属于自己的道路。

FPGA龙头厂商和第三方EDA工具提供商的"互别苗头"

就像GPU领域的CUDA软件那样,在设计工具中,通过软件和底层硬件的协同,使客户获得生产力提升、增强用户黏性,并据此构筑更高的技术护城河。

走在异构计算、硬件加速最前沿,也是代表了FPGA最先进调试验证技术,集这三大特点为一体的EDA硬件辅助验证工具,从两大仿真加速设备的演进路线上看,不断为应对电路设计复杂性带来的,不可避免的后端布局布线时间压力等技术需求,越来越先进的产品组合,同样是为用户的硬件设计和软件设计,提供"生产力优势"。

EDA三巨头之一的西门子,在2021年发布的"FPGA 功能验证趋势报告"中,曾表示"FPGA自身的技术进步,以及大量第三方IP核的集成使用,使得今天的FPGA应用设计,正被迫经历20年前,ASIC芯片设计所遇到的调试验证挑战"。

Xilinx、Altera这两大FPGA行业龙头,包括航天军工行业领头羊的微芯科技(Microsemi),通过在开发套件中引入ASIC设计使用的"新"功能,正在作为其新的核心竞争力。

目前国产替代浪潮中的几个爆款型号,硬件对应的逻辑单元数在数十万量级,而最新一代FPGA单芯片的容量规模,已经高达数千万逻辑单元。

如果既有"萧规曹随"产品理念继续保持不变,即便在专用EDA软件上,能够做得像赛灵思Vivado一样优秀或青出于蓝(何况还很难做到),那又会怎么样?

借用雪友@三心五意 的话说,"Vivado安装包要好几个G,多看一眼都反胃"!亲,你说的是"轻装版",full版本的话,可是好几百G呢。

全文完,感谢您的耐心阅读