上一篇在这里最近两个电路调试的经历与总结(一)

第二个电路说是调试,其实算是分析。因为知道我最近在看《你好,放大器》这本书,所以就正好找上我一起讨论了。

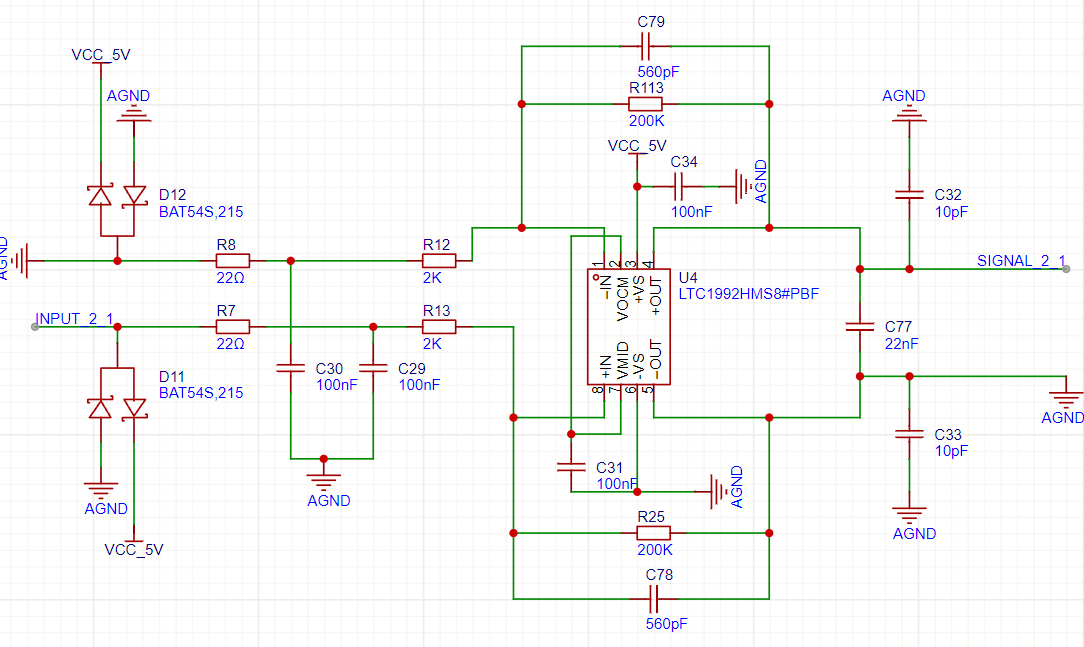

他们给我发来了这样一个电路,遇到的问题是,负半周有一部分被截止了,其他都是正确的。

这前半部分看着是一个单端转差分,但是后面怎么把差分输出信号的一端接地了......

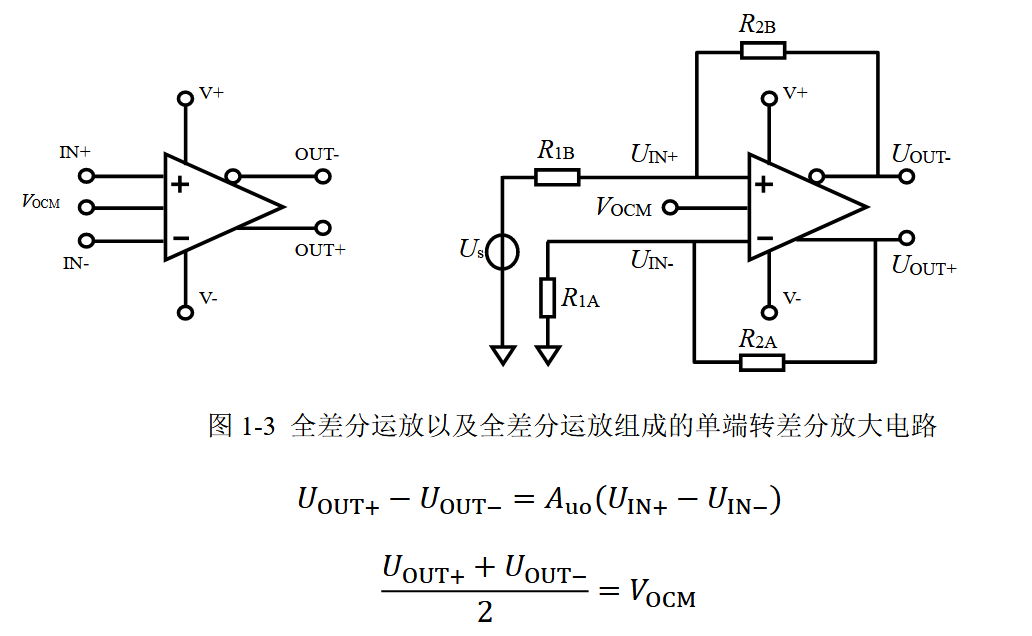

他们给出的解释是,试图通过这个方法将输出信号拉高,因为根据差分运放的定义是:

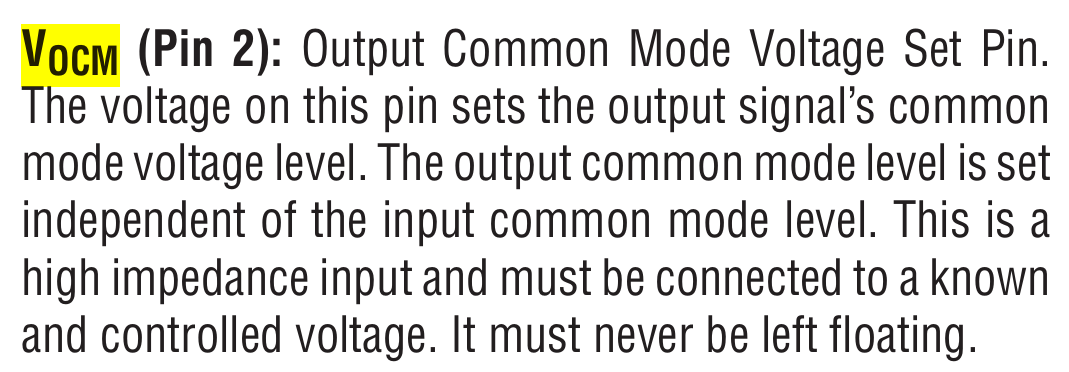

也可以看看这个运放手册上对VOCM的定义:

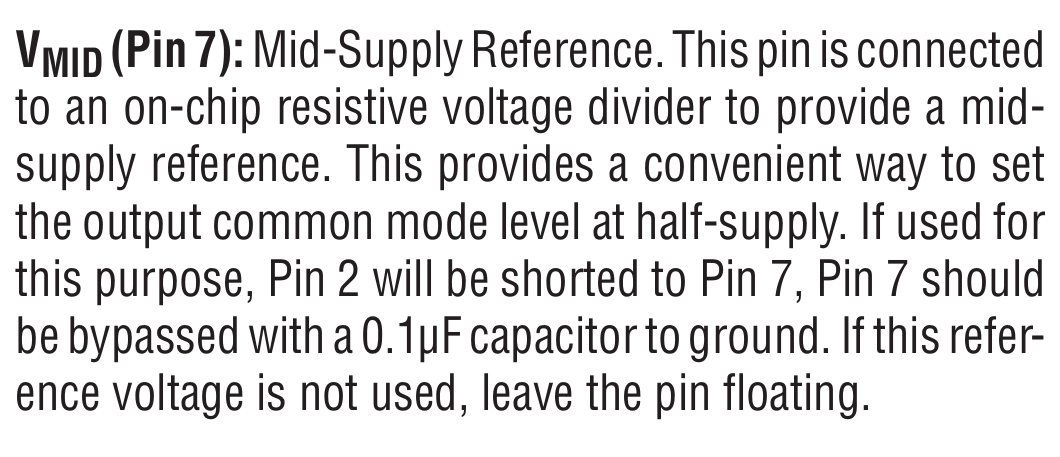

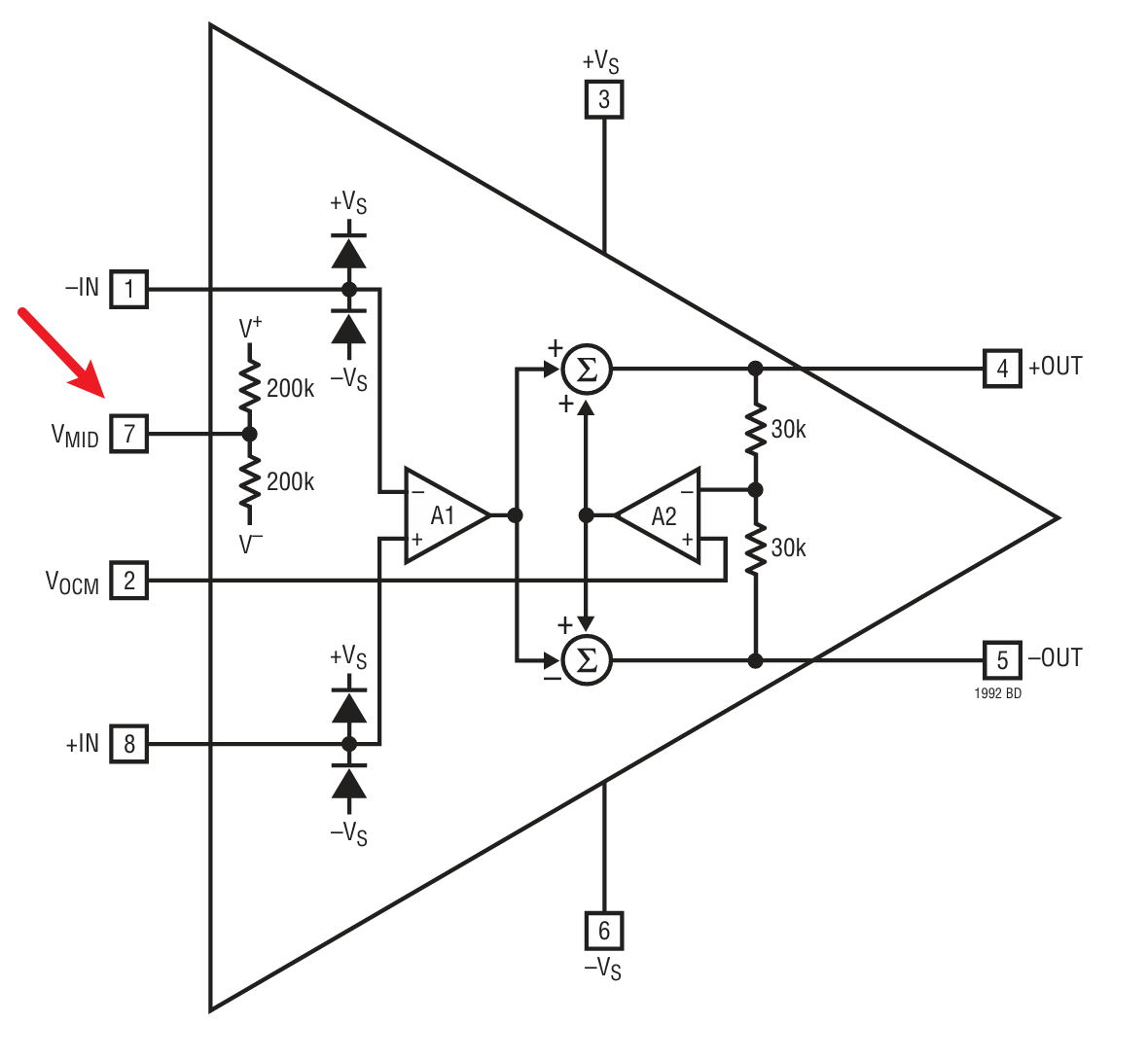

这里多了一个VMID电压,它的定义是:

根据参考手册的定义,也就是说只要将Pin2和Pin7连接在一起,引脚7再用一个0.1uF的电容接地,即可得到电源的一半供给VOCM。按照上图也确实是这个的接法,那么VOCM=2.5V。下图为运放内部结构,VMID就是正负电压的分压得到的值。

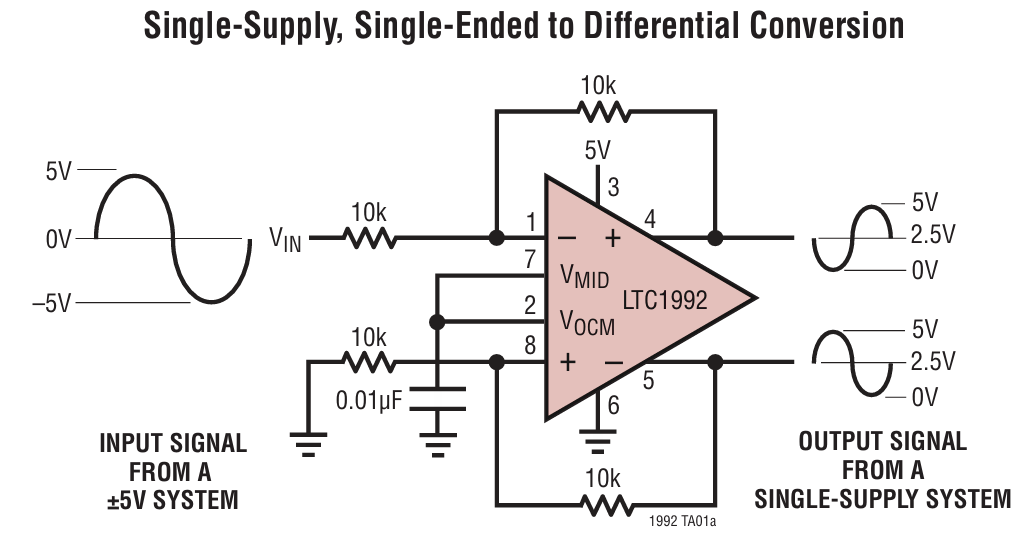

其实上图他们画的原理图,抛开将Vout-接地,其他电路基本参照数据手册的这张图:

一个单电源供电,单端转差分的设计。

我初步推测,这个接地肯定是影响了运放内部的电路输出的。因为我的理解是:没加入地之前,这两个端口输出就是运放内部电路转换后的结果,但是加入了这个地,那就相当于外部介入了这个运放的工作,从而导致输出不对。

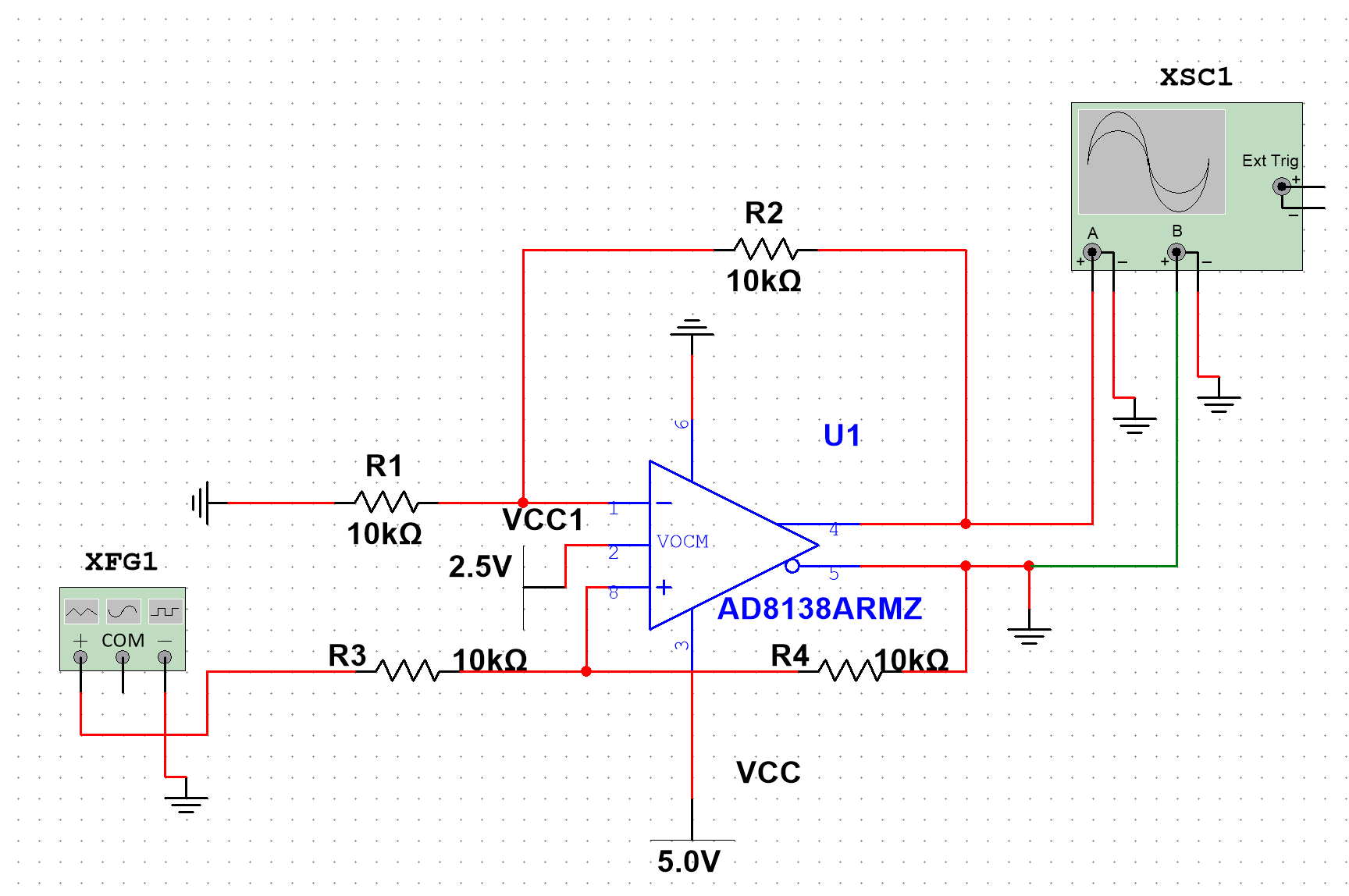

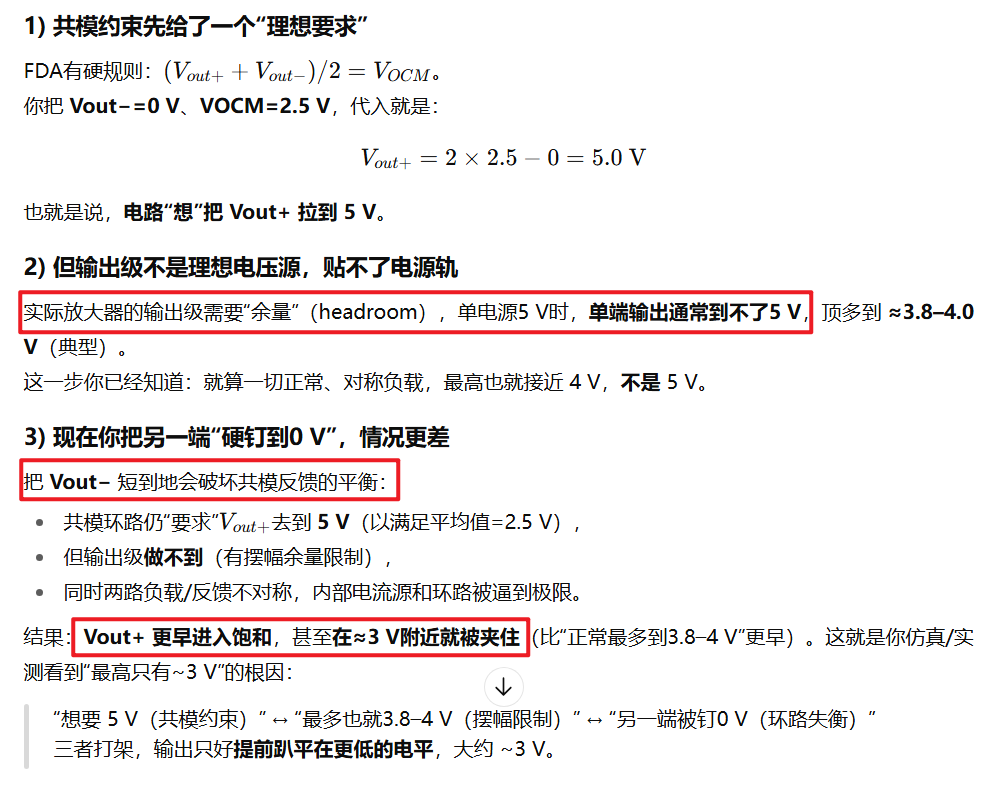

这里为了验证这个电路,我用Multsim搭了一个差分运放的电路,如下图。由于Multsim里面并没有这个运放,所以我选择了我以前用过的AD8138运放替代,反正这里只是探究原理(我师兄说ADI公司有个专门的仿真,但是当时为了尽快解决问题,就没有专门去下,后续可以研究研究)。这里我是直接按照上图搭建了,VOCM的值我直接给了2.5V以此来模拟实际电路。输入给的是Vp为1.5V、频率为100Hz的正弦波。

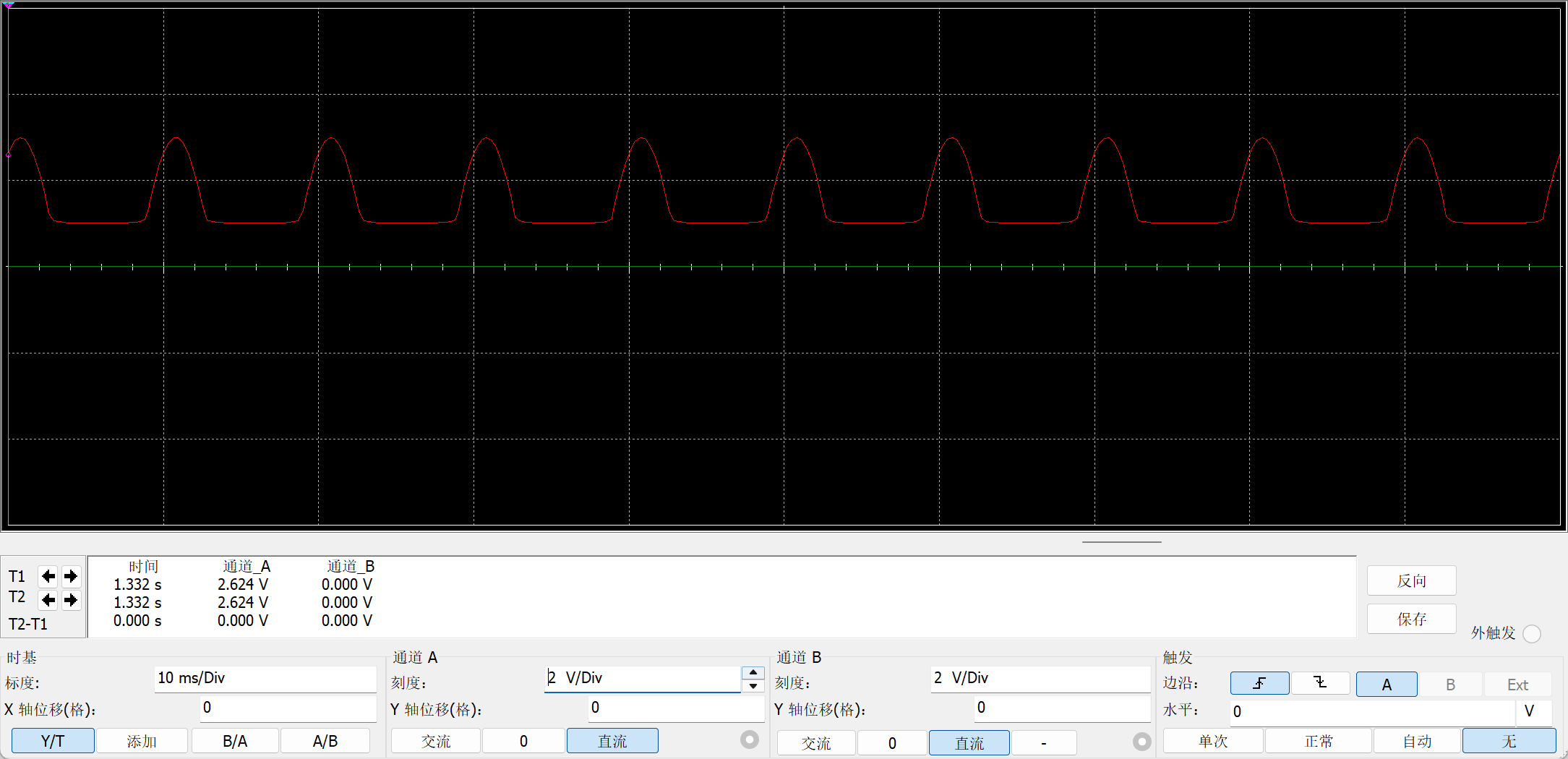

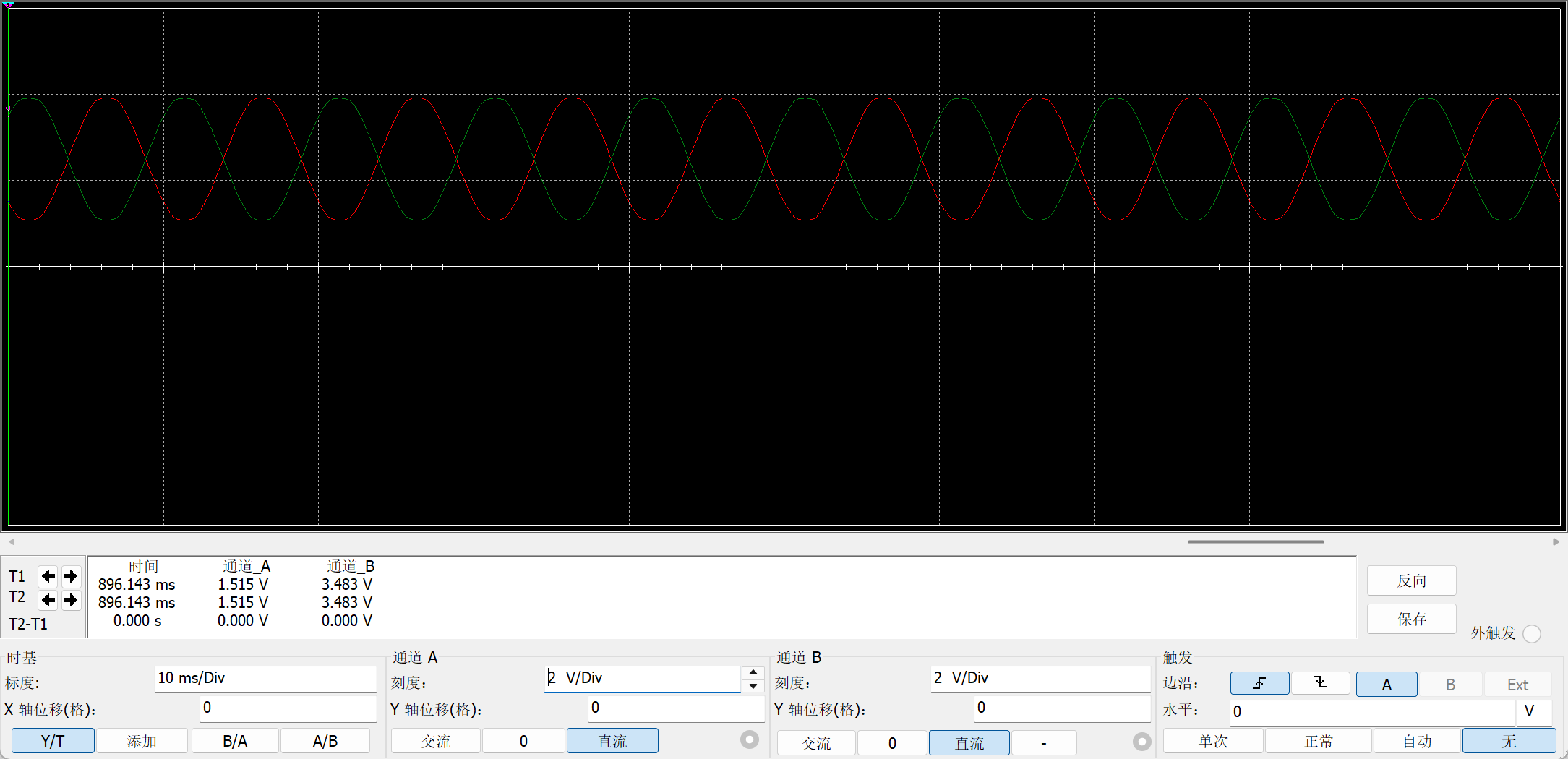

那么这样的一个电路仿真出来的结果是这样的:

很显然负半周是截断了的,当我把Vout-的地取走后,输出就正常了。

所以结论也就出来了:他们的原理图画错了,实际的输出引脚不能直接接地。

后续是他们为了赶进度直接将输入信号飞线飞到ADC了,先将就这样用着,但是我这里想思考一下这种现象出现的原因。目前的推断是:直流偏置减少了,导致信号负半周部分被截止。

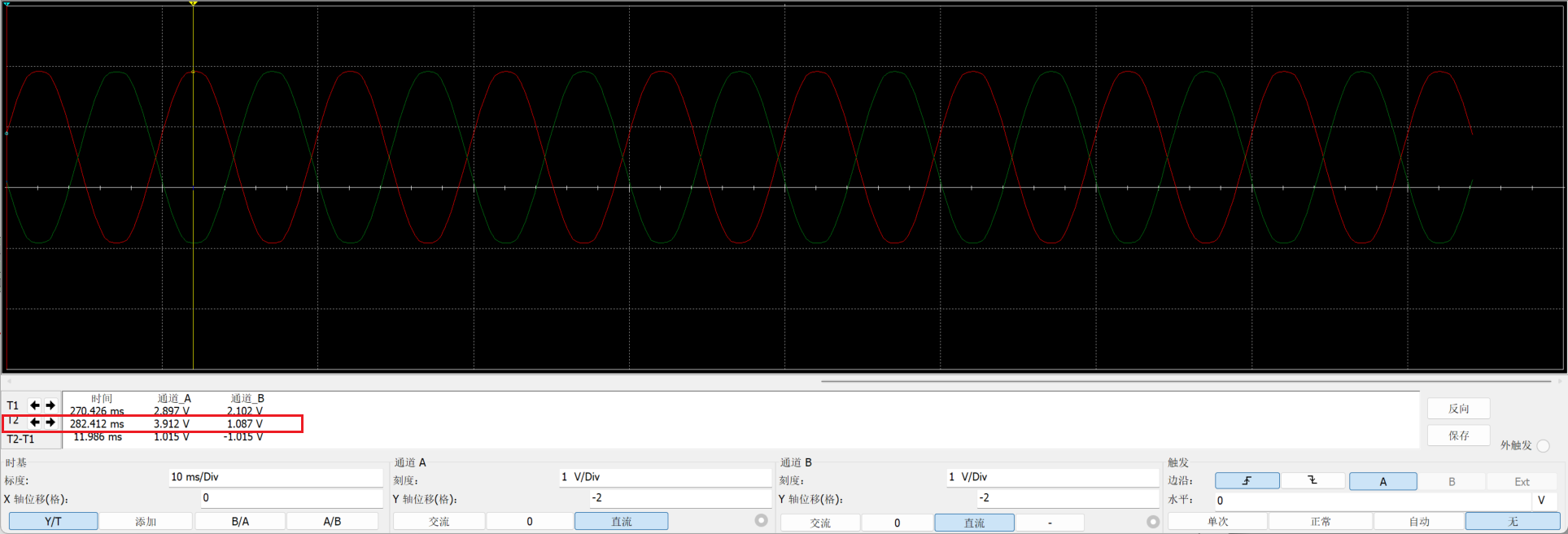

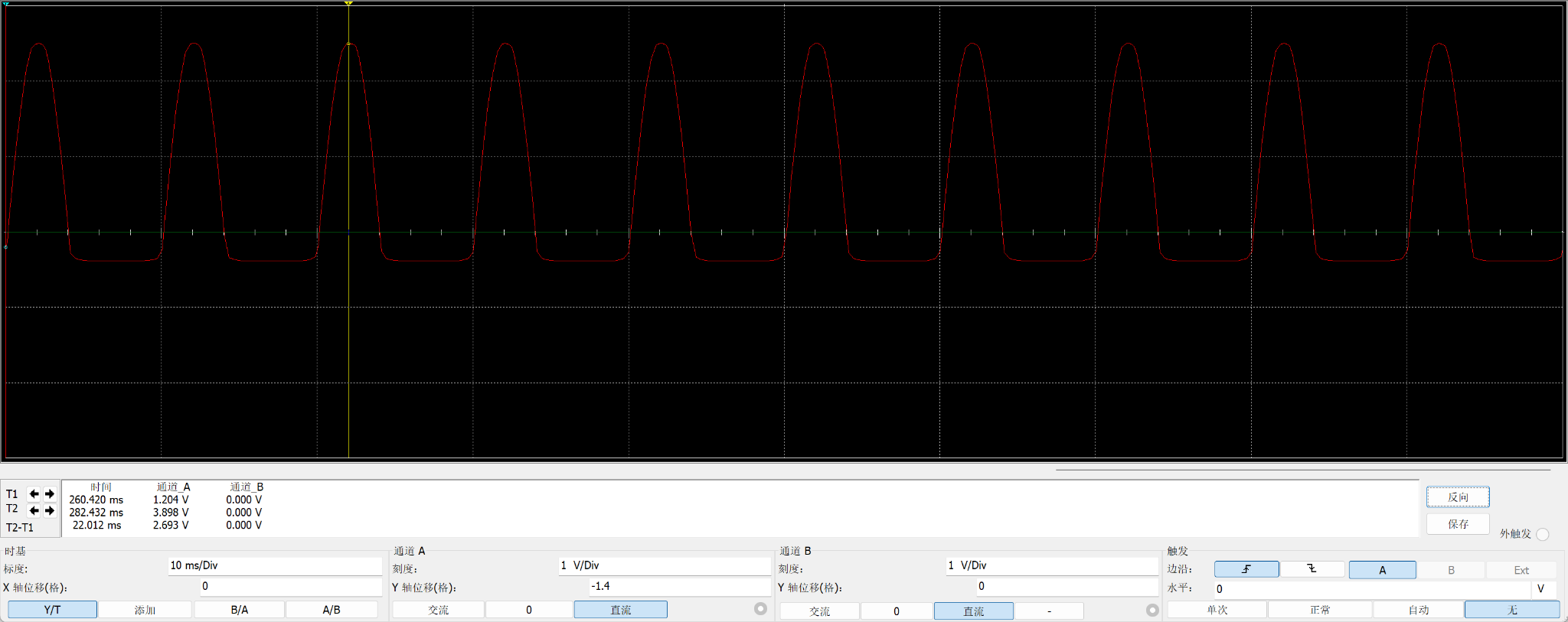

首先看一下正常的原理图仿真。

看到输出最高为3.9V,最低为1V。按照Vocm的公式来看,正确。

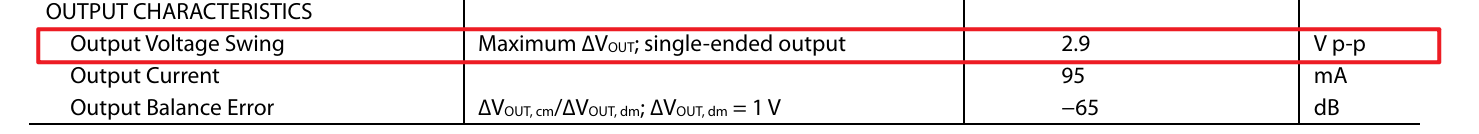

但是在单电源的情况下,输出达到3.9V是否合理呢?这得看一下数据手册。在单电源5V供电,Vocm为2.5V条件下给出的数据如下

数据手册上写的是单端输出电压摆幅典型值为2.9V。

单端输出是围绕Vocm对称摆动的,由于Vocm为2.5V,那么输出信号的摆幅1.45V,输出应该为1.05V~3.95V之间。那仿真的数据完全没有问题,至少理论上是可以的。

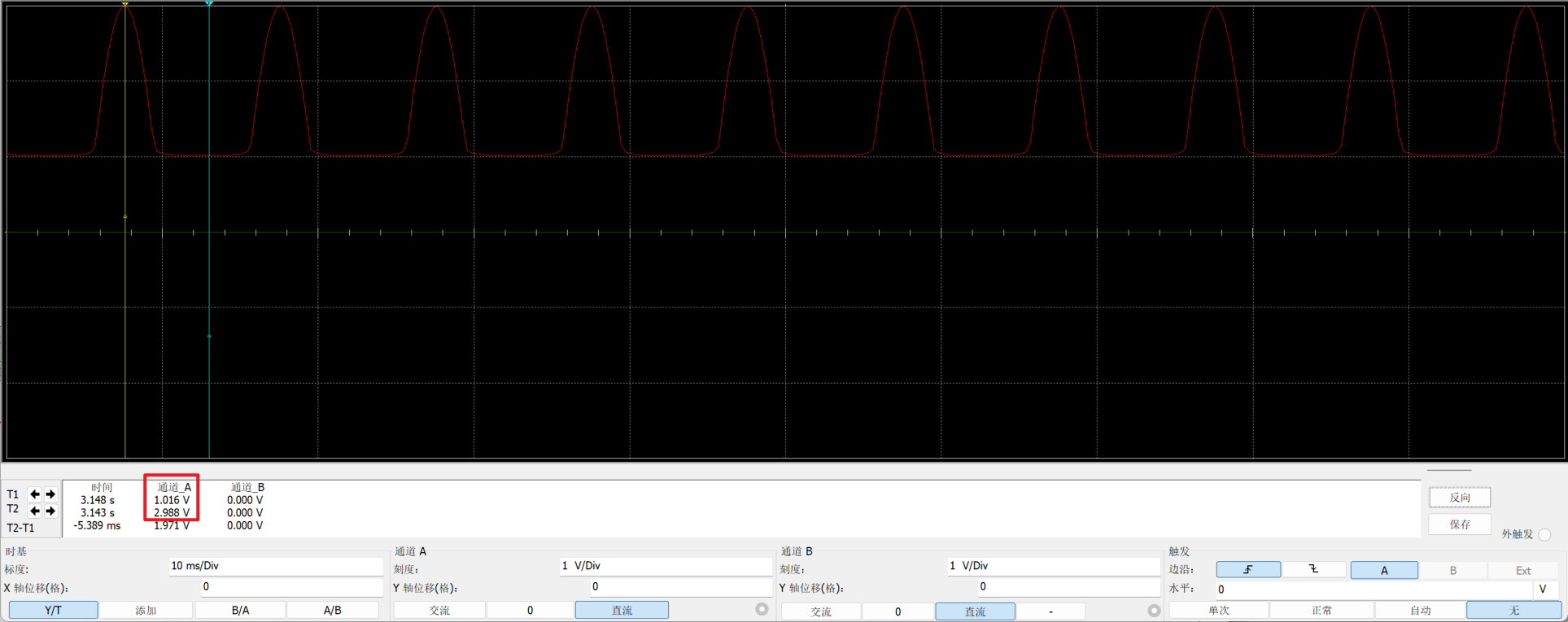

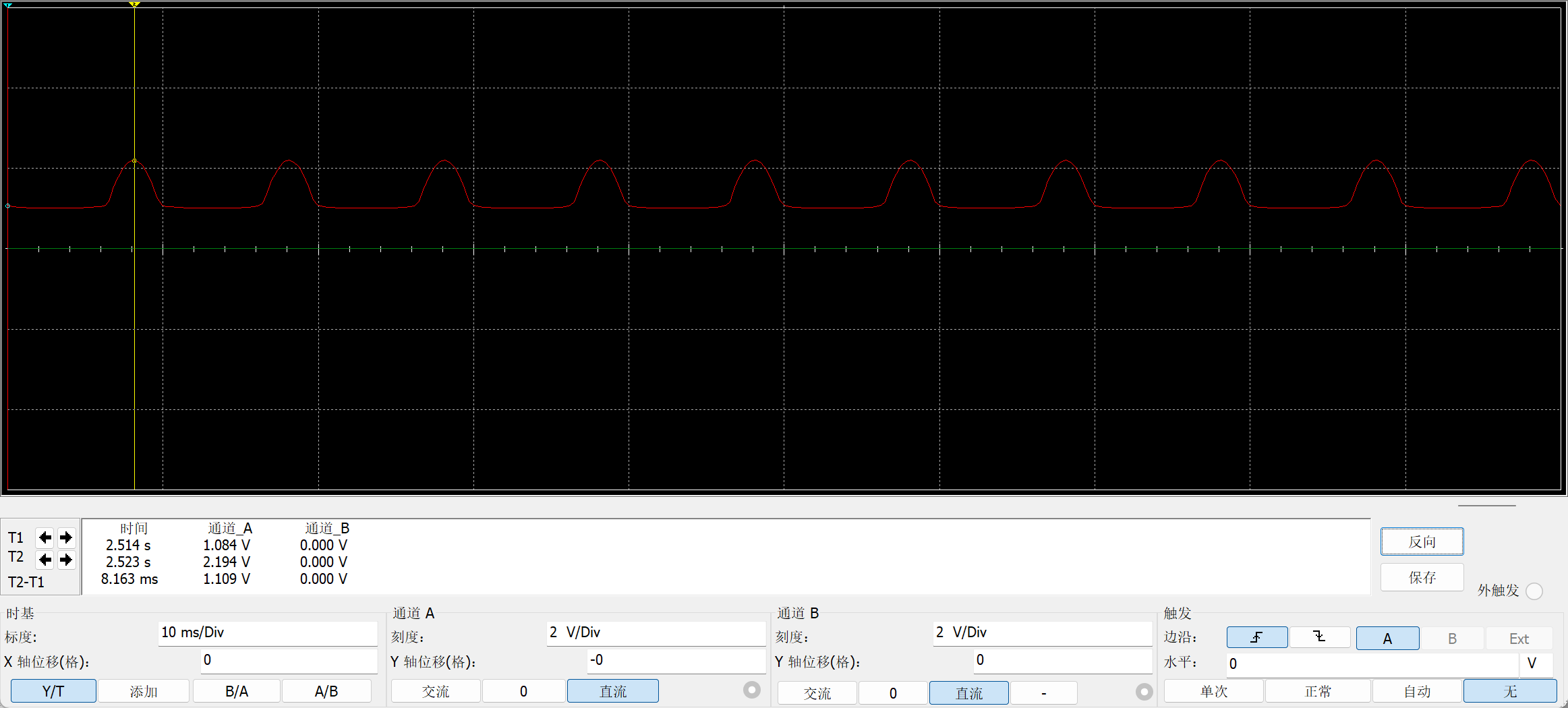

接着看回单端输出接地的波形,如下图,输出在1V~3V之间。

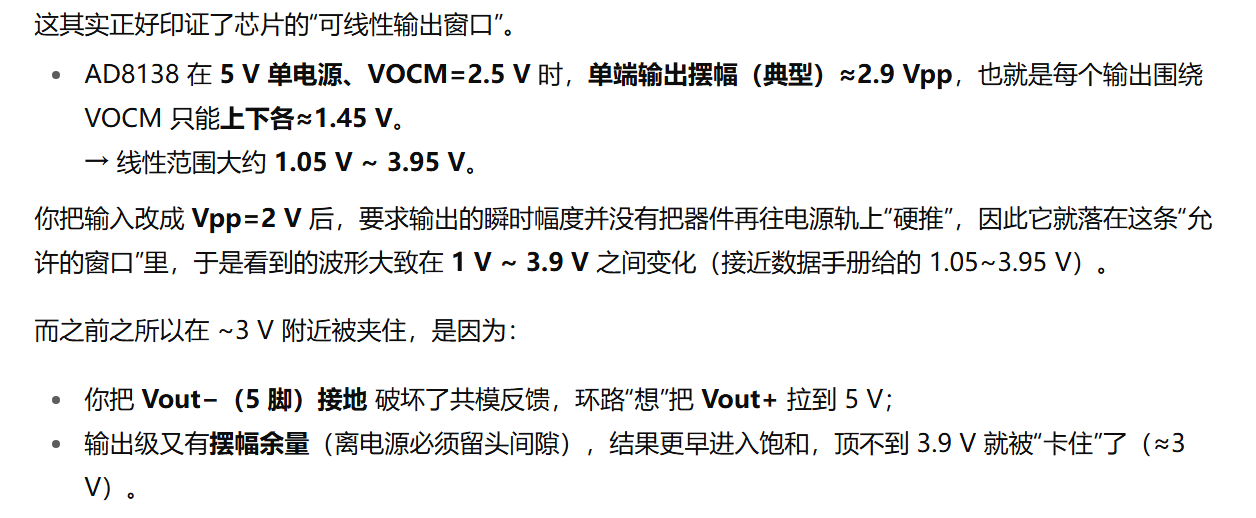

由于我的能力实在有效,这一段只有请求AI的帮助了

所以原来不是单纯的"负半周被阶段"。

这里解释一下共模反馈平衡:在全差分放大器里,除了决定差分增益的那条主反馈环路外,还有一条共模反馈环路,它实时测量两路输出的平均值并强制把这个平均值拉到VOCM。当这条环路正常工作且两路负载/反馈对称时,输出就会呈现围绕VOCM等幅、反相的对称摆动。

感觉还是挺有道理的。就这样吧。

诶我又发现当我把输入Vp调到2V时,输出信号居然又回到了1V~3.9V之间

AI的答复是:

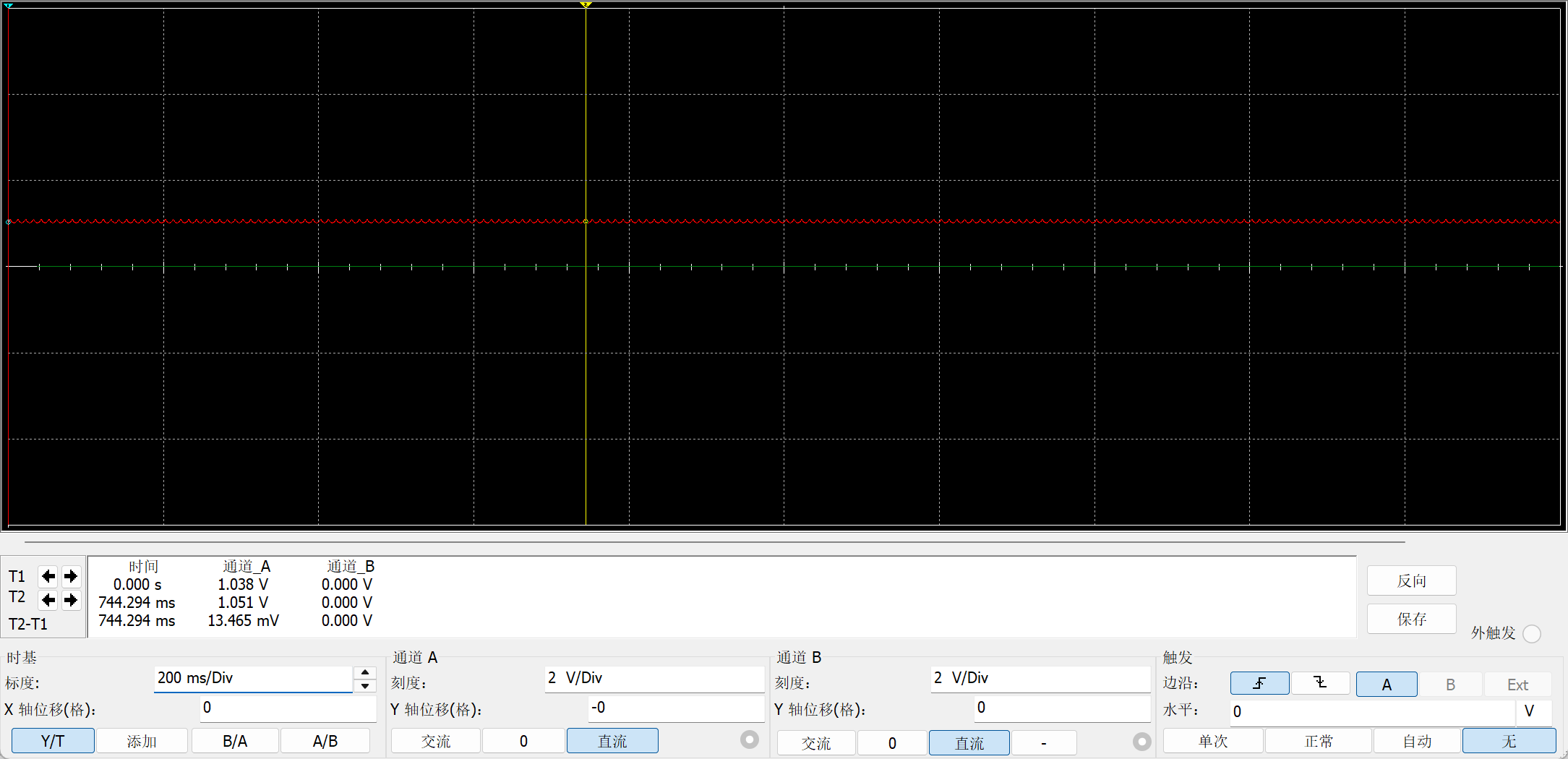

为了验证AI的回答,我把Vp调到0.5V,得到如下的结果

输出仅在1V左右波动。

不能调到0.5V,数据手册上给出单电源供电时,输入电压范围应为1V~3.8V。现在挑一个1.1V看看

在1V~2.1V之间波动

总结:差分运放输出的两端,不能加地。