介绍

去年我做了一个简单的矢量网络用于测量微波电路的 S 参数的分析仪,我正在制作 家。 预算非常少,主要是低成本的概念验证自制 VNA。

如果您不知道什么是矢量网络分析仪,我建议您阅读先看上一篇文章,但简而言之,它是一个测试设备,可用于测量电路的发射功率和反射功率的幅度和相位。 为 示例从天线反射回来的功率量在其工作时应较低 频率。

虽然它有效,但我可以用它来测量一个和两个端口的 S 参数测量精度不是很好。一个端口测量效果合理好吧,但两个端口测量精度的最大问题是泄漏测试端口之间。为了校准仪器,我不得不使用奇异的16 项校准,可以补偿之间的不同泄漏路径接收器通道。

端口之间缺乏隔离是最大的问题,但也有许多其他较小的问题:

-

接收器噪声系数非常高,因为混频器之前没有任何放大。噪声系数增加导致测量噪音大,动态范围减小。

-

接收器的线性度不是很好。这部分是由于坏的选择 IF 放大器,部分原因是我使用了没有巴伦。建议使用差分输入驱动混频器,但是宽带巴伦太贵了。用其他输入驱动混频器端接是可能的,但线性度、转换增益和噪声系数 遭受。

-

定向耦合器集成在 PCB 上,为了节省 PCB 面积,我制作了它们尽可能小。在低频下,耦合非常低,并且接收器的信噪比不是很好。在高频下耦合器的方向性和匹配开始恶化。

-

理论上,即使匹配、方向性或泄漏很高,它们也可以通过校准进行校正。实际上存在一定量的漂移和仪器中的噪声导致矢量纠错不精确并且结果中会出现一定数量的误差。有足够的漂移,非线性和噪声导致测量中存在显着误差即使在校准后也能得到结果。

-

微控制器的速度不够快,无法进行任何信号处理,并且所有信号处理需要在 PC 上完成。这需要传输原始ADC 值通过 USB 连接到 PC 进行处理。虽然 PC 应该足够快来处理样本而不会延迟下一次测量,实际上我的代码是用 Python 编写的,但不是足够快,可以在不延迟测量的情况下完成所有信号处理。微控制器也忙于读取 ADC,没有时间做同时做任何其他事情。

总的来说,有足够的改进空间,但我对此不满意董事会并决定制作一个改进版本来尝试解决问题尽可能地点,同时仍然保持低成本。

单接收器 VNA

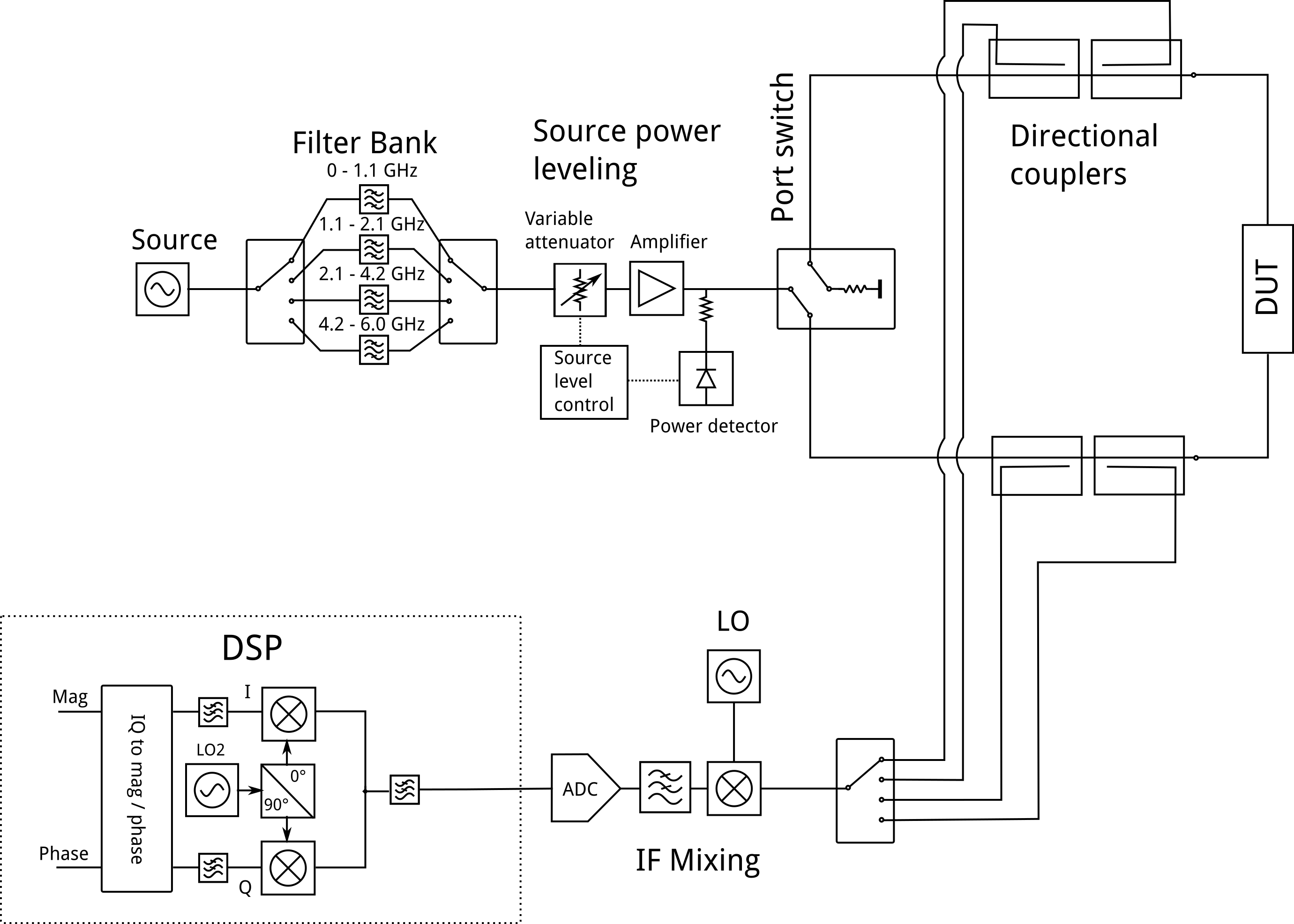

以前 VNA 版本的框图。

以上是之前版本的 VNA 框图。商业 VNA使用四个独立的接收器以及它们自己的混频器和 ADC,以最大限度地提高接收器通道之间的隔离并提高测量速度。我也想使用四个接收器,但现实是乘以接收器成本乘以四对于我的预算来说太高了。

接收器通道之间的隔离可以通过改进来改善接收器 SP4T 开关的隔离。在我之前的 VNA 上,我使用了单PE42441 SP4T 交换机。这是非常便宜,但隔离度对于 VNA 使用来说还不够好。商业 VNA 有接收器之间的隔离度至少超过 100 dB,但该开关只有40 GHz 时的 6 dB 隔离度。

VNA 的隔离度应远高于被测组件的隔离度测试过,例如无法测量接收器开关的隔离度在我的 VNA 的先前版本上,因为接收器通道之间的泄漏是与通过被测开关的信号的顺序相同。 这是 测试设备的一个普遍问题:它的性能应该优于被测设备。

除了接收器SP4T开关外,端口开关还有一个SP2T隔离度不够好的开关。源开关是PE42423的,已上市在 43 GHz 时具有 6 dB 的出色隔离度。虽然它非常好单个 SP2T 交换机的隔离度不足以用于 VNA。

在单个 PCB 上实现超过 100 dB 的隔离是困难的,而且这就是为什么专业的射频测试设备将每个系统相互屏蔽的原因。如果在同一个 PCB 上制作多个块,则会放置一个铣削的铝外壳PCB 顶部,将块彼此隔离开来,与环境隔离。铝块还可以用作散热器,减少温度漂移仪器。但是,我买不起任何定制的铣削铝件,并且必须在没有它们的情况下进行管理。

然而,我确实在接收器周围放置了一个屏蔽层,可以使用夹子连接以便在需要时可以将其移除。屏蔽源、开关、耦合器、FPGA和电源也是一个不错的选择,但它需要PCB 上的空间太大,所以我决定把它们排除在外。

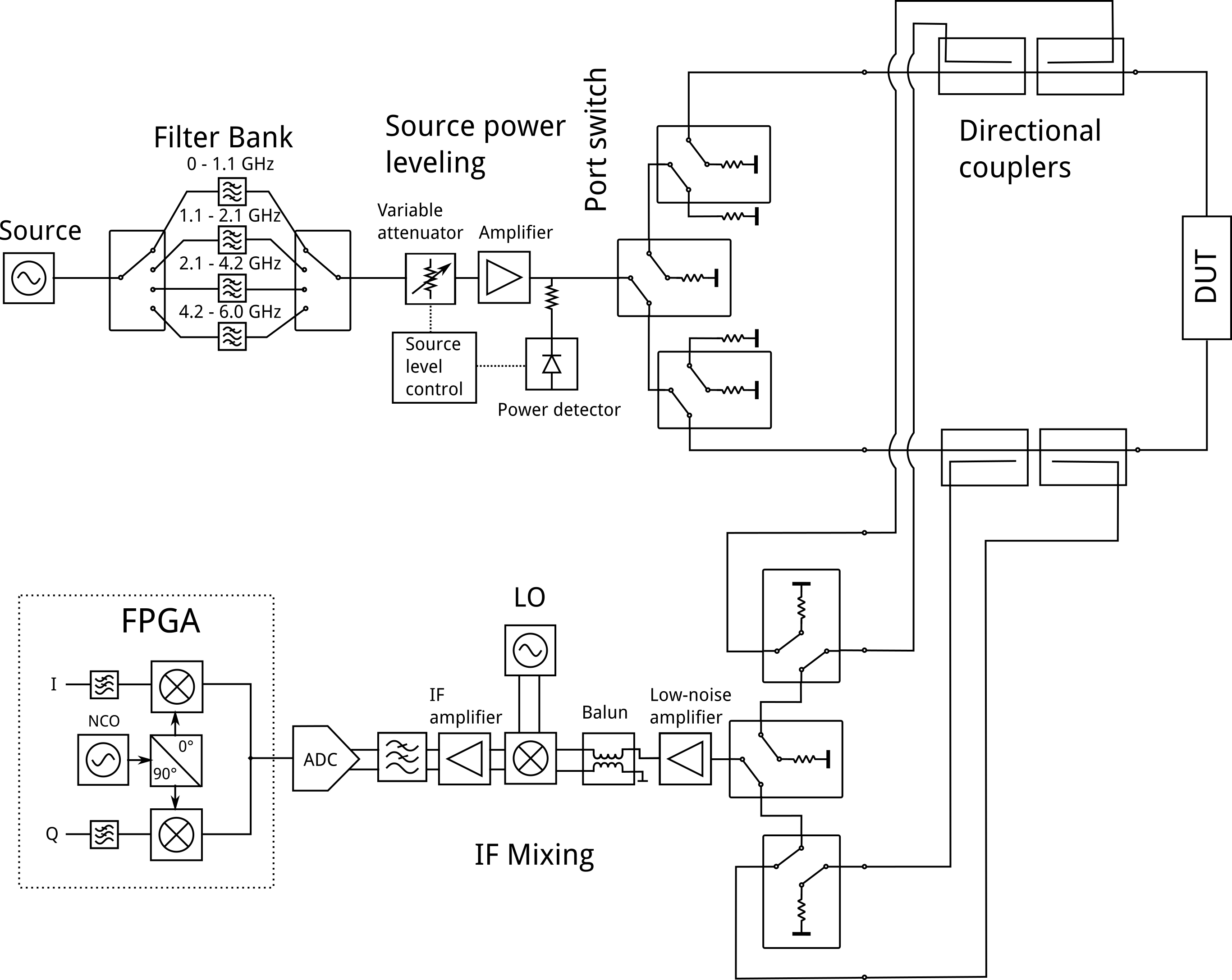

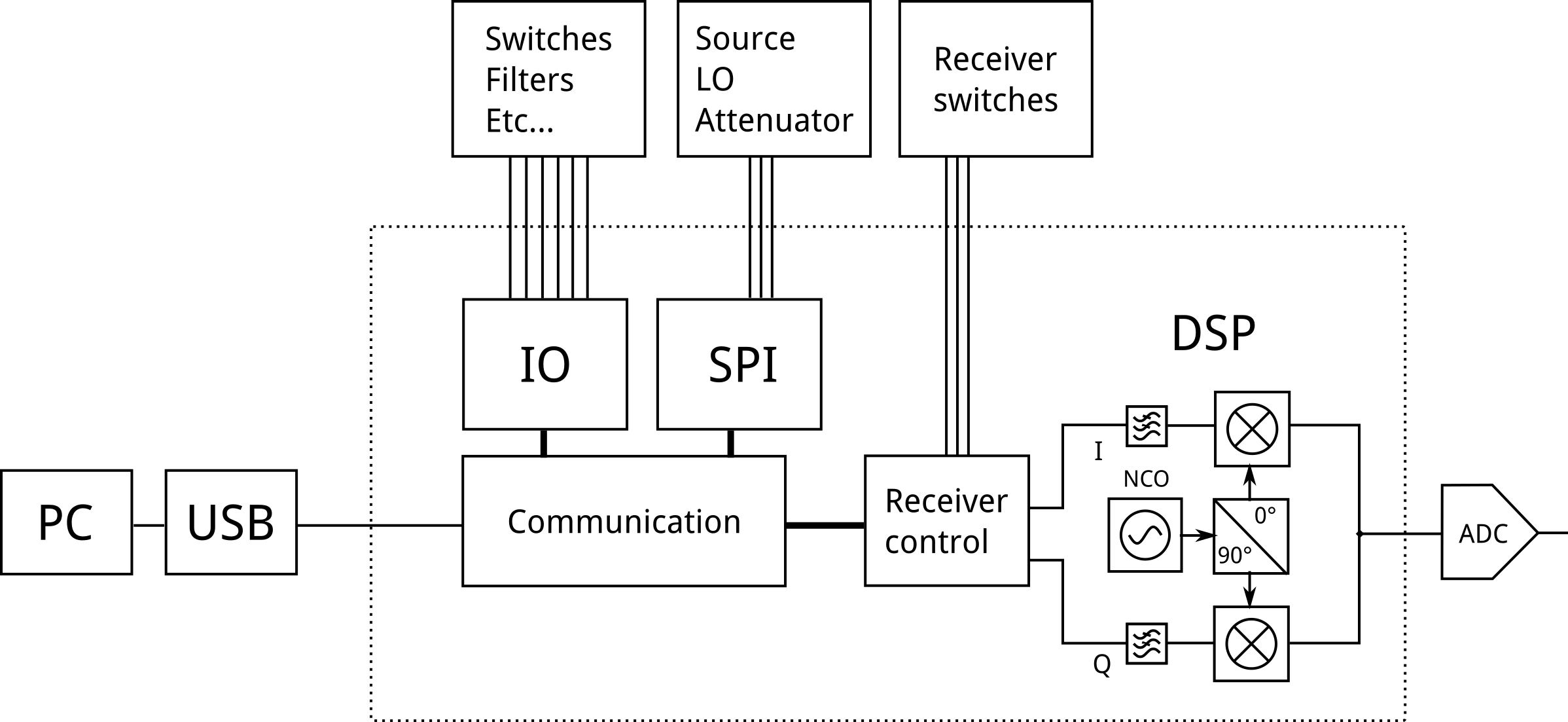

新VNA框图。

上面是新 VNA 设计的框图。它与块非常相似 上面显示的先前版本的图表。端口和接收器交换机是 更改为多个串联的 SP2T 交换机,因为单个交换机无法提供 必要的隔离。在 混频器以降低接收器的噪声系数。

巴伦也添加到混合器之前以提高其性能。混合器是 设计用于与巴伦一起使用,巴伦将单端射频信号转换为 差分,但宽带巴伦太贵了。只有 Minicircuits 销售 足够宽的巴伦。每件售价 8 欧元,最低订购量为 20 件 加上运费。订购巴伦的成本会比其他所有巴伦都高 组件组合在一起,所以我决定将其排除在外并接受性能 第一个版本中的损失。但是,我找到了销售 同样的巴伦,少量多余。巴伦输入回波损耗 调频器的转换增益、噪声系数和线性度得到改善。

尽管框图看起来非常相似,但还有其他大 变化:

-

微控制器被可以做数字信号的FPGA所取代 在板上处理,减少了 PC 所需的计算能力。 板载处理速度要快得多,测量速度应该会提高 因为不再需要将所有ADC样本传输到PC。

-

ADC 以前是集成在微控制器上的 12 位 ADC,是 以 10 MHz 采样。现在,它被采样的14位外部ADC所取代 在 40 MHz 时。这应该会大大增加接收器的动态范围。

-

在以前的版本中,定向耦合器集成在 PCB 上,但 现在它们位于单独的 PCB 上。这允许尝试不同的 耦合器并改进它们,而无需更换整个 VNA。

-

接收器与其他组件屏蔽。为了提高隔离度,请从 从源到接收器,接收器与其他一切严重隔离。射频 信号在PCB的内部层上布线,顶部和底部 接地层以尽可能屏蔽信号。

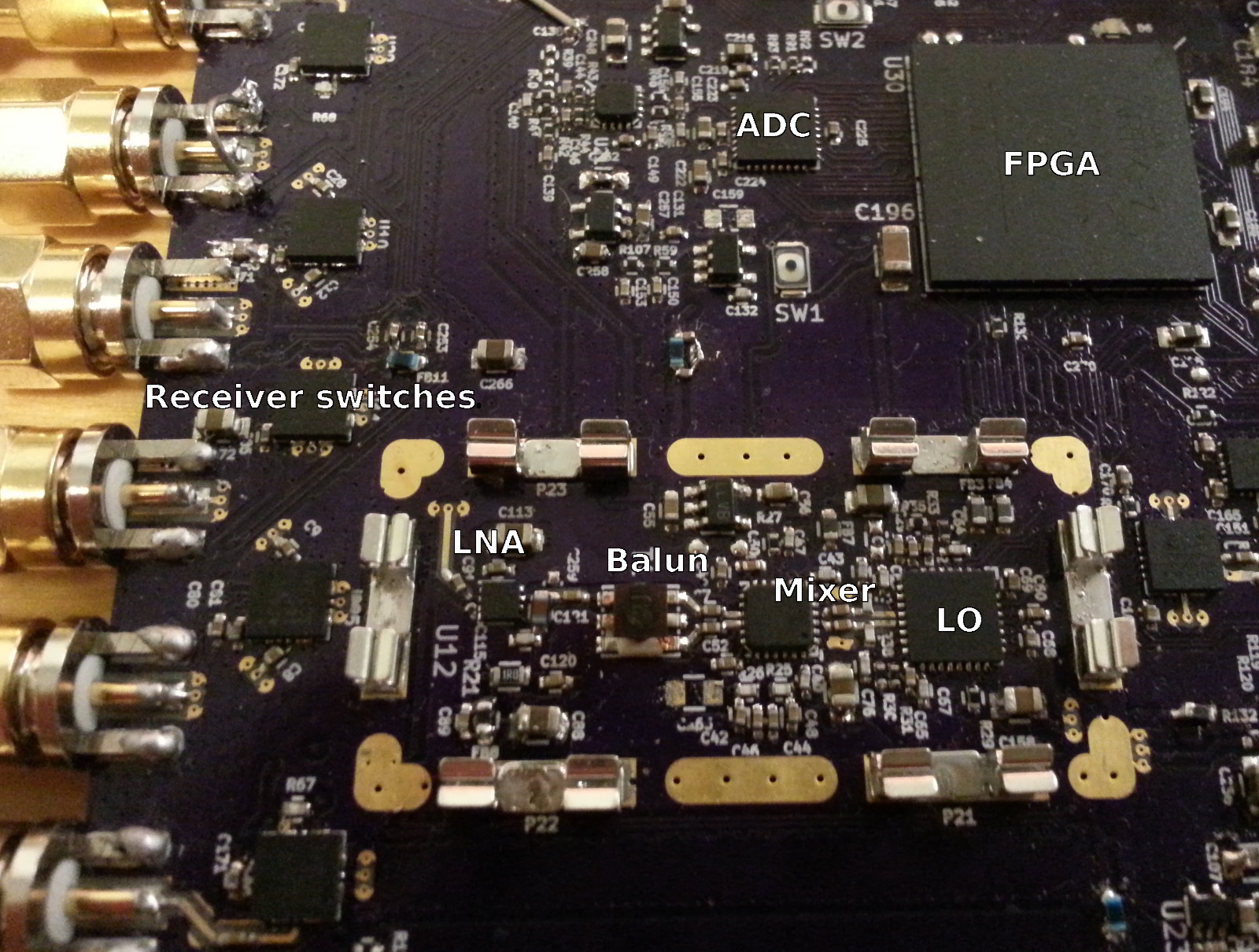

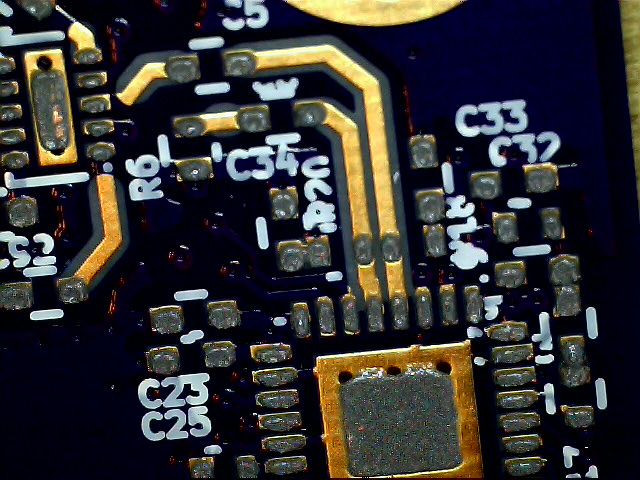

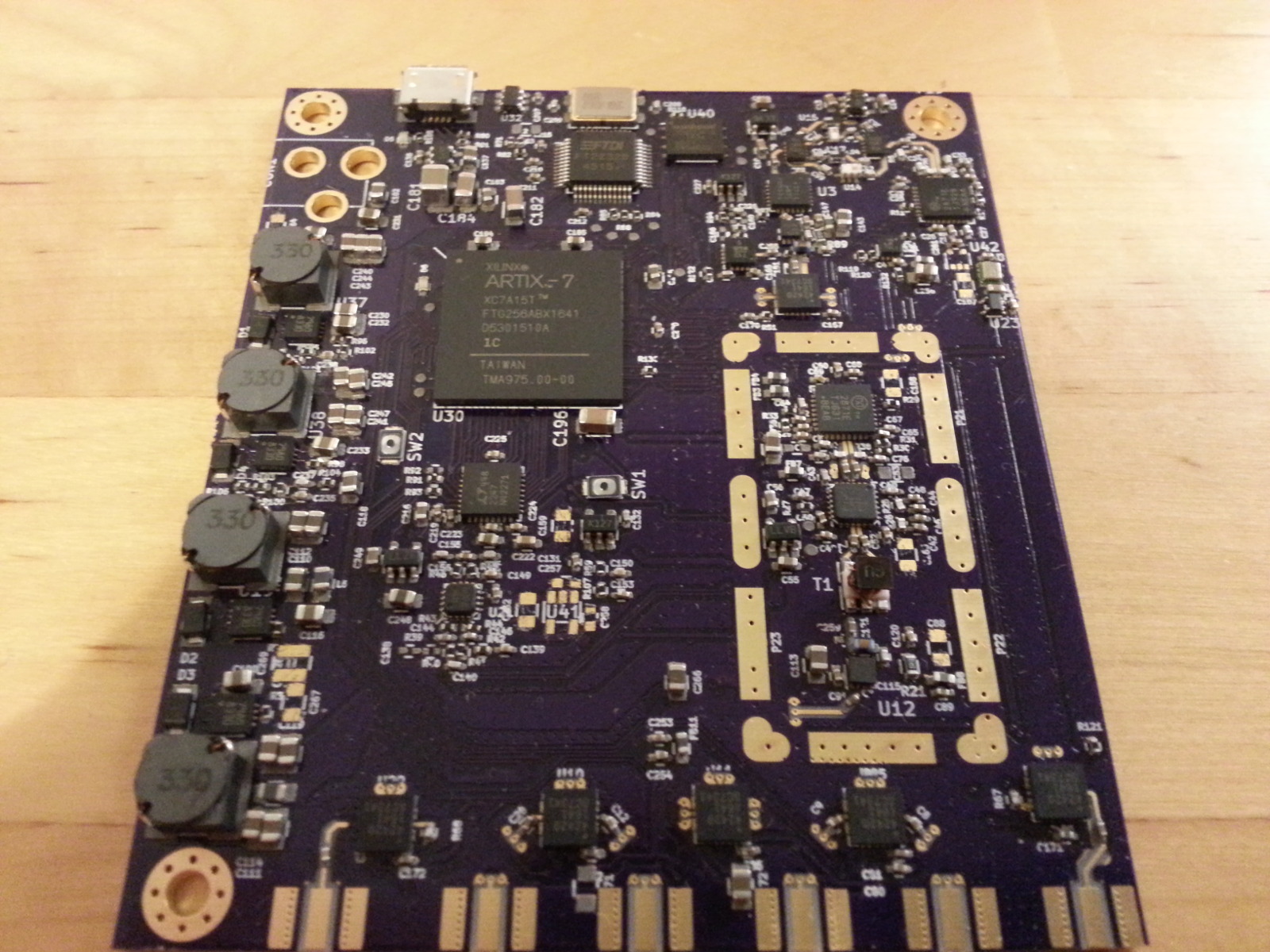

接收器组件已贴标签。

上图是不同组件的成品接收器部分的图片 标记。盾牌需要在棋盘上占用大量空间,但这并不影响 最终PCB尺寸太大,因为SMA连接器和电源限制了 最小电路板尺寸。

设计

图解的

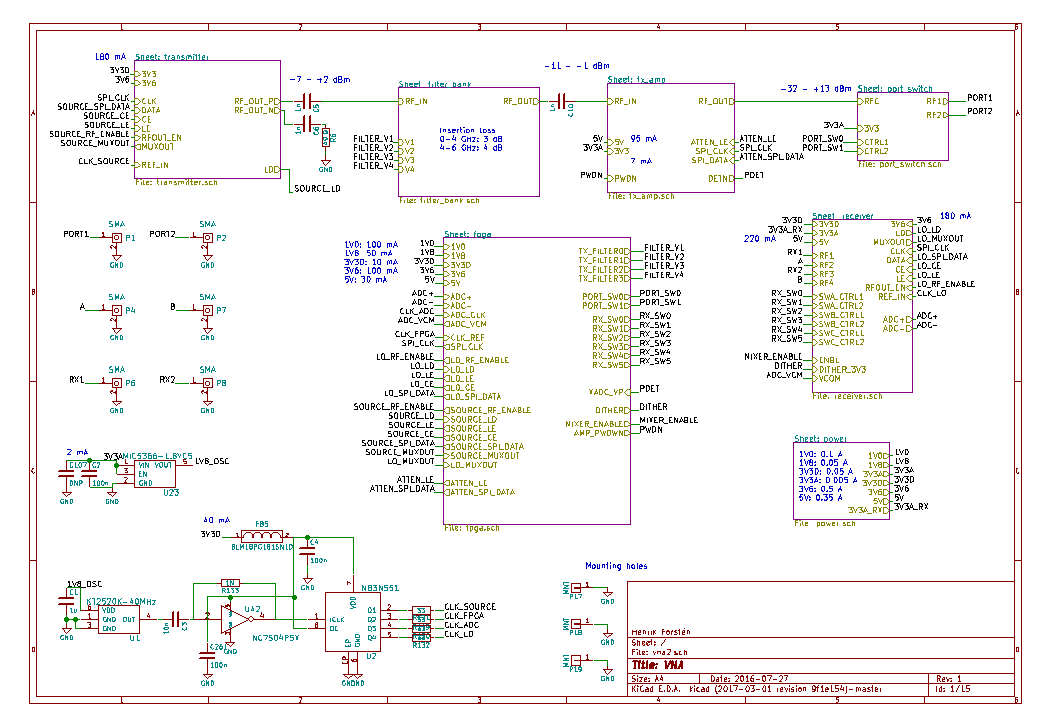

图解的。 点击查看 PDF。

主要是由于添加了 FPGA,原理图中的张数几乎翻了一番从第一个版本的 8 个增加到新版本的 15 个。BOM 有 522 个组件,但它也包括安装孔、射频封装和测试点等这些是 PCB 功能。还有许多空的足迹并不意味着以防万一。为了进行比较,以前的版本有 342 个BOM 中的组件。

FPGA

简化的 FPGA 框图。

大多数高级逻辑,例如计算接收器的 S 参数读数和确定扫描中的频率点,都是在 PC 上完成的。板载 FPGA 负责低级处理,例如切换 IO基于 PC 命令的线路,并从ADC 样本。

数字信号处理的工作方式与第一个版本相同。应接纳样本分为两个分支,它们乘以cos(2πft)和罪(2πft). 数字LO的频率与混频器的输出相同,在本例中为2 MHz。这导致信号被混合下降到直流。取样本的下一个平均值,得到两个数字 I 和 Q.

DSP 的另一种思维方式是乘以 sin 和 cos,然后取平均值等于傅里叶变换的一个频箱:

Xk=1N∑n=0N−1xne−2π我kn/N

这是测量已知信号幅度和相位的最佳方法 受高斯噪声影响的频率。

定向耦合器

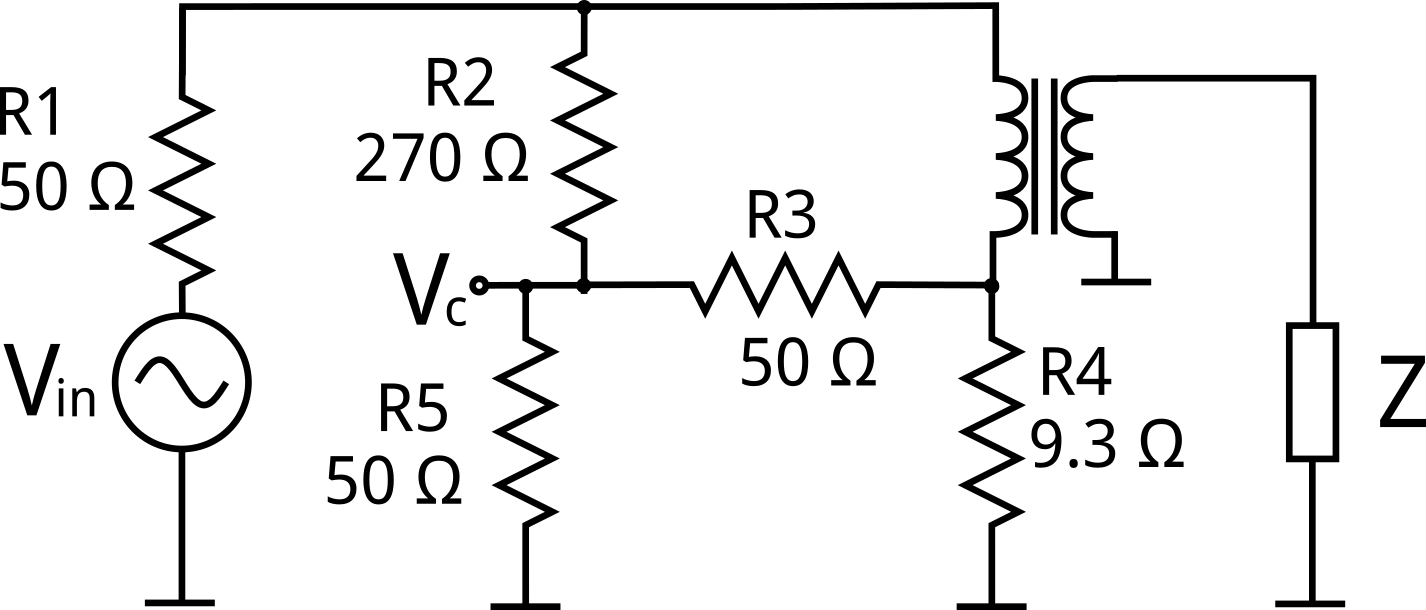

电阻桥耦合器原理图。R1 和 R5 是 源极和负载的端接电阻,并且不在电路板上。Z 是 正在测量的未知阻抗。Vc 电压因 Z 而异。

以前的定向耦合器是带状线耦合线耦合器,具有 PCB内层的两条紧密放置的线。它确实很有效 在大约 2-4 GHz 时,但在较低频率下,线路非常短 与信号和耦合的波长相比非常低。这 导致接收器输入功率在低频下非常低,导致 非常嘈杂的测量。耦合器的 4 GHz 以上方向性不是很 好。理想情况下,测量反射信号的耦合器不会耦合任何 信号从源到测试端口,并且仅耦合信号 从被测设备返回源头。在实践中 定向耦合器具有有限的方向性和一些信号通过 从源到DUT也耦合到接收器。此方向性误差 必须在校准期间进行测量并从测量中删除。 方向性误差的减法并不完美,是首选 如果它足够低,以至于测量值和实际值之间的潜在误差 方向性不会对测量结果造成很大的误差。

对于新的定向耦合器,我决定将架构更改为 电阻桥耦合器,因为它可以在非常宽的范围内提供非常平坦的耦合 带宽从 kHz 频率到超过 10 GHz。顾名思义,它基于 不具有频率依赖性的电阻器,如耦合线和 频率响应仅受寄生效应的限制。商业 VNA 通常 具有电阻桥耦合器以达到传输的 kHz 频率 基于线路的耦合器不实用。

电阻电桥基本上是惠斯通的变体 桥。同轴巴伦是 插入桥以允许连接单端负载。通常情况下 同轴电缆应比信号波长,但要低 巴伦的频率限制可以通过在巴伦周围添加铁氧体磁珠来扩展 同轴电缆。铁氧体磁珠在低电平时衰减共模信号 频率,并允许使用短路较多的同轴电缆。

与普通惠斯通相比,电阻值也略有修改 桥式电路,使直通损耗更低,耦合损耗更高。请参阅本文 概述此耦合器架构的工作原理。

我的耦合器的设计基于这篇 IEEE 论文。

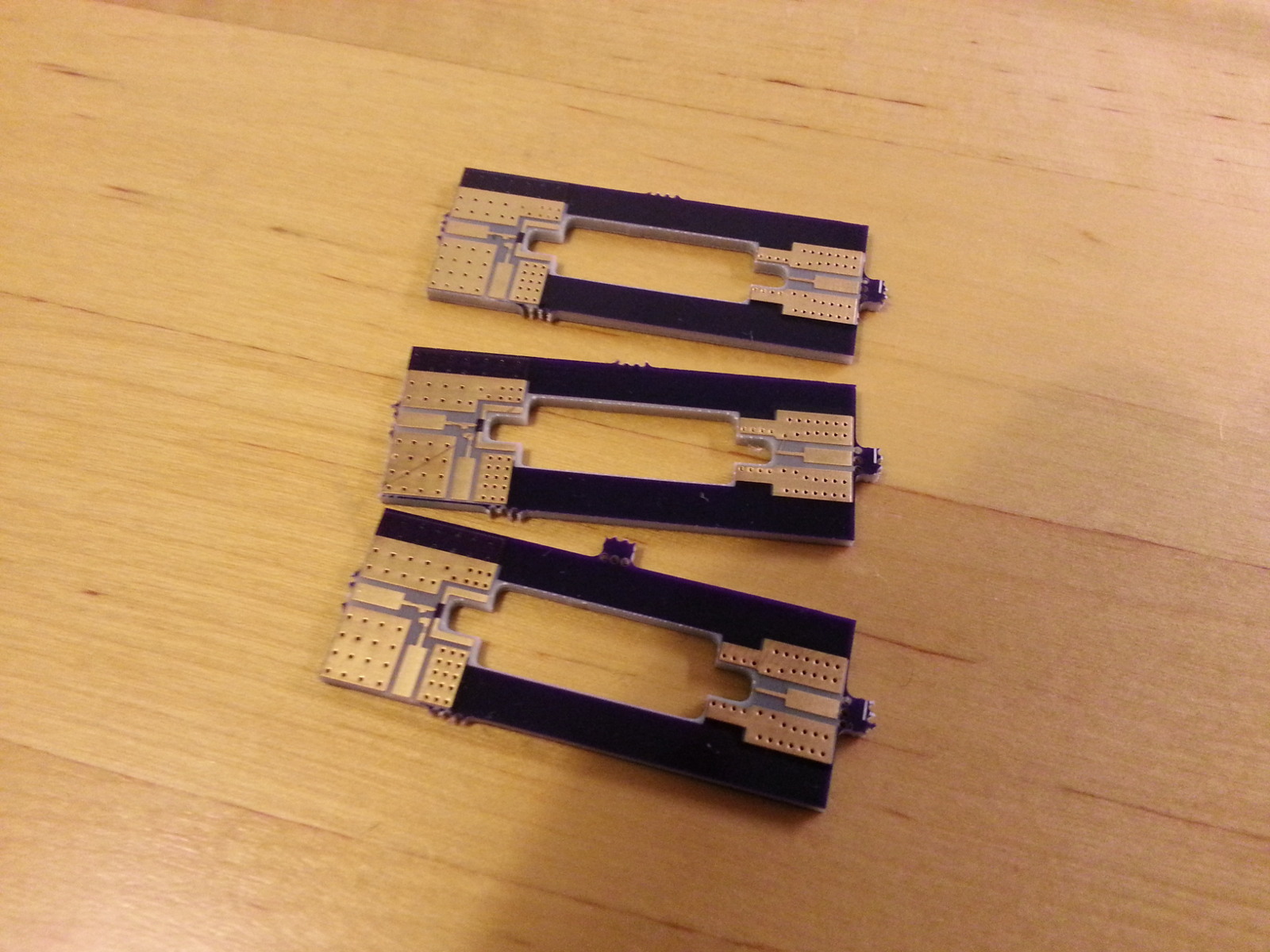

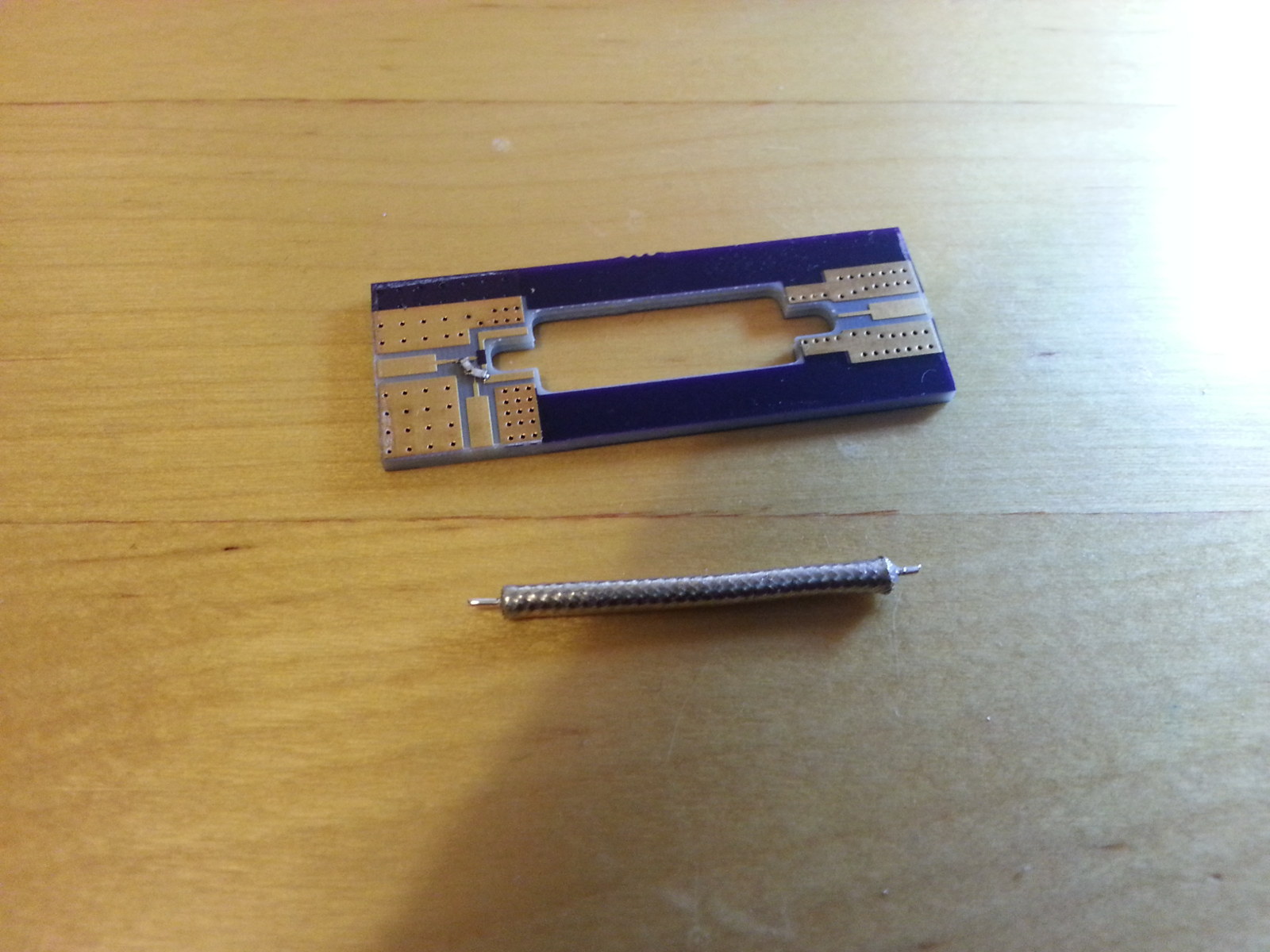

定向耦合器 PCB。

用于巴伦的短同轴电缆。

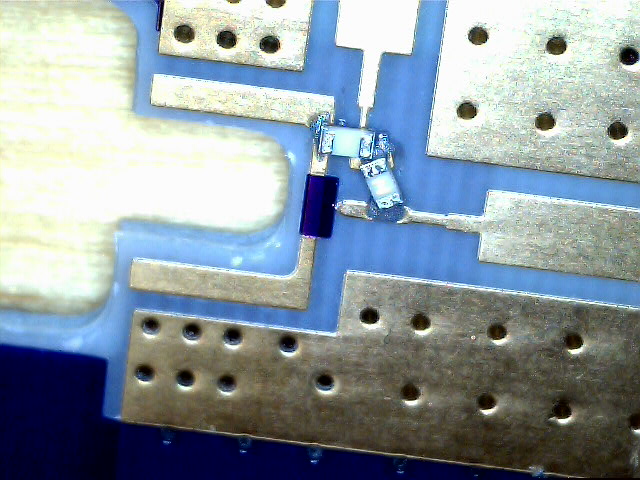

SMD 电阻器倒置焊接到 最大限度地减少寄生。

至少理论上,SMD电阻器倒置焊接应该有一点点 寄生电感低于以正确方式焊接时的寄生电感。电阻 元件位于电阻器的顶部,通过将其倒置安装,它是 靠近 PCB 接地层,降低其电感。

两个成品耦合器,周围有铁氧体磁珠 同轴电缆。

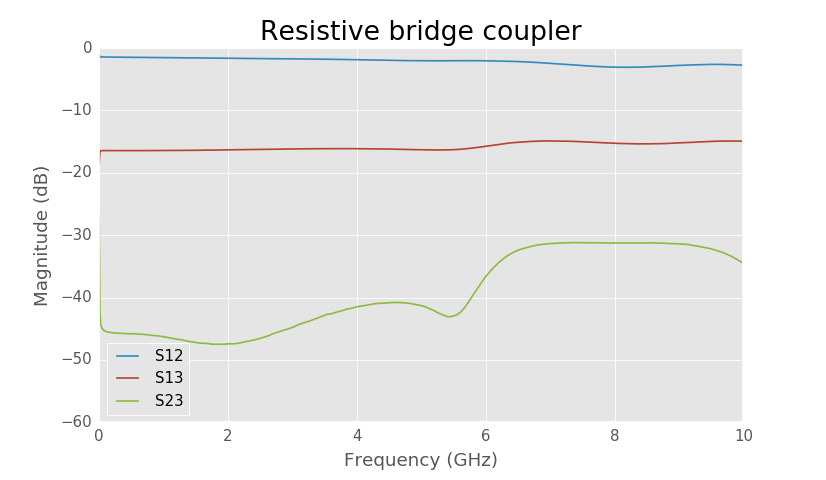

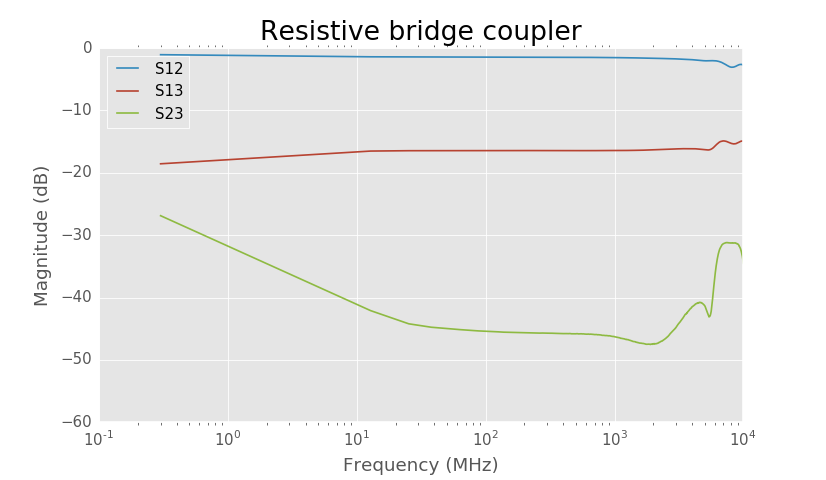

耦合器的测量 S 参数。

耦合器的测量 S 参数。

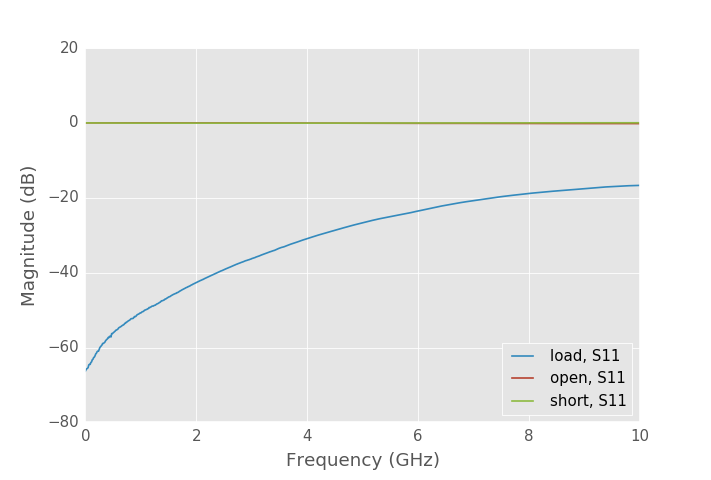

在上图中,使用高达 10 GHz 的商用 VNA 测量的 S 参数。 耦合器被测量为两个端口,第三个端口以高电平端接 VNA 校准套件的质量端接。

S12走线为直通路径,S13为耦合路径,S23为隔离路径 方向。指向性为 S13 - S23,在高达 5.5 GHz 时优于 25 dB 之后大约 15 分贝。匹配在低频下非常好,但开始 随着频率的增加而恶化。通过损耗约为 1.5 dB。

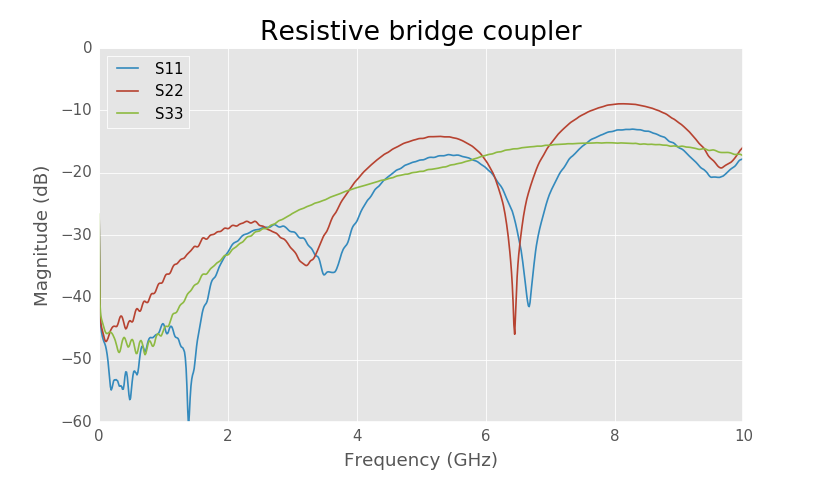

耦合器的测量 S 参数。对数的 规模。

当 X 轴更改为 对数的。同轴巴伦上的铁氧体扩展了低频范围,并且 耦合器在 300 kHz 时仍具有约 5 dB 的指向性。

总的来说,我对耦合器的性能非常满意。匹配 联轴器的方向性和平坦度都比联轴器好得多 以前版本的 VNA 上的线路耦合器。使用这些耦合器应该 导致更准确的测量。

软焊

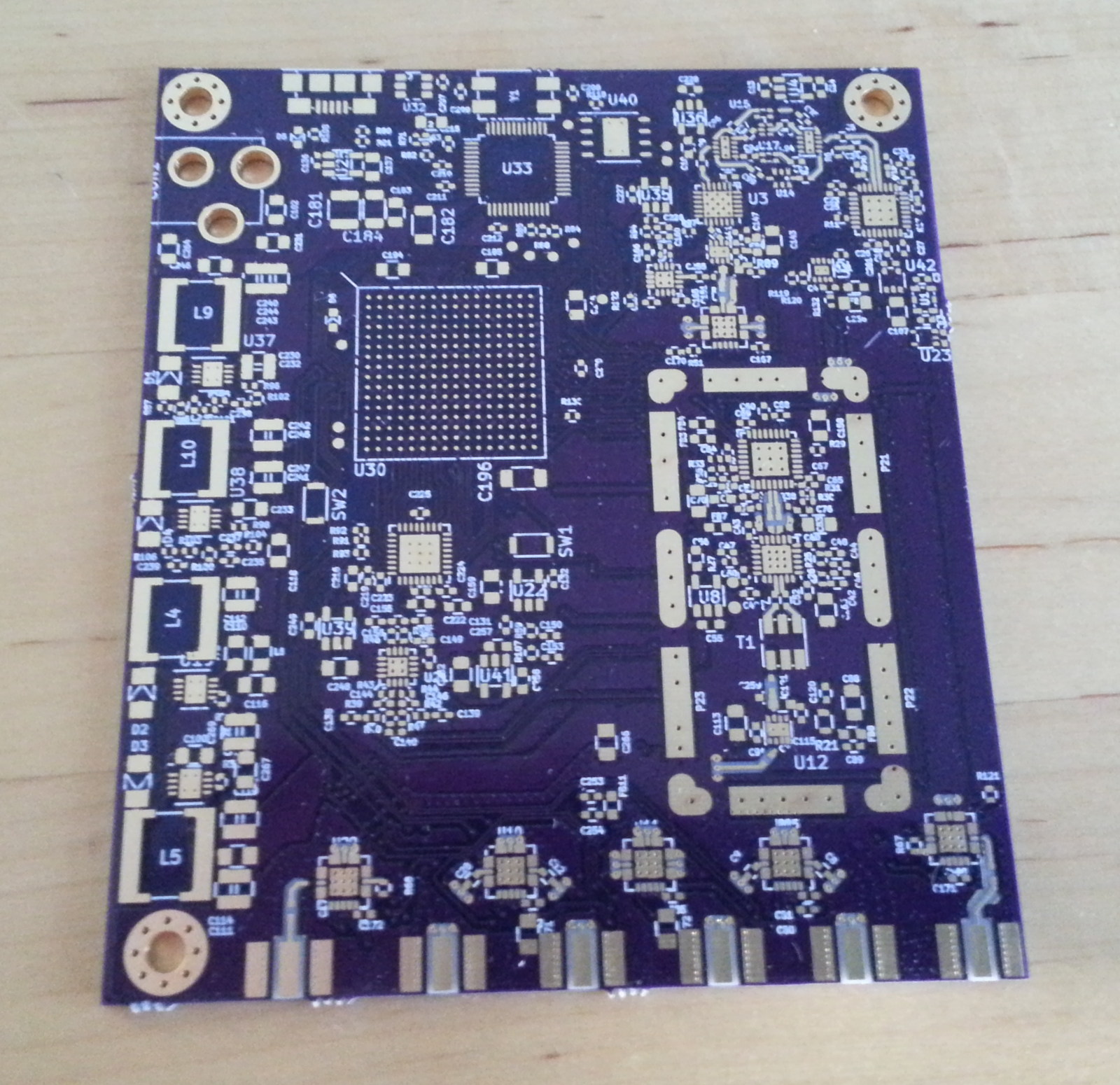

裸露的PCB。

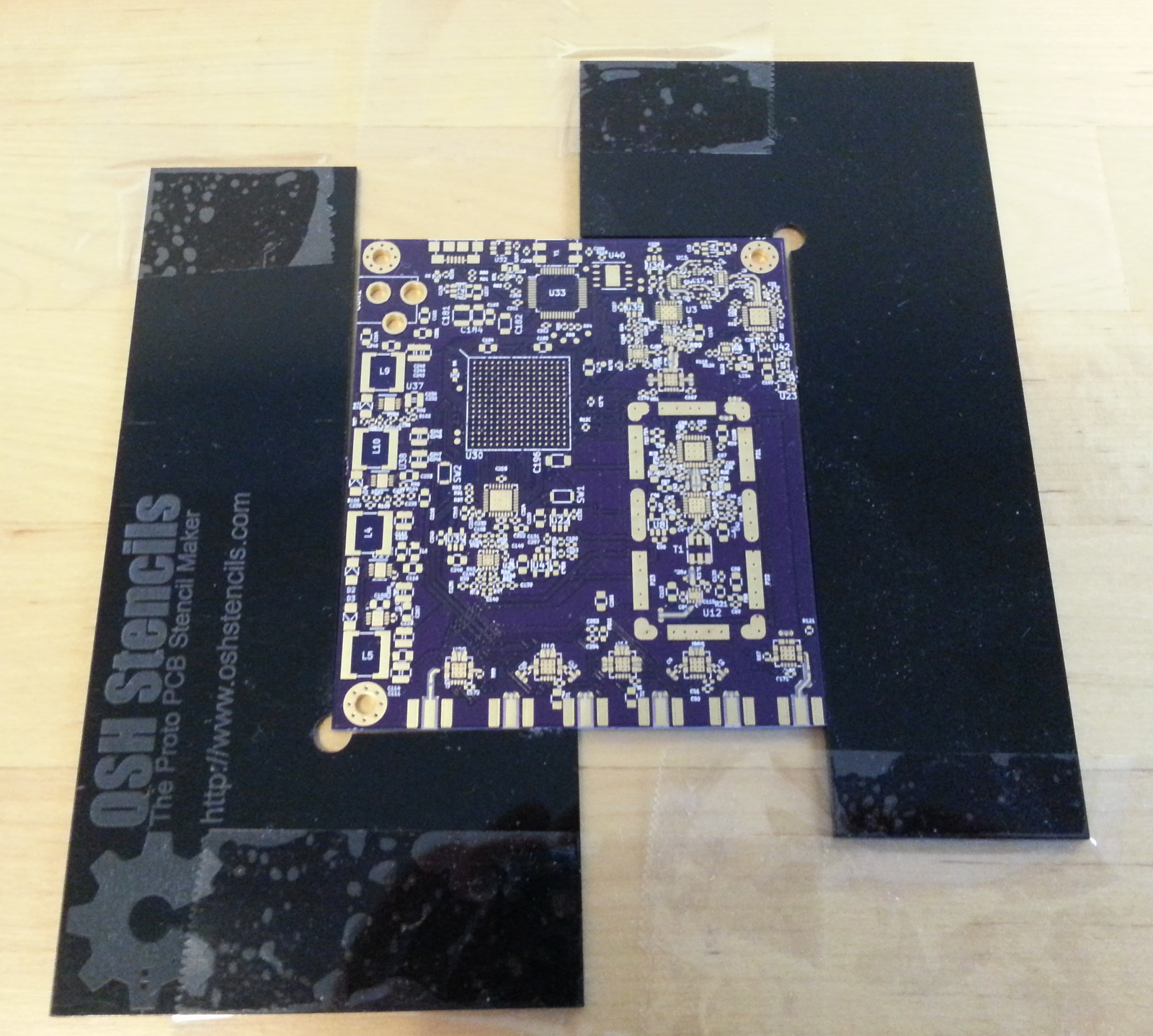

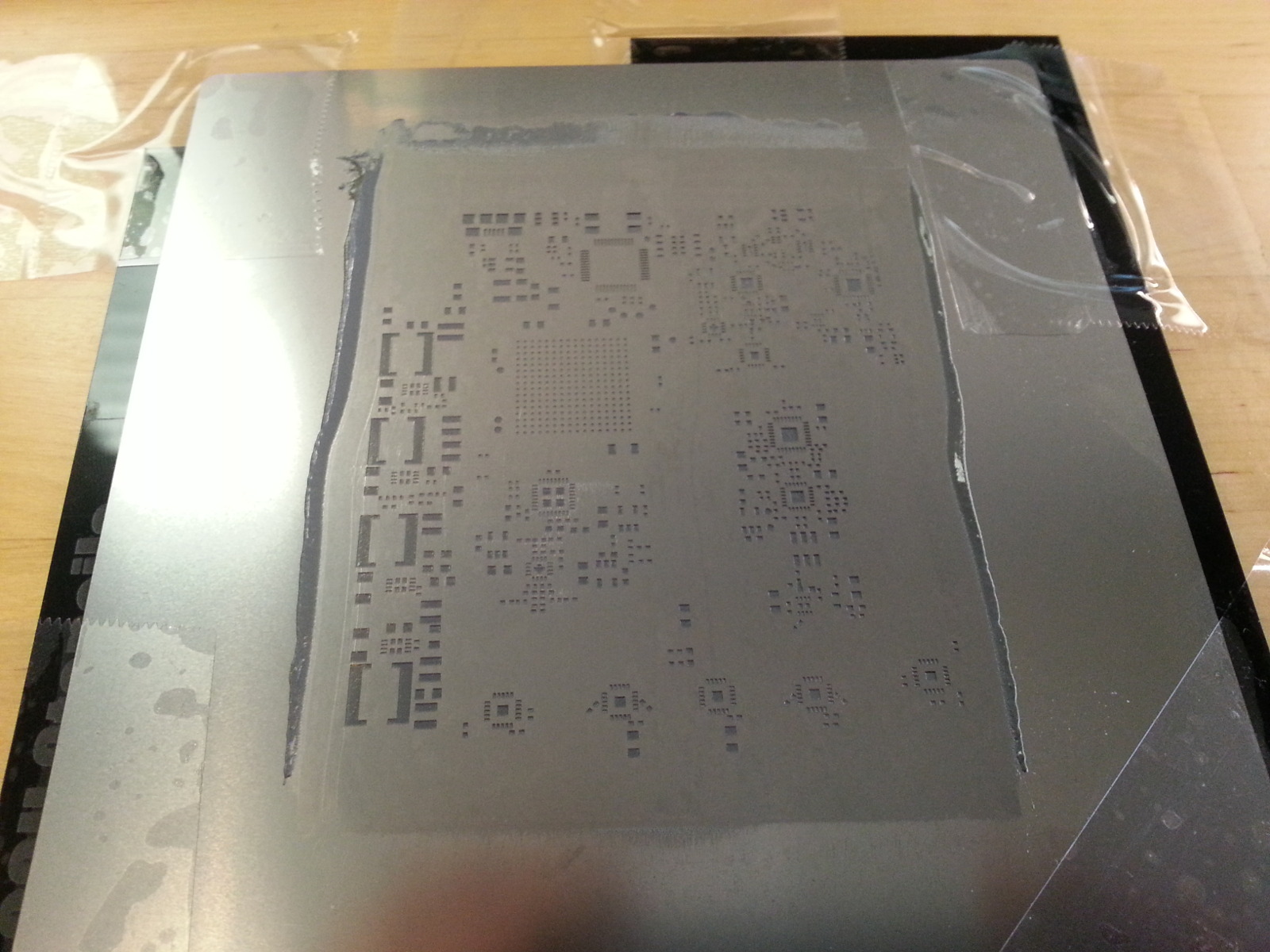

PCB 固定用于焊膏模板。

与第一个版本一样,PCB 来自 OSH Park。职业安全与健康公园 提供 4 层 FR408 基板 PCB,损耗更低,控制更好 高频时的介电常数。它似乎是目前唯一便宜的 非 FR4 过程,如果您阅读了我的其他帖子,我已经使用了很多。

之前我先做了PCB的背面,但我发现它 使得在正面涂抹锡膏的难度更大,因为电路板 不会直接坐在桌子上。这次我决定用 首先是困难的组件,然后手工完成背面。拥有公寓 没有组件的背面有助于固定 PCB 和模板 结果比上次好。不锈钢模板也应该有帮助 使用锡膏应用,应该会产生更清晰的边缘 沉积物比我以前使用过的聚酰亚胺模板。模板来自职业安全与健康 模板。

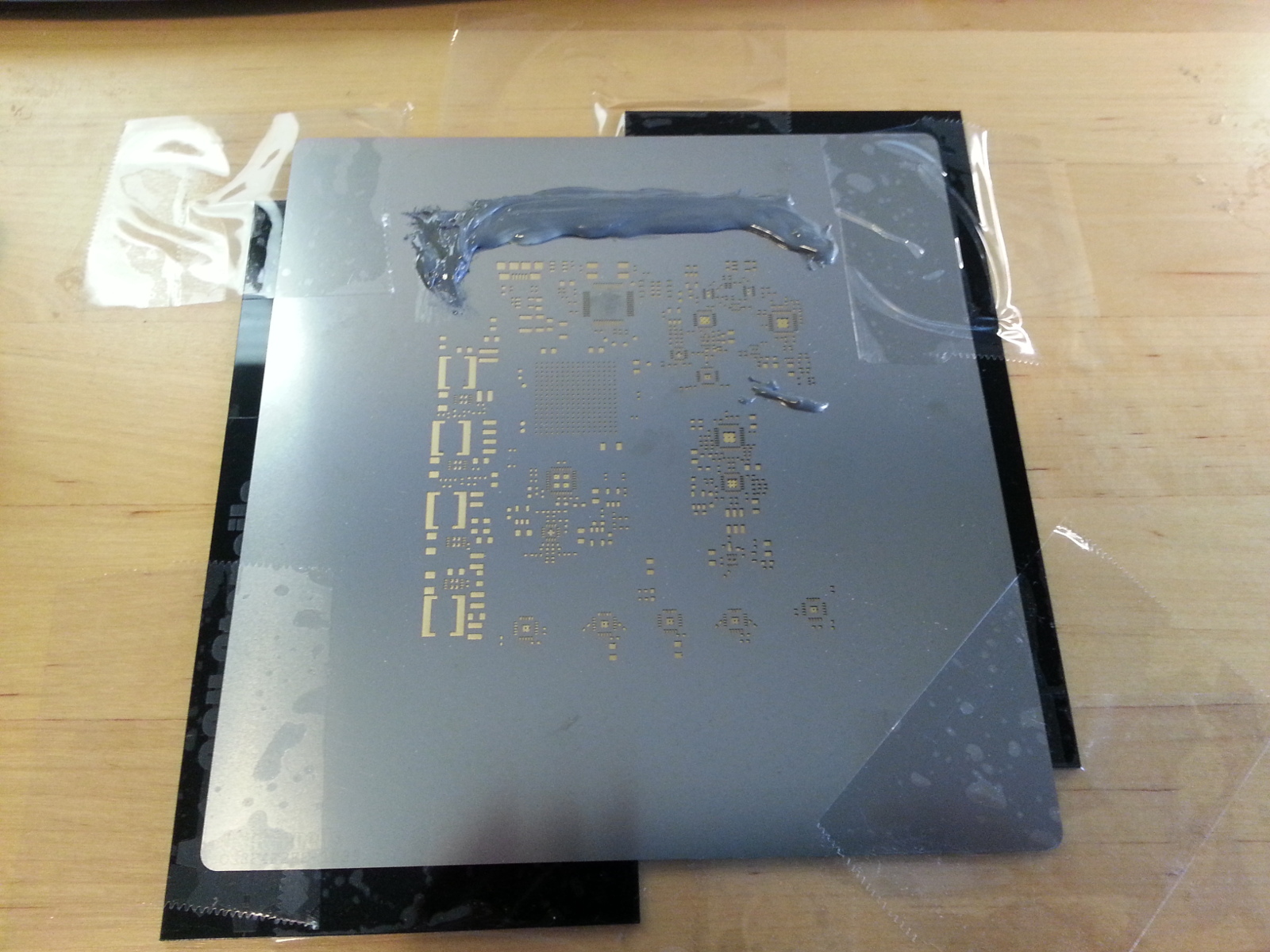

模板上的焊膏。

涂抹糊状物后。

BGA 封装上的焊膏。

射频源元件上的焊膏。

锡膏模板非常成功。糊状沉积物的边缘是 定义非常明确。

BGA放置在锡膏上。球距为 1 毫米,即使用手也很容易定位。

Xilinx FPGA 采用 256 球封装,球间距为 1 mm。这是非常 BGA 封装的大间距,使在家焊接变得非常容易。有 即使在低成本 PCB 上,也有舒适的空间来路由所有信号 喜欢这个。

放置在糊状物上的组件。

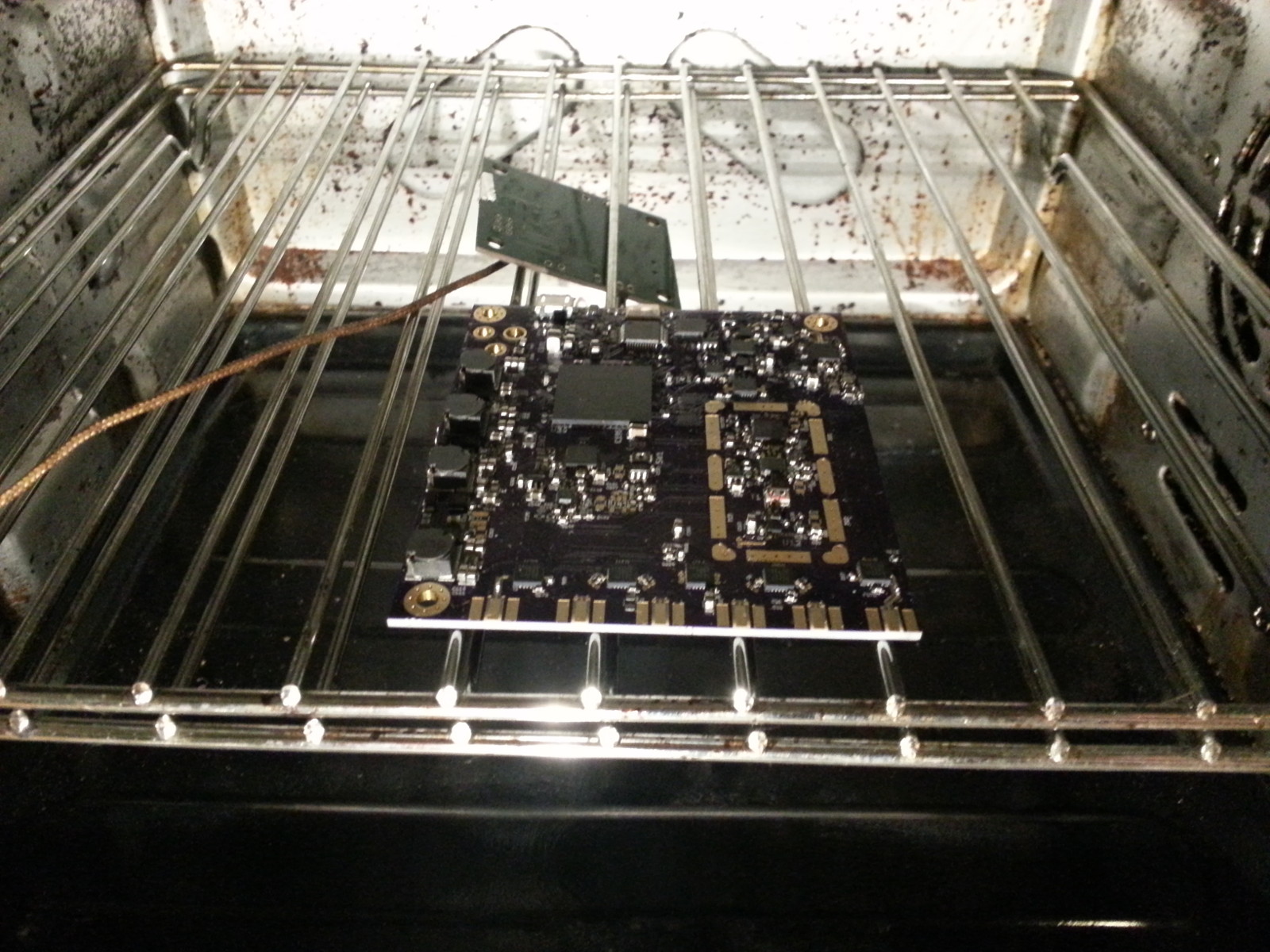

回流炉中的PCB。

我用的是同样的旧烤面包机 回流焊烘箱 我已经制作了所有其他项目。背面的绿色 PCB 可容纳 温度传感器。

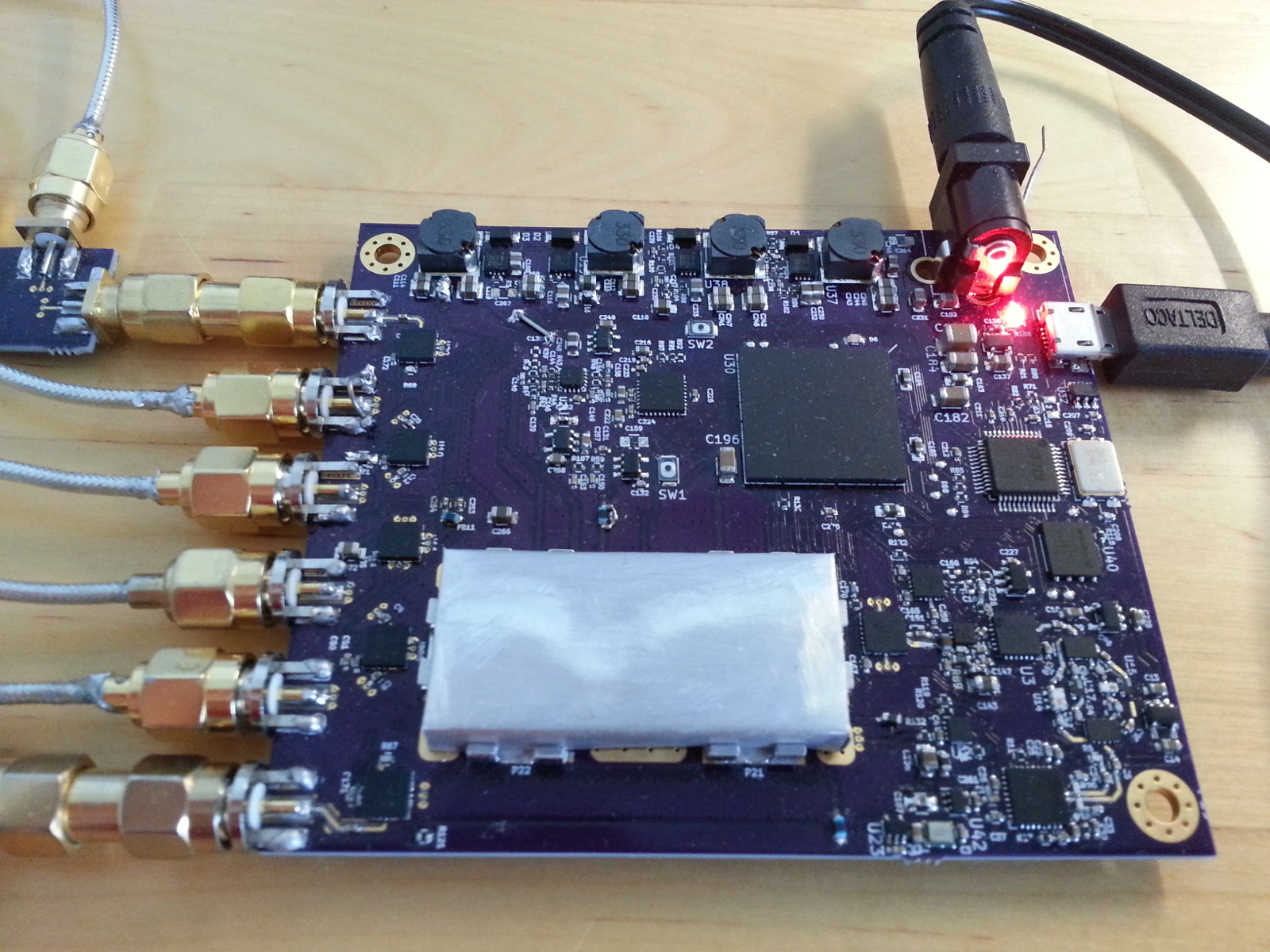

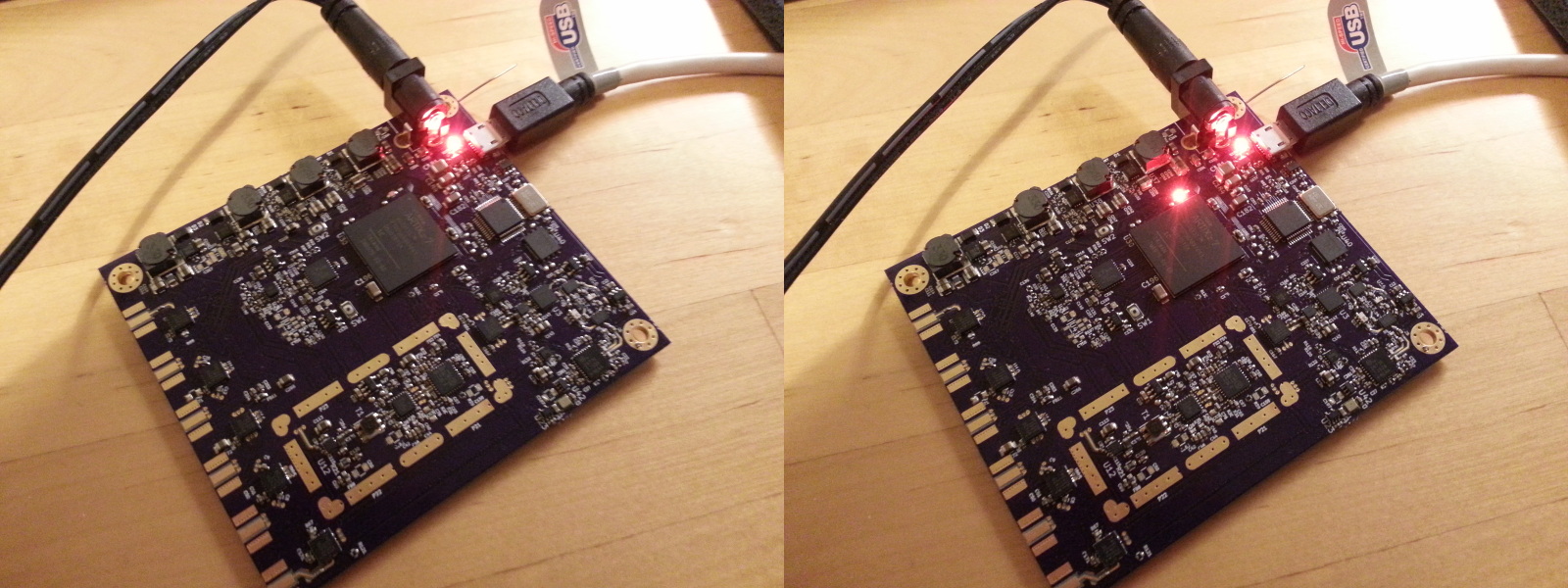

世界您好!

我为 FPGA 制作了一个快速位文件,只需闪烁 LED 即可一切正常 第一次。

测量

接收器

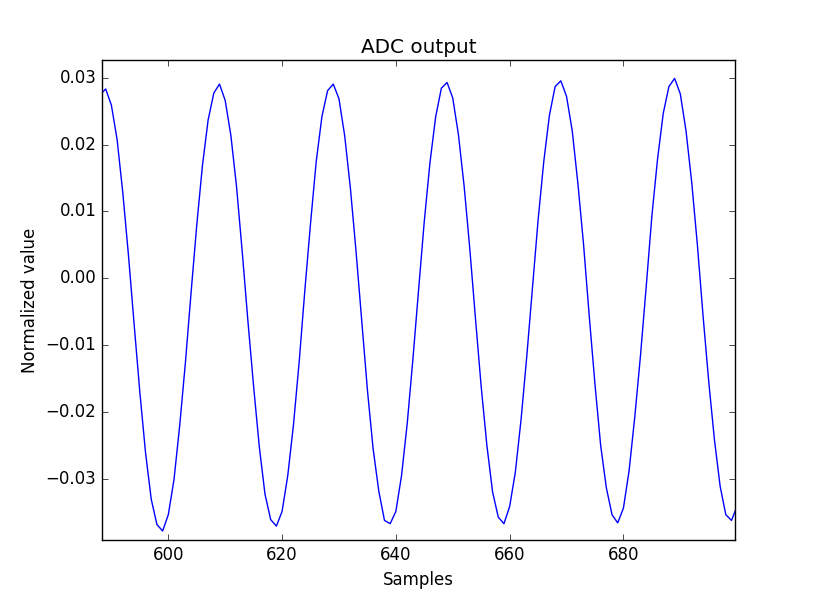

ADC输出波形。

外部 14 位 ADC 对接收器动态范围有很大影响 与之前集成在微控制器中的 12 位 ADC 相比。搅拌机 输出频率是可编程的,在上图中设置为2 MHz。确切 频率并不重要,但设置频率有一些限制。 在低频下,有抖动信号和更多的噪声,在高频时 IF放大器和ADC的频率线性度不太好。在某个时候, 抗混叠滤波器也将开始衰减信号。2 MHz 是好的 妥协。

ADC的采样频率为40 MHz。理论上,它可能会低得多 没有混叠和高采样率的 ADC 成本更高,所以为什么不使用 例如 10 MHz ADC?原因有三:

-

为了简化时钟分配,FPGA、PLL 和 ADC 使用相同的时钟 信号。40 MHz 对所有这些来说都是一个不错的价值。如果时钟不同 使用频率时,需要添加时钟分频器或 PLL。 FPGA 可以使用单独的时钟,但 PLL 参考时钟和 ADC 采样时钟 需要同步。

-

高采样速度允许使用更简单的抗锯齿滤波器。

-

采样速度可以用准确性来换取。当两个连续的ADC采样 平均动态范围增加 3 dB。采样速度翻两番 平均采集四个样本可使动态范围增加 6 dB,从而 等于样本深度增加一位。动态范围为 40 MHz 14 位 ADC 相当于 10 MHz 15 位 ADC 或 2.5 MHz 16 位 ADC。

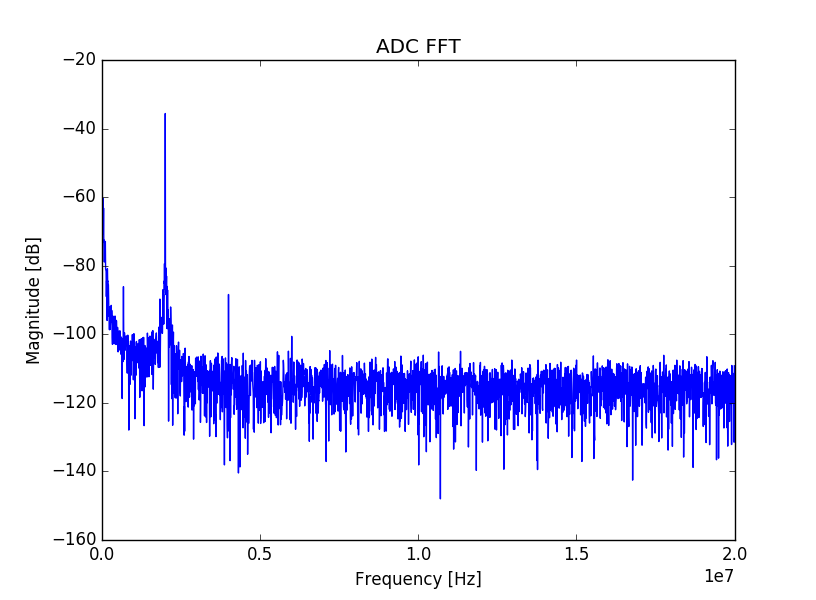

5000个ADC样本的FFT。Y轴为dB满量程。最大非削波输入正弦波为 0 dB。

上面是 5000 个 ADC 样本的 FFT,这是我可以存储在 FPGA 并传输到 PC 上。USB 速度不够快,无法 连续流式传输ADC样本。本底噪声约为 -105 dBF。5000 个样品 对应于 8 kHz 宽的 FFT bin 和 125 μs 的采样时间。每加倍 采样时间使动态范围增加了 3 dB。采样时间为 10 毫秒 (100 Hz IF 带宽)动态范围为 125 dB 和 0.1 s(10 Hz IF 带宽) 提供 135 dB 的动态范围。

相比之下,以前版本的采样动态范围为 90 dB 时间为 400us。由于需要将所有样本传输到 PC,因此此设置为 新版本的采样时间大约是 5 毫秒。由于更好的ADC, 接收机LNA和板载处理动态范围至少增加了30 dB 表示相同的测量速度。

一个端口 S 参数

进行准确的单端口 S 参数测量比双端口容易得多 测量。误差模型要简单得多,隔离度也没有那么大 一个问题。一个端口测量可以用三个参数进行完全校正 错误网络,而两个端口错误网络至少有九个参数。

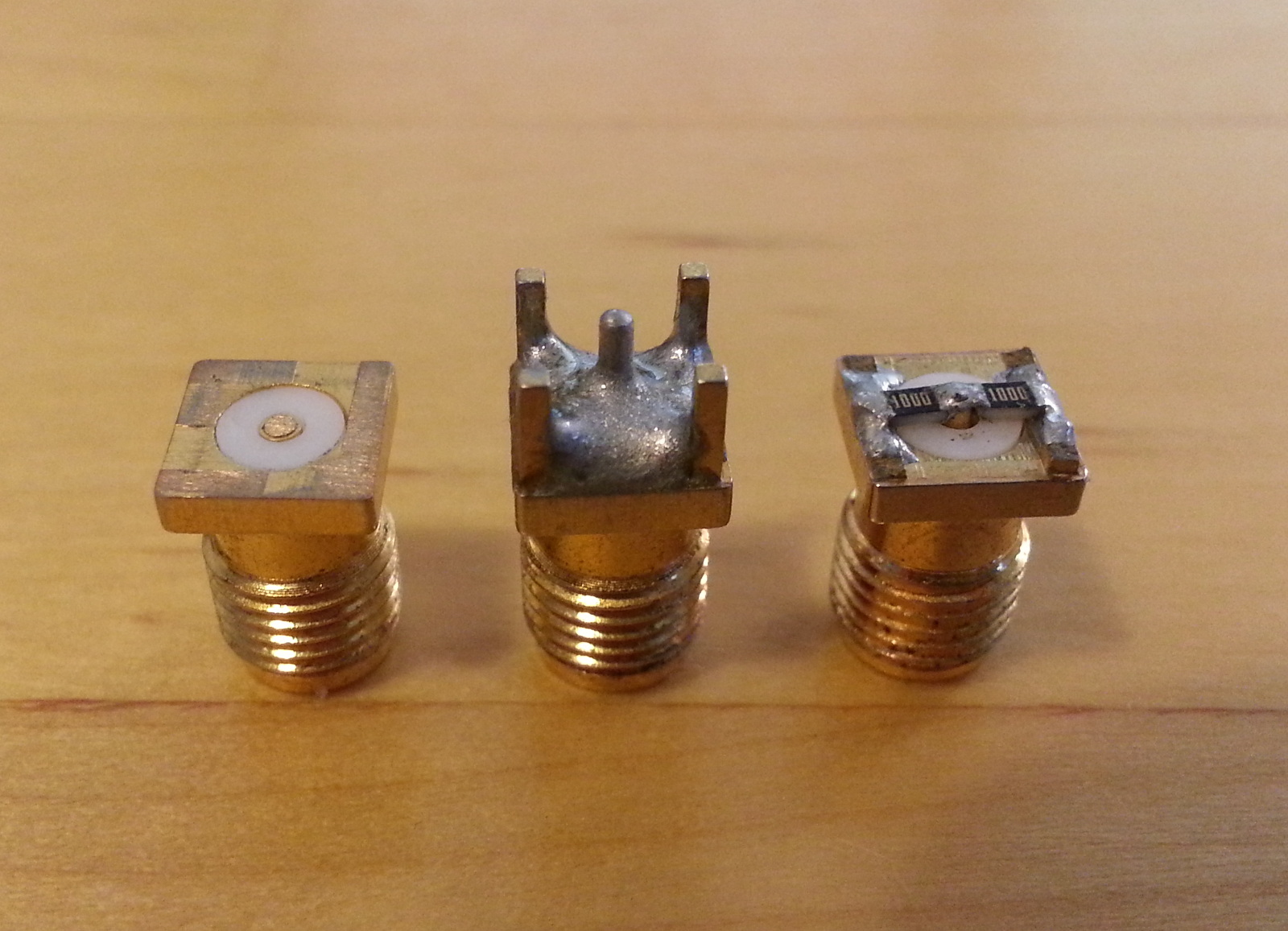

自制 SMA 校准套件。开放、短和 负荷。

测量校准套件 S 参数。

以前我没有关于 校准套件,并且不得不做出降低准确性 测量的 S 参数。

我用商用 VNA 测量了校准套件的 S 参数 使用非常准确且昂贵的校准套件进行校准。这基本上是 将昂贵套件的校准转移到我自制的套件中,并允许我 使用自制套件进行合理准确的测量。

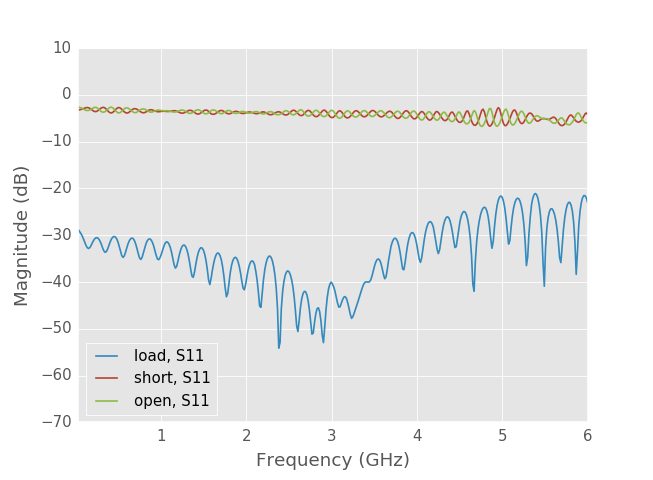

校准的未校准 S 参数 标准。

以上是校准标准的原始未校准测量值 用我的 VNA 测量。由于负载有限,负载被测量为 -30 dB 耦合器的方向性。纹波是由源的变化引起的 匹配。开路和短路不以 0 dB 为中心,因为 耦合。所有这些误差都可以从测量结果和 纠正。

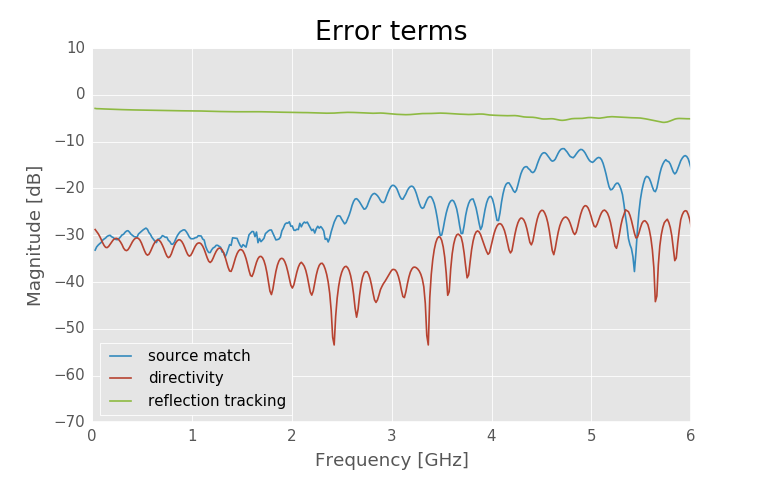

解决了错误术语。

与之前的相同测量相比 版本错误术语现在是 显然要小得多。新型耦合器具有更好的方向性和匹配的减少 开放和短测量中的纹波,并改善了 负载测量。

贴片天线

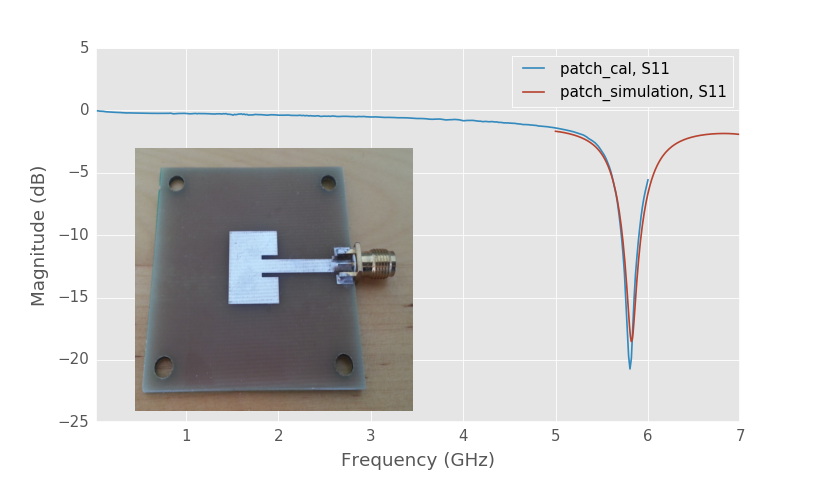

贴片天线的图片和模拟的测量的 S11 迹线。

上面是一个设计用于在 5.8 GHz 下工作的简单贴片天线。"patch_cal"迹线是测量的 S11,"patch_simulation"是来自 EM 模拟器的 S11。测量的 S11 与模拟的非常吻合,迹线非常干净。

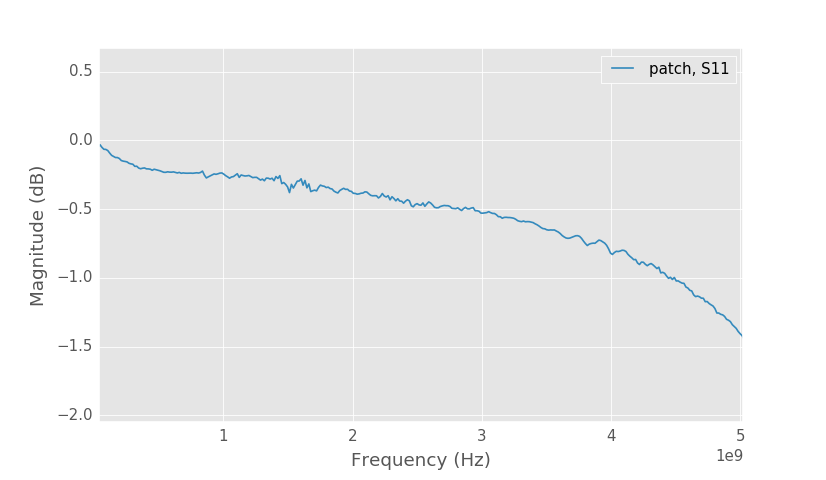

放大贴片天线 S11 跟踪。

贴片天线S11测量中的迹线噪声约为0.1 dB,即 可能是由于源到接收器的泄漏变化造成的。 低于 700 MHz 的性能要好得多,因为低频下的隔离度要高得多 频率。

喇叭天线

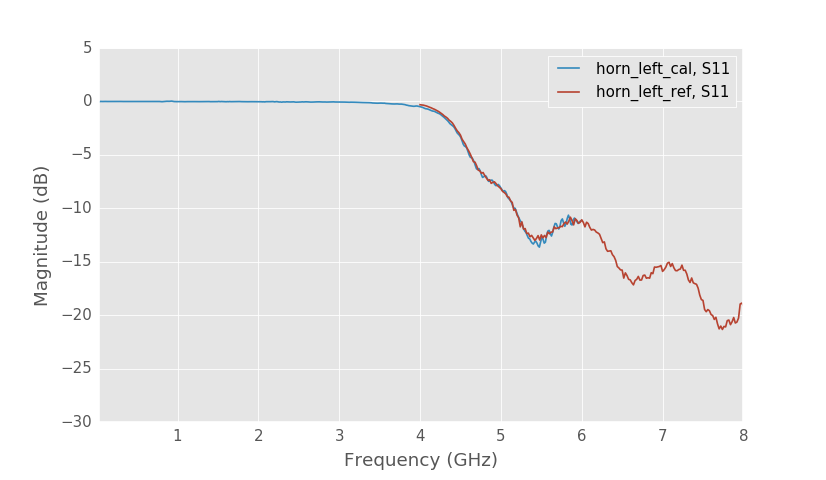

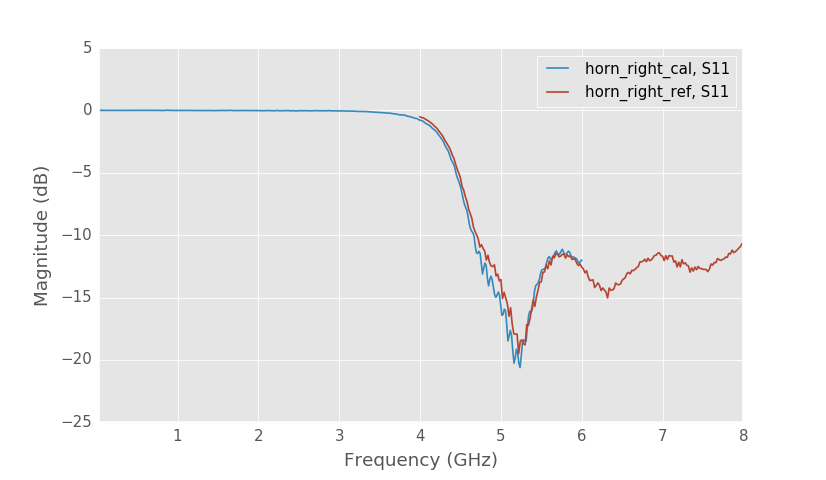

6 GHz 雷达喇叭天线与商用天线的比较 VNA 测量。

以上是我自制喇叭的 S11 测量值("horn_left_cal"痕迹)天线与 使用商业 VNA("horn_left_ref"迹线)进行的测量。与上次测量相比 版本跟踪现在更接近了。最 的改进来自测量校准套件。

其他喇叭天线。

另一个喇叭天线也非常一致。

两个端口 S 参数

端口 1 上的电阻桥耦合器(向下)。带状线 端口 2 上的耦合线路耦合器(向上)。

我没有足够的两个端口的新电阻桥耦合器。所以对于 两个端口测量我不得不从之前的耦合线耦合器 版本。它降低了准确性,但至少它允许我 进行测量。

以前的版本在通道之间有如此高的泄漏,我不得不使用 特殊的 16 项校准,还可以校准所有可能的泄漏 路径。这个版本具有更好的隔离性,我可以使用普通的 SOLT 使用隔离校准进行校准(两个端口都终止)。

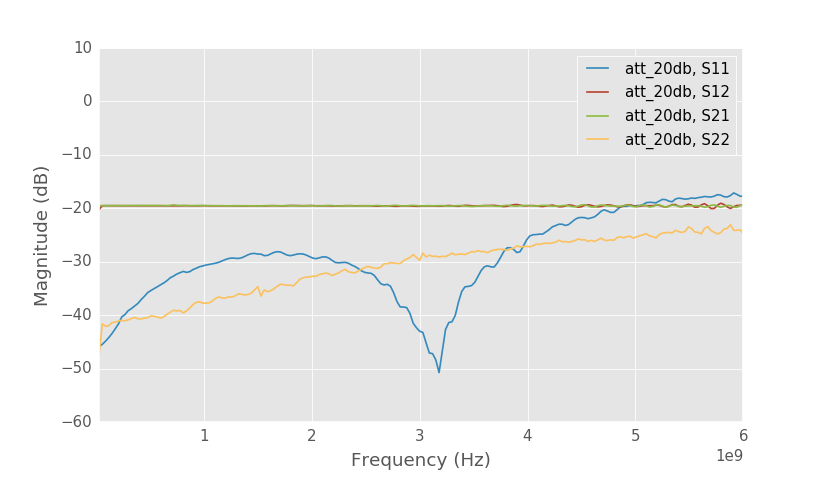

20 dB衰减器S参数。

以上是测量的 20 dB 衰减器的 S 参数。我测量了同样的 衰减器也与旧 VNA 一起使用,并使用相同的 12 项校准质量 非常糟糕。16 学期 校准包括我设法测量的额外泄漏路径 它。有明显的区别 新旧版本之间的S11和S22精度。Ripple 中的 痕迹是非物理的,它们应该是平滑的。

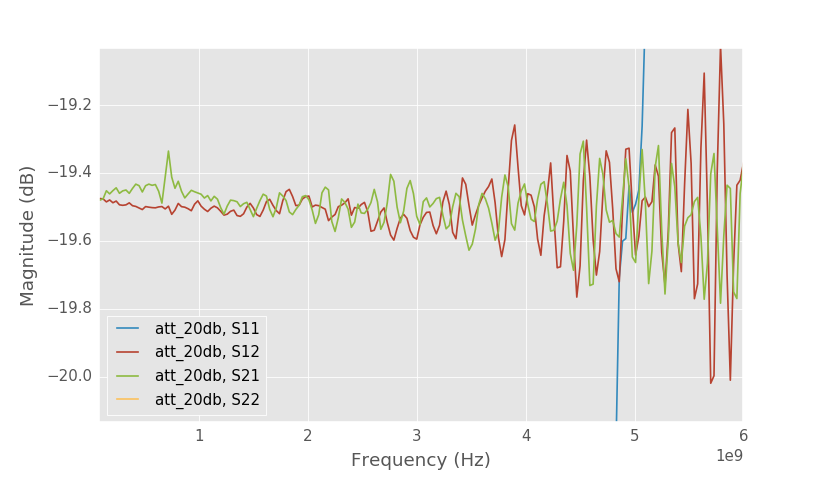

20 dB衰减器S参数。S21、S12 细节。

上面是缩放到 S12 和 S21 迹线的相同测量值。脉动 由于高电平时泄漏较大,频率随频率增加而增加 频率。在低频下,S21 和 S21 之间也存在一些差异 S12 走线是由于不同端口上的不同耦合器造成的。端口 1 具有新的 电阻桥耦合器,而端口 2 具有耦合线路耦合器,具有非常 低频耦合低,降低测量精度。

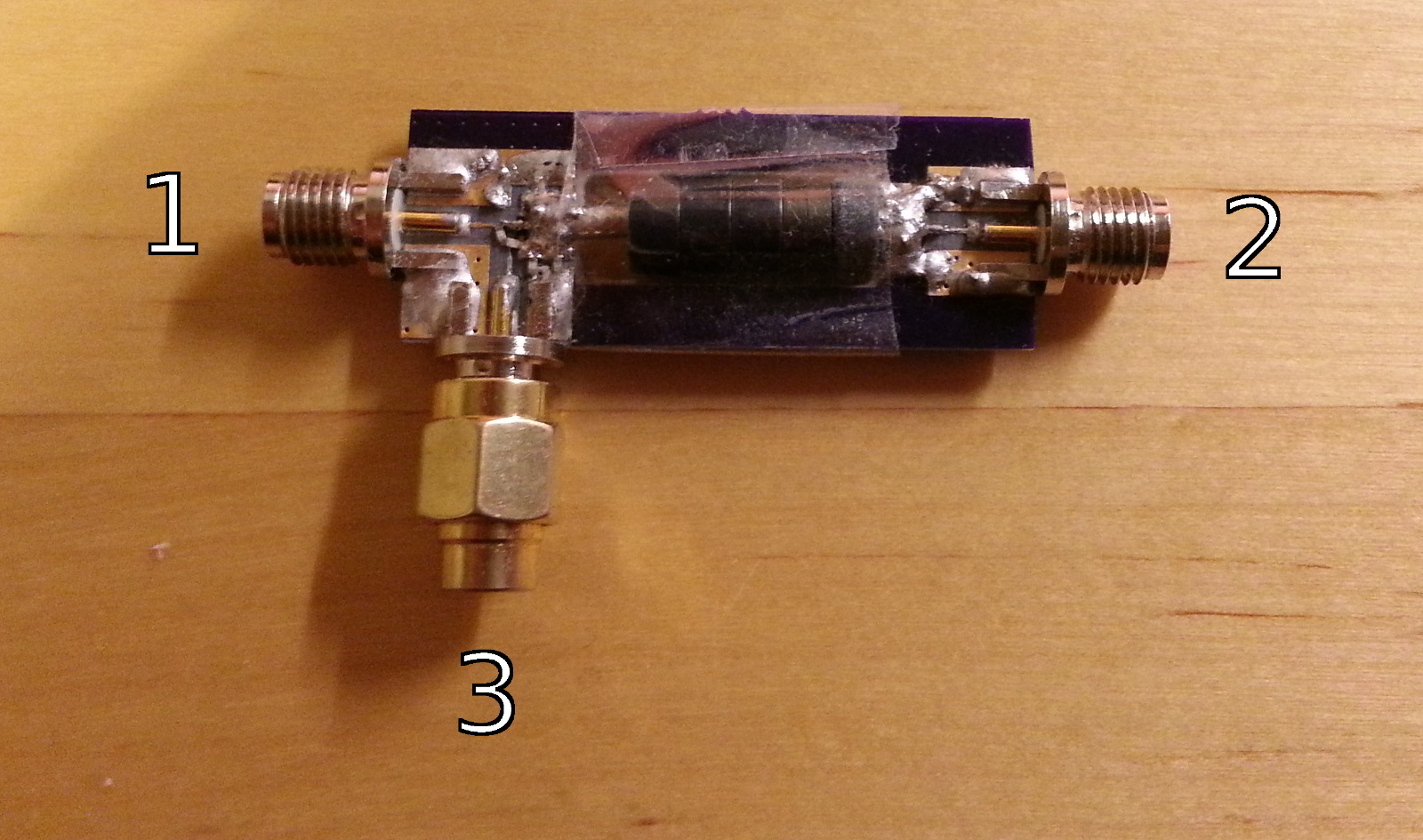

带有端口标记的电阻式桥接器。港口 3 带负载端接。

我制作了三个桥接器,两个用于端口 1,所以留下一个 量过的。上面是带有端口标记的耦合器的图片。在图片中 端口 3 以负载端接,因此可以使用两个端口 VNA 进行测量。 端口 1 到端口 2 是低损耗的直通路径。端口 1 到端口 3 正在耦合 具有 16 dB 损耗的路径。端口 2 到端口 3 是低电平的隔离路径 耦合。

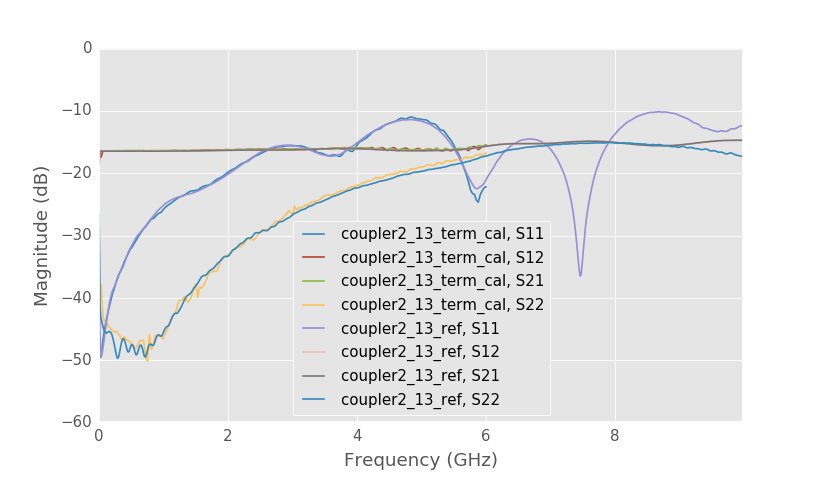

耦合器端口 1 到端口 3,端口 2 端接。

上图是耦合器的两个端口 S 参数,用 我的 300 欧元 VNA 使用 5 欧元的自制校准套件("coupler2_13_term_cal"轨迹) 进行校准 以及使用 5 000 欧元校准套件校准的商用 100 000 欧元 VNA ("coupler2_13_ref"痕迹)。虽然我的测量噪音要大得多,但迹线是一致的 非常接近。

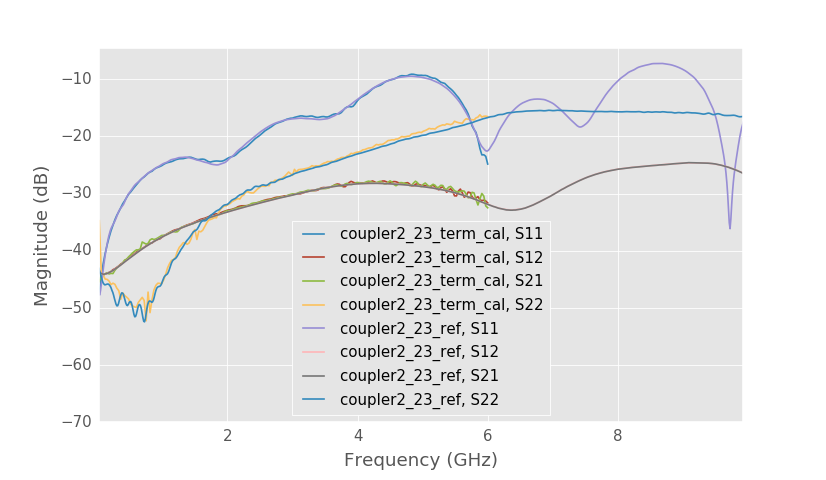

耦合器端口 2 到端口 3,端口 1 端接。

端口 2 到端口 3 的测量也非常一致。如果您比较这些测量值 对于之前介绍的,您会注意到方向性没有那么好。原因 是这些测量是用非常便宜的端接进行的,该终端具有 更高的反射系数。在方向性测量中,端接 端口反映了一些功率,并且测量的 S21 比它大 一个完美的终止。

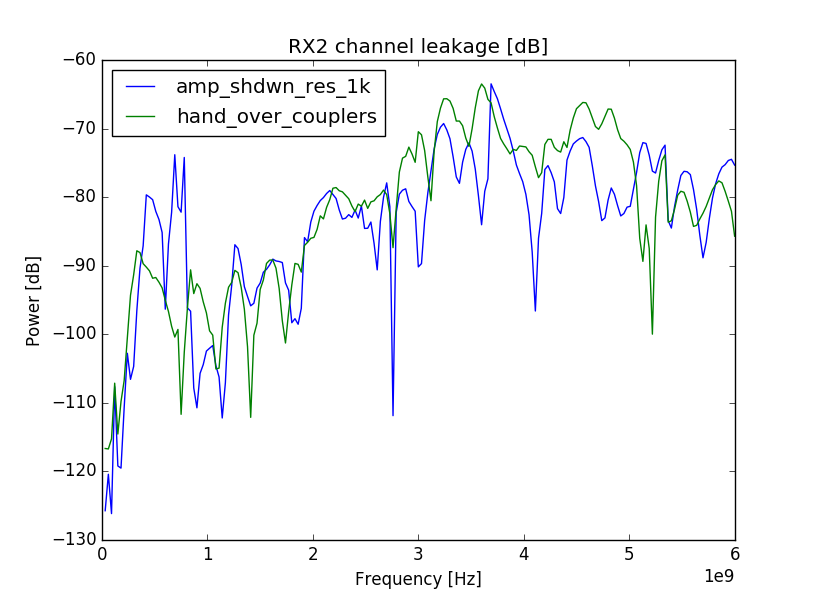

隔离

VNA 的隔离性能并没有我希望的那么好。 我之前就知道,如果没有非常好的表现,我就无法获得最好的表现 屏蔽,但我想避免它,因为好的屏蔽太贵了。看来 大部分泄漏是从源到接收器的辐射泄漏,但 接收器通道之间的泄漏也比预期的要多。我确实尝试过 找到并修复一些最糟糕的无意天线。

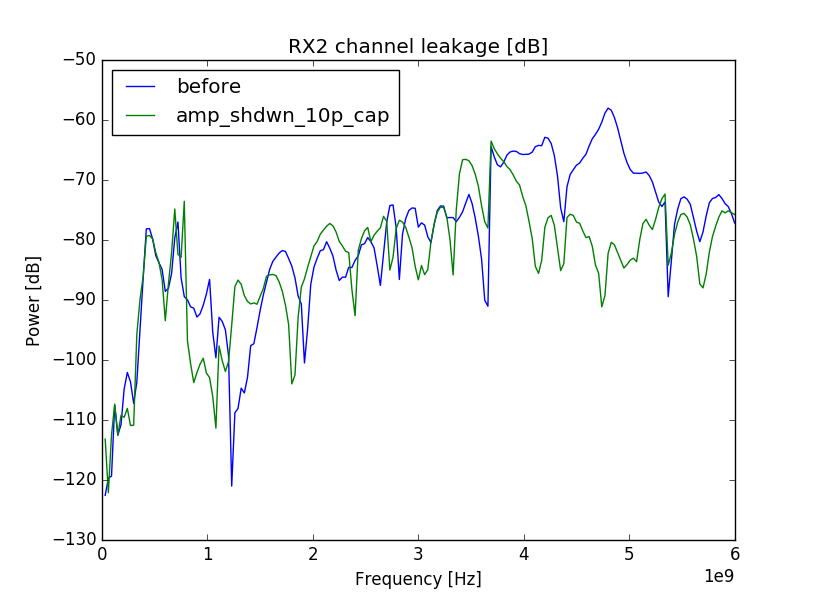

端口 2 参考通道 (RX2) 使用 端口 1 上的源。放大器关断时带和不带 10 pF 电容器 跟踪。

源放大器有一个关断引脚,连接到 FPGA 并在顶部布线 PCB层长距离。我在附近放置了一个 100 欧姆的电阻器 放大器引脚,以增加线路的一些损耗。然而事实证明,大约在 5 GHz 关断引脚走线是最大的泄漏源。添加 10 pF 后 电容器从走线到地的泄漏在5 GHz时下降了20 dB。

放大器关断走线、串联电阻和 添加了电容器。右侧的细长迹线是关机迹线。源 放大器是左下角的 IC。

端口 2 参考通道 (RX2) 使用 端口 1 上的源。有和没有交出耦合器电缆。

在大约 700 MHz 时,泄漏图中还有另一个峰值。这个好像是 由外部耦合器引起。如果我把手放在两个耦合器上 泄漏衰减约 20 dB。

还有更多类似的无意天线,我无法全部修复。 我想提高隔离度的唯一方法是屏蔽每个子系统和 最好甚至在不同的 PCB 上制作它们。

稳定性

在上面的视频中,您可以看到在棋盘上挥手如何影响 接收器读数。源频率为 6 GHz,连接到端口 1 导致端口 1 通道 RX1 和 A 上的高读数。测试电缆是 打开,因此理想情况下,RX2 和 B 通道不应有任何电源进入它们。 然而,由于泄漏,在 RX2 和 B 通道处检测到一些功率。移动我的 手根据反射的泄漏是否升高或降低检测到的泄漏 来自我手的信号与其他泄漏路径同相或异相。

S11 测量也受到隔离的影响。绝对效果是 较小,因为信号较大,但我可以对 S11 读数产生大约影响 从大约 0.5 m 外将我的手移到 VNA 上,可产生 0.01 dB。如果带宽是 100赫兹。

痕迹噪声在开头的绘图中也可见。约为0.002分贝 这相当不错,但由于隔离迹线噪声较差 测量值要高得多。在良好的隔离下,迹线噪声将大约 该水平也适用于测量的 S 参数。

结论

新版本的 VNA 比以前的版本准确得多。 接收器非常准确,动态范围很好,但和上一个版本一样 隔离限制了性能。PCB 周围的金属外壳将有助于 稳定性,应提高测量精度。带外壳、防护罩 围绕单独的 PCB 测量上的各个子电路和接收器 准确性应该要好得多。