1. AXI-AP 概述

AXI-AP(AXI Access Port)实现了MEM-AP架构,用于直接连接到AXI内存系统。通过合适的桥接组件,也可以连接到其他内存系统。

2. 时钟与复位

2.1 时钟域配置

AXI-AP在单一时钟域运行,该时钟必须同时用于DAPBUS接口和AXI接口。

2.2 复位特性

AXI-AP的时钟和复位信号包括:

-

clk:时钟信号

-

resetn:低电平有效复位信号,异步断言,同步解除

复位影响:

-

复位时整个AXI-AP模块被重置,事务历史丢失

-

ARM不建议在AXI传输过程中断言复位,但AXI-AP允许此操作(需知会丢失所有事务历史)

3. 功能接口

AXI-AP包含三个主要总线接口:

-

DAPBUS从接口:连接到DAPBUS互连

-

认证从接口

-

AXI4主接口

4. AXI-AP核心特性

4.1 特性列表

| 特性 | 说明 |

|---|---|

| AXI4接口支持 | - |

| 自动递增TAR | - |

| 停滞访问 | - |

| 访问大小 | 8、16、32或64位 |

| 字节序 | 小端格式 |

| 错误响应 | - |

| 打包传输 | - |

| ROM表指针寄存器 | - |

| 长地址支持 | - |

5. 传输中止与错误处理

5.1 DAP传输中止

当DP通过DAPBUS接口发出中止时:

-

AXI-AP立即完成其DAPBUS从接口上的事务

-

不取消正在进行的AXI传输

5.2 错误响应机制

5.2.1 AXI发起的错误响应

-

AXI主接口接收的错误响应在传输完成时传播到DAP总线

-

64位数据传输需要两次DAP总线访问:

-

读取:DAP总线的第一次读取请求在AXI接口上发送读取请求

-

写入:只有在DAP总线上收到两次写入请求后,才在AXI接口上发送写入访问

-

错误响应分配:

-

读取请求的错误响应针对DAP总线的第一次读取请求

-

写入请求的错误响应针对DAP总线的第二次写入请求

5.2.2 AP发起的错误响应

中止后的AXI-AP写入:

-

DP发起中止操作后,如果外部传输仍挂起(TrInProg位保持高电平),所有对AXI-AP的写入都返回可忽略的错误响应

-

在系统传输完成且TrInProg位设置为0之前,AXI-AP写入持续返回错误

64位AXI读取后的AXI-AP读取:

-

DAP总线的读取请求必须访问BDx寄存器对的两个寄存器,且必须先访问编号较低的寄存器

-

对于DRW,需要两次写入请求才能从AXI接口获取完整的64位字

-

所有其他访问(如读取后跟写入到相同或不同寄存器)都会向DP返回错误响应

5.2.3 特殊情况处理

64位写入序列中断后的写入:

-

DAP接口的写入请求必须访问BDx寄存器对的两个寄存器,且必须先访问编号较低的寄存器

-

对于DRW,需要两次写入请求才能在AXI接口上构建64位数据包作为写入数据

-

所有其他访问(如写入后跟另一个读取-写入到不同寄存器)返回错误响应

示例:

-

访问DRW后,DAP总线的下一次访问必须是写入DRW,任何其他访问返回错误响应

-

访问BD0后,下一次访问必须是写入BD1,任何其他访问返回错误响应

中止的AXI屏障事务:

-

可以中止尚未完成的屏障事务

-

生成中止请求时,DAPBUS事务在下一个周期完成,但CSW.TrInPrg位保持设置,表示AXI接口正忙等待事务完成

-

AXI接口忙时,对DRW或BDx寄存器的读取-写入请求(导致AXI接口上的事务)会使AXI-AP向DP返回错误响应

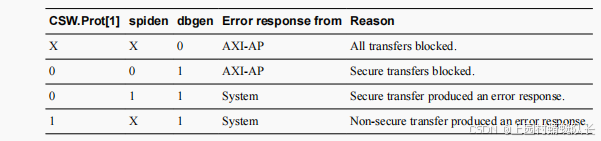

5.2.4 AXI和AP发起的错误响应区分

如果DAPBUS从接口上给出错误响应且CSW寄存器中的TrInProg为低电平,错误来自:

-

系统错误响应(如果dbgen和spiden允许启动传输)

-

AXI-AP错误响应(如果dbgen和spiden不允许传输)

表 AXI和AP发起的错误响应区别:

如果给出错误响应且TrInProg为高电平,则错误来自访问端口错误响应。这种情况只能在启动中止后系统传输未完成时发生。

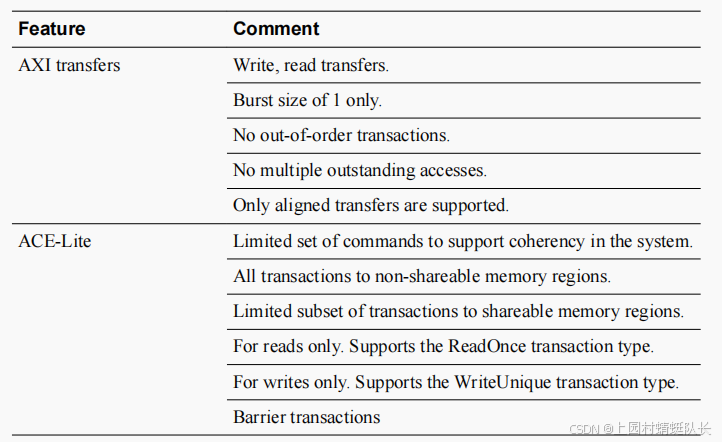

6. AXI传输特性

6.1 基本特性

AMBA4 AXI兼容主端口支持的特性:

-

仅支持单次传输突发

-

按发出顺序一次处理一个事务

-

不支持乱序事务

-

不发出多个未完成地址

6.2 传输参数详细说明

突发长度:

-

ARLEN[3:0]和AWLEN[3:0]始终为0b0000(单次传输)

-

打包的8位或16位传输在AXI接口上被视为单个突发长度为一次的传输

突发大小:

- 支持8位、16位、32位、64位

突发类型:

-

ARBURST和AWBURST信号始终为0b01

-

在单次传输上下文中,突发类型无实际意义

原子访问:

-

仅支持正常访问

-

ARLOCK和AWLOCK信号始终为0b00

6.3 地址对齐要求

不支持未对齐访问,地址必须根据传输大小对齐:

对齐规则:

-

16位传输:半字对齐

-

32位传输:字对齐

-

64位传输:双字对齐

具体示例:

-

16位半字传输:

-

基地址0x01被对齐,AxADDR[7:0] = 0x00

-

基地址0x02被保留,AxADDR[7:0] = 0x02

-

-

32位字传输:

-

基地址0x01到0x03被对齐,AxADDR[7:0] = 0x00

-

基地址0x04被保留,AxADDR[7:0] = 0x04

-

-

64位双字传输:

-

基地址0x04被对齐,AxADDR[7:0] = 0x00

-

基地址0x08被保留,AxADDR[7:0] = 0x08

-

7. 打包传输

7.1 基本概念

-

DAPBUS接口是32位数据总线,但可根据CSW寄存器中的大小字段形成8位或16位传输

-

CSW寄存器中的AddrInc字段允许优化DAPBUS使用,减少DAP访问次数

-

如果启动打包传输,则自动启用地址递增

-

多个传输在顺序地址中执行,地址增量大小基于传输大小

7.2 传输示例

非打包16位写入:

-

基地址0x2,CSW[2:0] = 0b001,CSW[5:4] = 0b01

-

WDATA[31:16]从DRW寄存器的[31:16]位写入

非打包8位读取:

-

基地址0x1,CSW[2:0] = 0b000,CSW[5:4] = 0b01

-

RDATA[31:16]和RDATA[7:0]为零,RDATA[15:8]包含读取数据

打包字节写入:

-

基地址0x2,CSW[2:0] = 0b000,CSW[5:4] = 0b10

-

发起四次写入传输,发送数据顺序:

-

WDATA[23:16]从DRW[23:16]到AWADDR[31:0] = 0x000000002

-

WDATA[31:24]从DRW[31:24]到AWADDR[31:0] = 0x000000003

-

WDATA[7:0]从DRW[7:0]到AWADDR[31:0] = 0x000000004

-

WDATA[15:8]从DRW[15:8]到AWADDR[31:0] = 0x000000005

-

打包半字读取:

-

基地址0x2,CSW[2:0] = 0b001,CSW[5:4] = 0b10

-

发起两次读取传输:

-

RDATA[31:16]从ARADDR[31:0] = 0x000000002存储到DRW[31:16]

-

RDATA[15:0]从ARADDR[31:0] = 0x000000004存储到DRW[15:0]

-

7.3 DAPREADY信号行为

-

AXI-AP仅在所有来自AXI接口的打包传输完成时才置DAPREADY为高电平

-

如果当前传输中止或当前传输收到ERROR响应,AXI-AP不完成后续打包传输,并在当前打包传输后立即返回DAPREADY高电平

8. AxCACHE与AxDOMAIN有效组合

下表显示了AxCACHE和AxDOMAIN值的有效组合:

| AxCACHE[3:0] | 访问类型 | AxDOMAIN | 域类型 | 有效性 |

|---|---|---|---|---|

| 0000 | 设备 | 00 | 非共享 | 否 |

| 0000 | 设备 | 01 | 内共享 | 否 |

| 0000 | 设备 | 10 | 外共享 | 否 |

| 0000 | 设备 | 11 | 系统 | 是 |

| 0010 | 非可缓存 | 00 | 非共享 | 启用 |

| 0010 | 非可缓存 | 01 | 内共享 | 启用 |

| 0010 | 非可缓存 | 10 | 外共享 | 启用 |

| 0010 | 非可缓存 | 11 | 系统 | 是 |

| 0011 | 非可缓存 | 00 | 非共享 | 启用 |

| 0011 | 非可缓存 | 01 | 内共享 | 启用 |

| 0011 | 非可缓存 | 10 | 外共享 | 启用 |

| 0011 | 非可缓存 | 11 | 系统 | 是 |

| 010x | - | - | - | 否 |

| 100x | - | - | - | 否 |

| 110x | - | - | - | 否 |

| 011x | 写通 | 00 | 非共享 | 是 |

| 011x | 写通 | 01 | 内共享 | 是 |

| 011x | 写通 | 10 | 外共享 | 是 |

| 011x | 写通 | 11 | 系统 | 否 |

| 101x | 写回 | 00 | 非共享 | 是 |

| 101x | 写回 | 01 | 内共享 | 是 |

| 101x | 写回 | 10 | 外共享 | 是 |

| 101x | 写回 | 11 | 系统 | 否 |

| 111x | 写回 | 00 | 非共享 | 是 |

| 111x | 写回 | 01 | 内共享 | 是 |

| 111x | 写回 | 10 | 外共享 | 是 |

| 111x | 写回 | 11 | 系统 | 否 |

9. 技术要点总结

AXI-AP作为连接DAPBUS与AXI系统的关键组件,提供了灵活的存储器访问能力。其主要技术特点包括:

-

单时钟域设计:简化时序分析,提高系统稳定性

-

完善的错误处理机制:支持多种错误场景的检测和处理

-

严格的传输规范:确保数据传输的可靠性和一致性

-

灵活的打包传输:优化小尺寸数据访问效率

-

明确的内存访问规则:包括地址对齐要求和传输大小支持

这些特性使AXI-AP在嵌入式调试和系统开发中具有重要价值,为芯片设计提供了可靠的内存访问解决方案。