一、IP核

IP 核(Intellectual Property Core,知识产权核)是 FPGA 设计中可重用的功能模块,通常由 FPGA 厂商(如 Xilinx)或其他第三方提供。这些模块是预设计的、经过验证的硬件功能单元,可以直接集成到你的 FPGA 设计中,节省开发时间并提高可靠性。

IP 核有如下特点:

-

功能封装 :IP 核实现了特定功能,例如时钟管理(

clk_wiz_0用于生成和分频时钟)、逻辑分析(ila_0用于调试)、数据转换、通信接口(如 UART、SPI)等。 -

可配置性:用户可以通过图形界面或脚本配置 IP 核的参数(如时钟频率、端口数量等),以适应具体设计需求。

-

形式:IP 核通常以 Verilog/VHDL 代码、网表文件或加密格式提供,并包含综合和仿真所需的元数据。

-

Xilinx Vivado 中的 IP 核 :Vivado 提供了一个 IP Catalog,包含大量预定义的 IP 核,用户可以直接使用或定制。

-

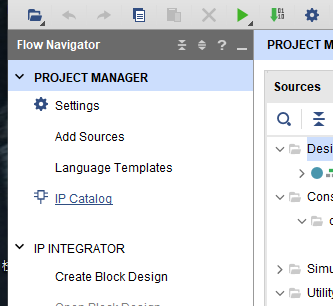

打开 IP Catalog

- 打开你的 Vivado 项目。

- 在 Vivado 的 Flow Navigator (左侧栏)中,点击 IP Catalog (通常位于 Project Manager 部分)。

- 这会打开一个窗口,显示所有可用的 IP 核。

例如:创建 clk_wiz_0 和 IP 核

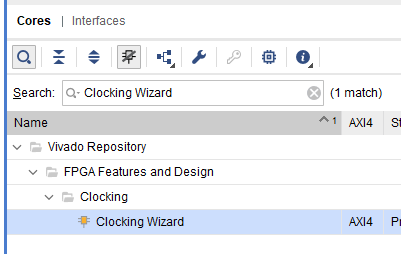

** clk_wiz_0核**用于生成和管理 FPGA 的时钟信号。它基于 FPGA 的时钟资源(如 MMCM 或 PLL)从输入时钟生成一个或多个输出时钟,满足设计中不同模块的时钟需求。

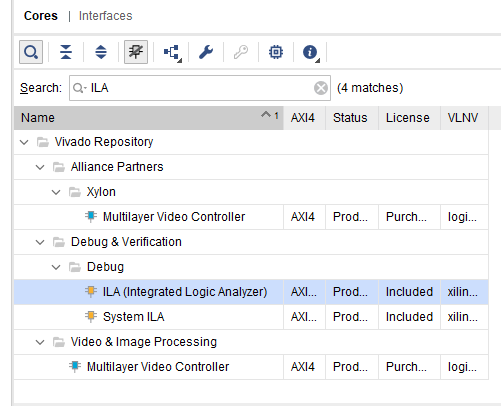

ILA (ila_0)核 用于调试 FPGA 内部信号,捕获和显示 ADC 信号(ad0_data, ad1_data, ad0_otr, ad1_otr)的波形,帮助验证 ADC 功能和定位问题。

-

步骤:

- 在 IP Catalog 搜索框中输入

Clocking Wizard。 - 双击 Clocking Wizard ,或者右键选择 Create IP。

- 在 IP Catalog 搜索框中输入

-

- 在弹出的配置窗口中:

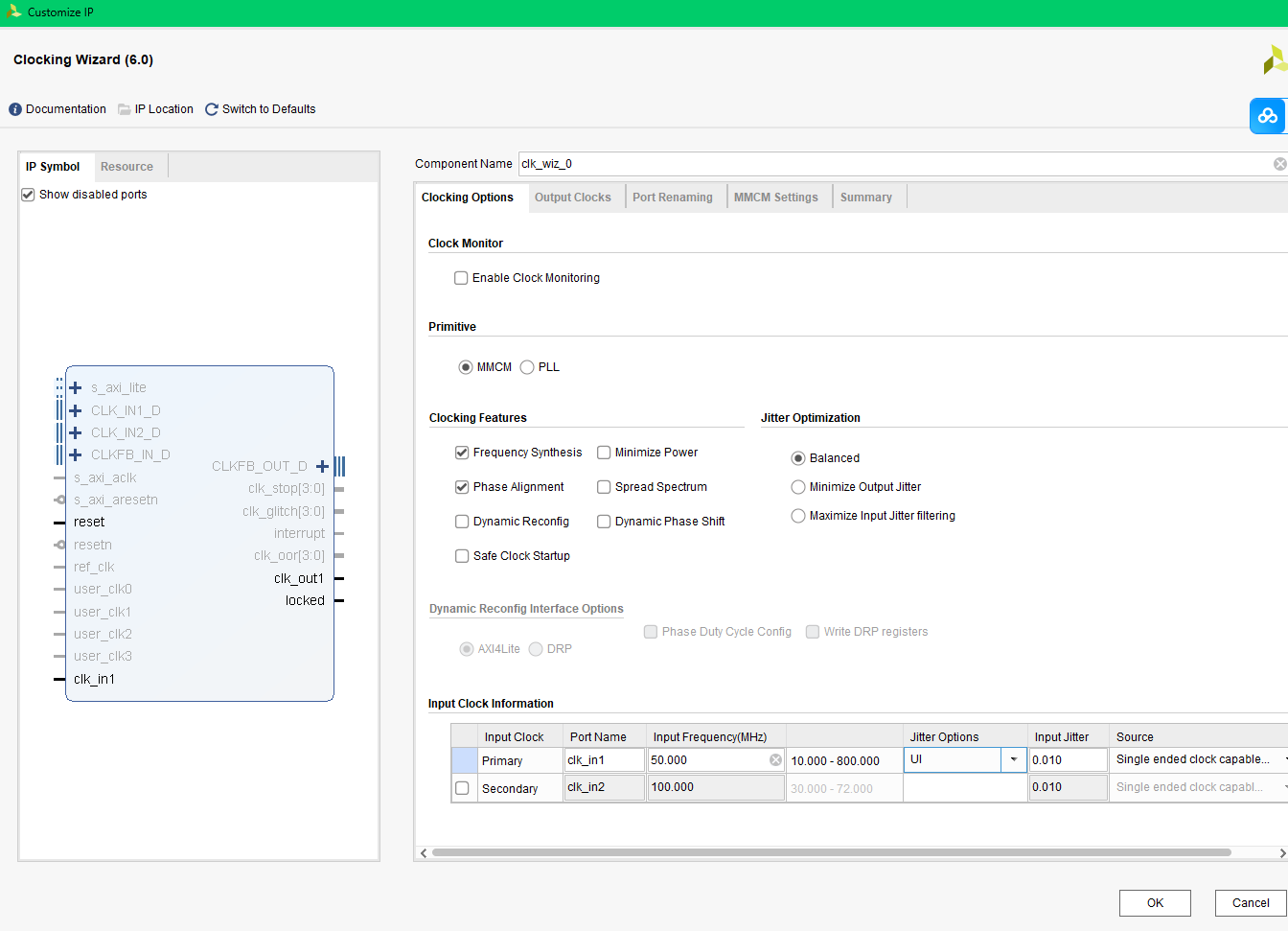

- IP 名称 :默认会生成类似

clk_wiz_0的名称,确保与你的代码中的实例化名称一致(即clk_wiz_0)。 - 时钟配置 :

- Input Clock :设置输入时钟频率。根据 XDC 文件而定(比如我的:

create_clock -period 20.000),输入时钟频率为 50 MHz(20 ns 周期)。 - Output Clocks :配置

clk_out1的输出频率(代码中使用的是clk_out1的话)。如果需要clk_out2,也需配置。

- Input Clock :设置输入时钟频率。根据 XDC 文件而定(比如我的:

- IP 名称 :默认会生成类似

- 在弹出的配置窗口中:

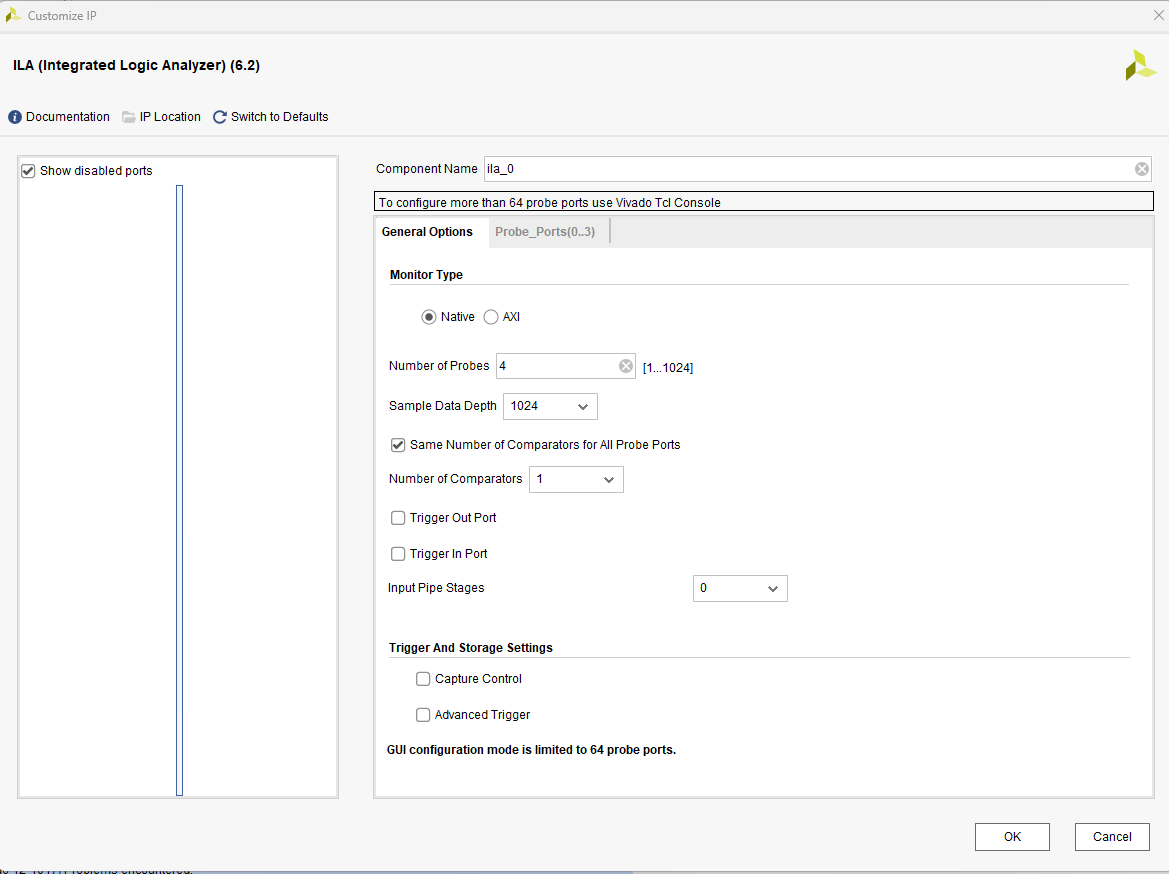

同样的,点击 IP Catalog ,在搜索框中输入 ILA ,选择 Integrated Logic Analyzer。

- 在弹出的窗口中,设置 IP 核名称:

- Component Name :输入

ila_0。

- Component Name :输入

- 配置 ILA 参数(基于

ila_0实例化代码):- General Options 页面:

- Number of Probes :设置为

4(匹配probe0到probe3)。 - Sample Data Depth:选择默认值(如 1024)或根据需求调整(用于存储捕获的数据深度)。

- Number of Probes :设置为

- General Options 页面:

- 描述:设置 ILA 的探针端口数量,用于连接需要监控的信号。

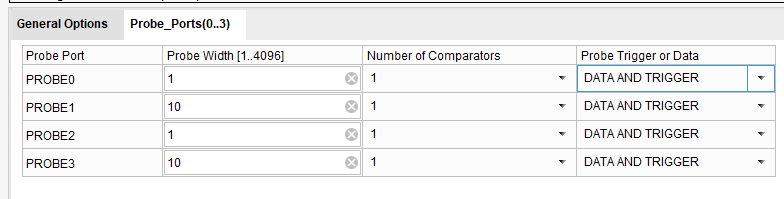

- 窗口显示 :当前设置为

4,范围为[1..1024]。 - 推荐设置 :保持为

4。probe3:10-bit(ad1_data)probe2:1-bit(ad0_otr)probe1:10-bit(ad0_data)probe0:1-bit(ad1_otr)- 如果需要监控更多信号,可以增加探针数量,配置要匹配代码。

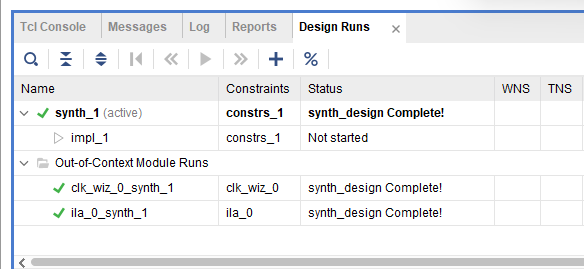

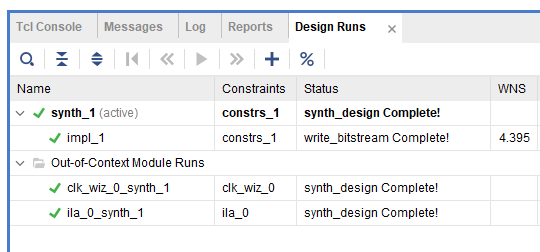

这样配置完之后,Run Synthesis是可以通过的

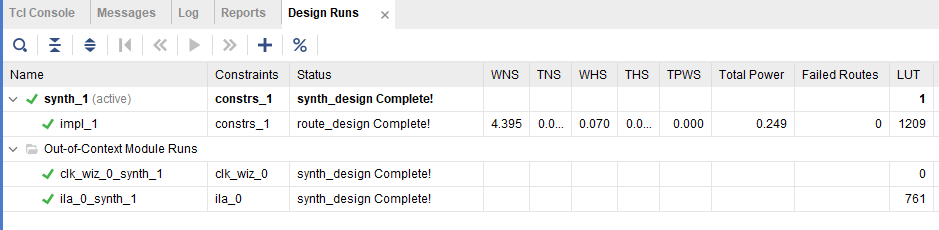

再Run Implementation,需要等一会儿

- 再Generate Bitstream

二、组成部分

ZYNQ7020(型号通常为 XC7Z020)由以下两个主要部分组成:

- 处理系统(PS,Processing System):基于 ARM Cortex-A9 的双核处理器,负责运行嵌入式软件、操作系统(如 Linux)或裸机程序。

- 可编程逻辑(PL,Programmable Logic):基于 Xilinx 7 系列 FPGA 的可编程逻辑资源,用于实现定制硬件逻辑。

- PS-PL 交互接口:通过 AXI(Advanced eXtensible Interface)总线实现 PS 和 PL 之间的高效通信。

详细分析如下:

1、处理系统(PS,Processing System)

PS 是 ZYNQ7020 的处理器部分,基于 双核 ARM Cortex-A9 MPCore,运行频率高达 667 MHz(具体频率因型号和配置而异)。它是一个功能完整的嵌入式处理系统,包含以下关键组件:

1. ARM Cortex-A9 处理器

- 架构:双核 ARM Cortex-A9,32 位 RISC 处理器,支持 ARMv7-A 指令集。

- 特性 :

- 每个核具有独立的 L1 缓存(32 KB 指令缓存 + 32 KB 数据缓存)。

- 共享 512 KB 的 L2 缓存。

- 支持 NEON 扩展(用于 SIMD 运算)和浮点单元(FPU)。

- 可运行 Linux、实时操作系统(如 FreeRTOS)或裸机程序。

- 用途:运行操作系统、应用程序、管理外设、处理复杂算法等。

2. 存储控制器

- DDR 控制器:支持 DDR2、DDR3、DDR3L 和 LPDDR2 内存,最大带宽 533 MHz,32 位宽。

- 片上存储器(OCM):256 KB SRAM,位于 PS 内部,可由 ARM 核和 PL 访问,低延迟。

- NAND/NOR 闪存控制器:支持外部 NAND、NOR 闪存或 Quad-SPI 存储,用于存储引导程序或数据。

3. 外设接口

PS 集成了丰富的标准外设接口,用于与外部设备通信:

- 以太网控制器:2 个千兆以太网 MAC,支持 IEEE 1588。

- USB 控制器:2 个 USB 2.0 OTG 控制器。

- SD/SDIO 控制器:2 个 SD/SDIO 接口,支持 SD 卡存储。

- SPI 控制器:2 个 SPI 接口。

- I2C 控制器:2 个 I2C 接口。

- UART 控制器:2 个 UART 接口,用于串口通信。

- CAN 控制器:2 个 CAN 总线接口。

- GPIO:54 个 GPIO 引脚,可由 PS 直接控制,也可通过 PL 扩展。

4. 中断控制器

- 通用中断控制器(GIC):管理 PS 和 PL 之间的中断,支持多优先级中断处理。

- 用途:处理外部设备中断、PS 内部中断或 PL 发送的中断。

5. 时钟和电源管理

- 时钟管理单元(CMU):为 PS 和 PL 提供灵活的时钟配置,支持多个时钟源(如外部晶振、PLL)。

- 电源管理:支持低功耗模式,动态调整 PS 和 PL 的电源状态。

6. DMA 控制器

- 直接内存访问(DMA):支持高效的数据传输,减少 ARM 核的负担。

- 中央 DMA 和外设 DMA:用于 PS 内部数据搬移和外设数据传输。

7. 系统级控制单元

- 配置和安全单元:管理芯片的启动、配置和安全功能(如加密引导)。

- JTAG 接口:用于调试和配置 PS 和 PL。

2、可编程逻辑(PL,Programmable Logic)

PL 是 ZYNQ7020 的 FPGA 部分,基于 Xilinx 7 系列 Artix-7 架构,提供灵活的硬件加速和定制能力。对于 ZYNQ7020(XC7Z020),PL 的资源包括以下内容:

1. 逻辑资源

- 逻辑单元(Logic Cells):约 85,000 个逻辑单元(具体为 85,120 LCs)。

- 查找表(LUTs):约 53,200 个 LUTs,用于实现组合逻辑。

- 触发器(Flip-Flops):约 106,400 个触发器,用于时序逻辑。

2. 块存储器(Block RAM)

- 容量:4.9 Mb(560 KB)的 Block RAM。

- 用途:存储数据、缓冲区或实现 FIFO、RAM 等。

3. 数字信号处理(DSP)单元

- DSP 切片:220 个 DSP48E1 单元。

- 功能:支持高性能数字信号处理,如乘法、累加、滤波等。

4. 时钟管理

- 时钟管理模块(CMT):包含 PLL(锁相环)和 MMCM(混合模式时钟管理器),用于生成灵活的时钟信号。

- 时钟网络:支持全局和区域时钟分配。

5. I/O 资源

- 可编程 I/O(SelectIO):约 200 个 I/O 引脚(具体数量取决于封装,例如 CLG400 封装为 200 个)。

- 支持标准:支持 LVCMOS、LVDS、HSTL 等多种 I/O 标准,电压范围 1.2V 至 3.3V。

- 用途:连接外部设备,如 LED、按钮、传感器、显示器等。

6. 其他资源

- XADC(模拟数字转换器):12 位、1 MSPS 的 ADC,用于模拟信号采集。

- 配置逻辑 :支持通过 JTAG、SPI 或 PS 配置 PL 的比特流。