有一段时间没有写技术文章了,目前投入SI/PI领域约一年的时间。这次想先分享一下平面对高速讯号的影响。

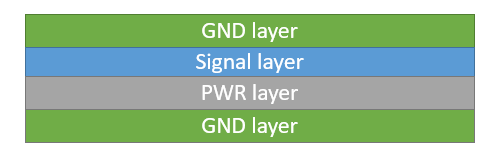

在PCIe传输布局中,对CEI插件插槽的厚度为0.062英寸。由于厚度的限制,造成在PCB叠构设计上讯号也参考到电源平面[1]。相反有时候在PCB的布线上并不总是可以参考GND平面,由于叠构厚度缩小也将PWR平面做为参考平面,如下图。

4 层堆叠

在线路的传输布线上其实只有一个概念,就是、让阻抗可控制。但高速在PWR平面上经常遇到的情况就是塔平面(分割参考平面),主要是由于器件所需的电压不同,需要把PWR平面作分割。会造成传输路径上的回流路径(返回路径存在)不连续点。在低频传输上可能影响不大,但在高频时回流路径不走最短路径,而阻抗最低的路径,将提高回流路径之一致性。

塔楼对讯号的影响

主要会造成讯号衰减 和串扰效应。

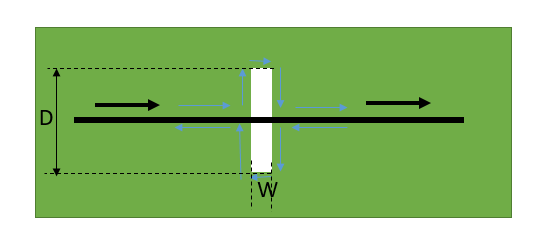

在经过塔柱平面讯号会受到塔柱的电性效应(或电流),会增加讯号的上升(下降)时间。D 塔电感越大,W 越大,影响在信号电压的连续性。

塔顶平面上信号与回流路径

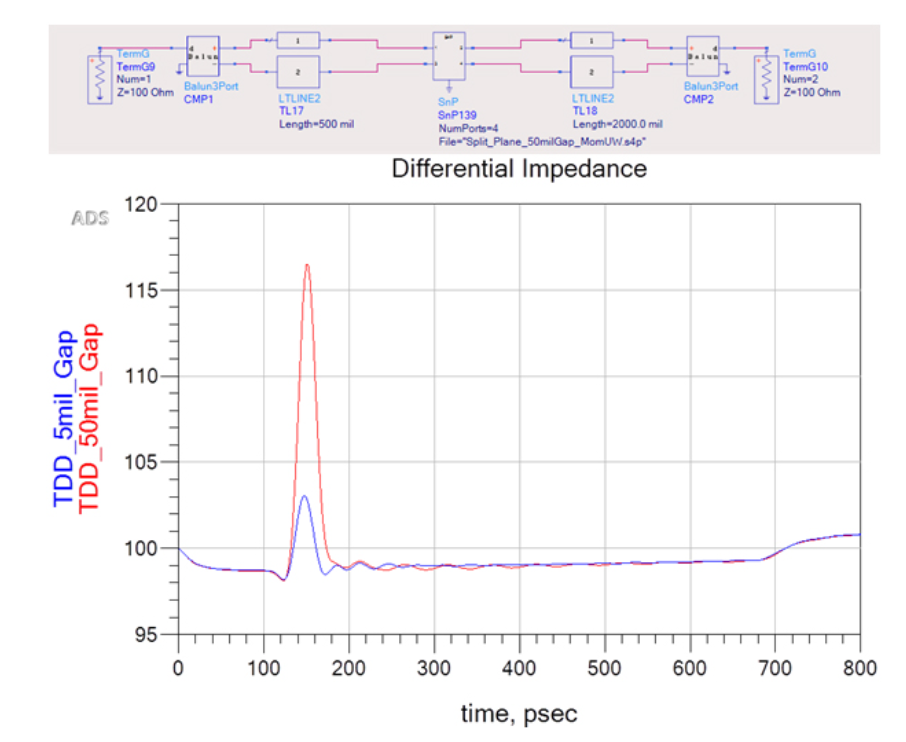

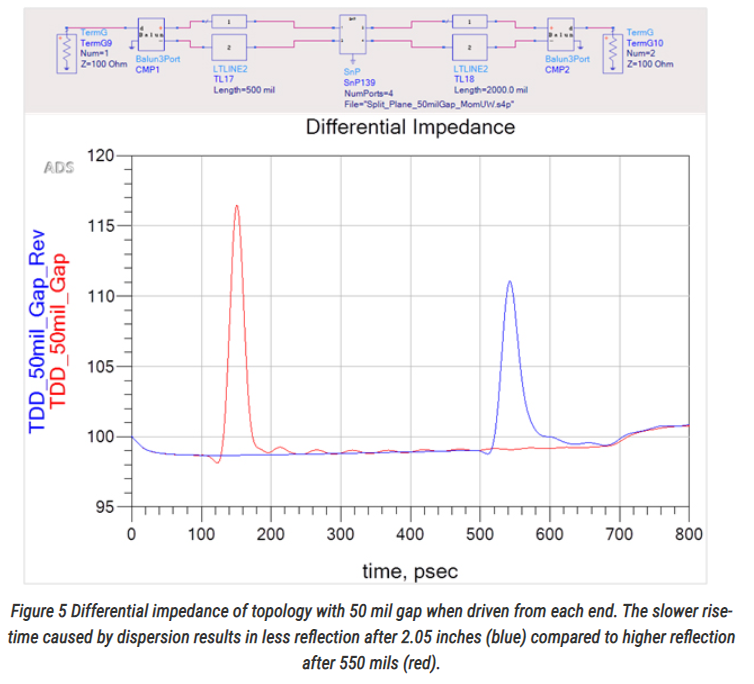

在"分割平面以及微带信号交叉时会发生什么"一文中有提到塔的大小对阻抗的影响,可以看到塔的间隙增大,阻抗增益。

阻抗和分裂空隙尺寸[2]

另外就是上升时间的增加与反射损耗的影响。

信号效应[2]

另外一个主要影响就是增加对其他传输线干扰的风险,由于回流路径的改变,交叉到其他传输线的路径造成讯号衰减。

支架平台风险增加串扰

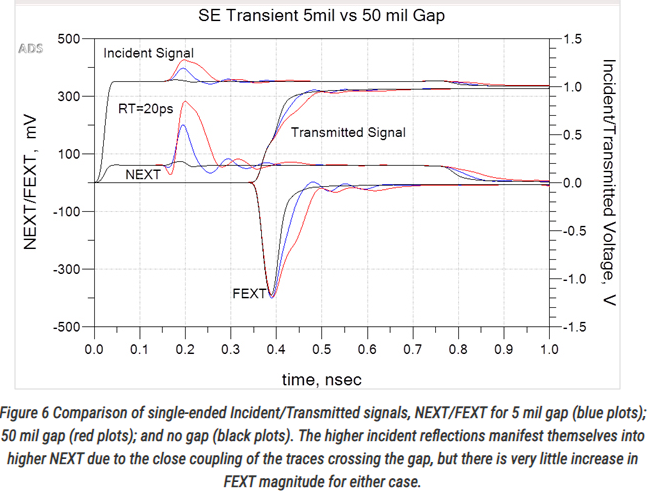

在SE的模拟上可以看到,矮塔的大小对于其他传输线的扰串影响。在接下来的对于讯号有过冲(overshoot)的现象,矮塔越大Peak越大。在FEXT上相对只是下降时间有变缓的趋势。

串扰效应 [2]

最后提供了一些方法来改善 PWR 平面遇到的塔问题。

- 避免将高速讯号线走在塔台上,就这样。这个概念就是要"避免某件事情发生,就是不要让那件事情发生。"

- 串扰问题可以遵循三倍线原则,当然时间允许可以模拟确认一下大小

- 如果讯号走内层,那就把叠构设计讯号做成靠GND平面近一点(当然GND平面未必没有支架存在,那就是设计上的问题让高速讯号有完整的参考平面)