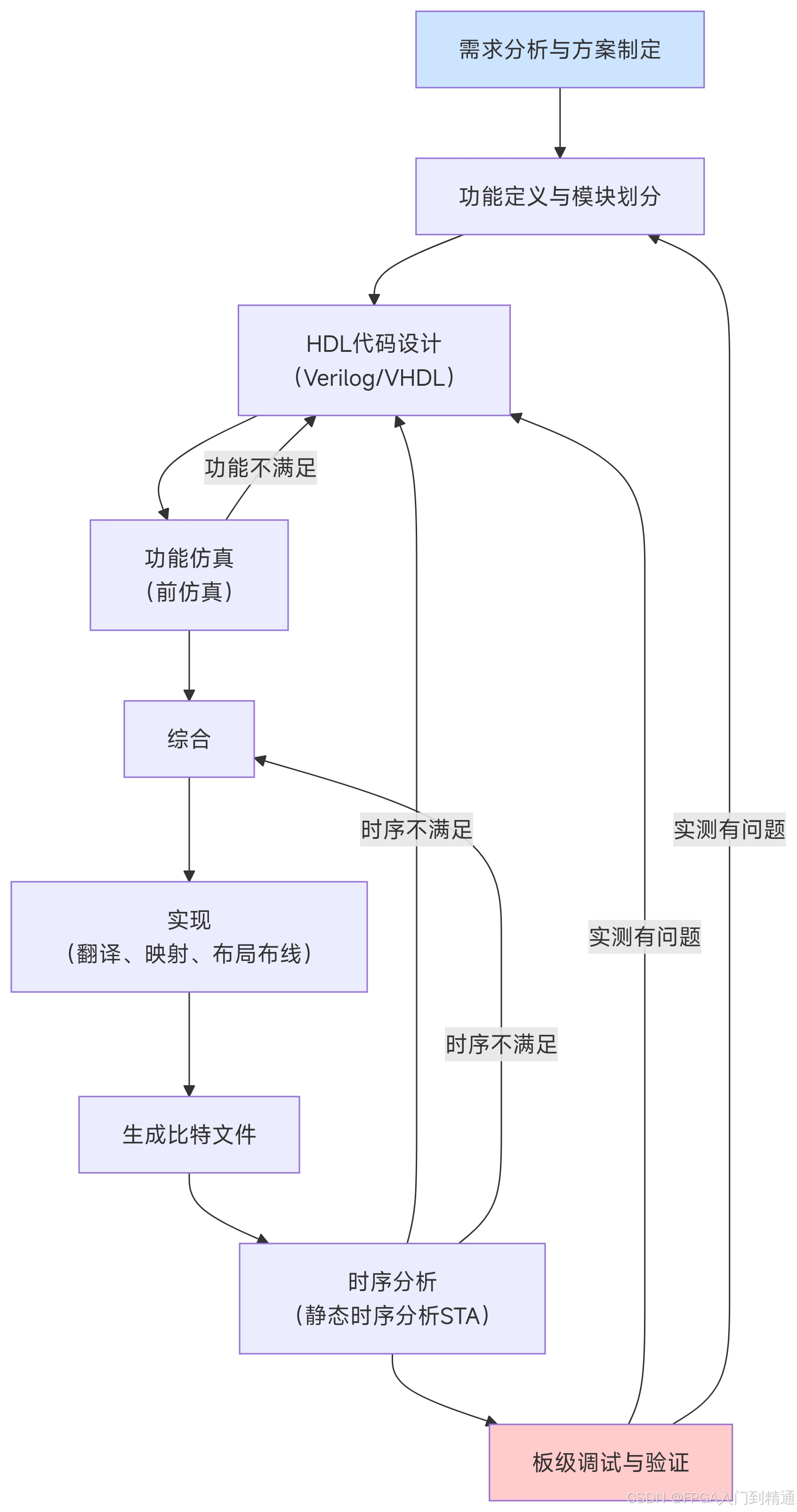

FPGA 的传统开发流程,通常被称为 "RTL 到比特流" 的设计流程,是 FPGA 开发中最基础、最核心的步骤。

整个流程可以分为以下几个主要阶段,下图清晰地展示了这一循序渐进的过程:

1、需求分析与方案制定

这是所有工作的起点,也是最容易,被忽视但至关重要的一步。

- 目标: 明确设计要实现的功能、性能指标和接口要求。

- 主要工作:

- 需求分析: 理解系统需求,分析具体的功能。

- 架构设计: 确定数据流、控制流和模块间的接口方式(如握手协议、FIFO等)。

- 资源评估: 估算所需的逻辑单元、存储器、DSP块和I/O引脚数量,以选择合适的FPGA芯片。

- 时钟规划: 设计时钟域,确定时钟频率和来源,处理跨时钟域问题。

- 输出: 设计规格书、系统架构图、硬件设计方案。

2. 功能定义与模块划分

这一步设计具体的系统架构方案。

- 主要工作: 采用"自顶向下"的设计方法,将整个系统划分为多个功能子模块(如时钟管理、数据采集、数据处理、协议封装等)。并明确定义每个模块的接口和功能。

- 输出: 模块划分文档、接口定义文档。

3. HDL代码设计

将设计思路用硬件描述语言或原理图的形式表达出来。

- 主要工作:

- 编写HDL代码: 使用 Verilog 或 VHDL 编写各个模块的代码。这是最主流的方式。

- 创建原理图: 对于一些简单的逻辑或使用厂商提供的IP核。可能会用到图形化的原理图输入方式,比如vivado的block design。

- IP核集成: 调用FPGA厂商提供的IP核(如FIFO、PLL、DDR控制器、PCIe接口等),并对其进行配置。

- 输入: 设计规格书、架构图。

- 输出: Verilog/VHDL源文件、约束文件(初步)、IP核配置文件。

- 常用工具: 任何文本编辑器(如VS Code、Sublime Text)、Vim,以及厂商IDE自带的编辑器。

4. 功能仿真

在代码编写完成后,进行逻辑功能的验证,确保代码的行为符合设计预期。

- 主要工作:

- 编写Testbench: 创建一个独立的仿真模块,为被测设计提供激励信号(如时钟、复位、输入数据),并检查其输出是否正确。

- 运行仿真: 使用仿真工具执行Testbench,观察波形图。

- 调试: 如果功能不正确,返回设计输入阶段修改代码,然后重新仿真,直到功能完全正确。

- 输入: RTL代码、Testbench代码。

- 输出: 仿真波形图、功能验证报告。

- 常用工具:

- Mentor Graphics (Siemens EDA): ModelSim/QuestaSim (行业标准)

- Synopsys: VCS

- Cadence: Xcelium

- Aldec: Riviera-PRO / Active-HDL

- 开源: Icarus Verilog, GHDL (配合GTKWave)

5. 综合

将RTL代码转换为FPGA底层的基本逻辑单元(如查找表LUT、触发器FF、布线资源等)构成的网表,

- 主要工作:

- 翻译: 将HDL代码解析为中间表示。

- 优化: 对逻辑进行优化,如逻辑化简、状态机优化等。

- 映射: 将优化后的逻辑映射到目标FPGA器件的特定硬件资源上(例如,一个4输入与门映射到一个LUT)。

- 输入: 经过功能仿真的RTL代码、约束文件(包含时钟定义、I/O引脚分配等)。

- 输出: 综合后的网表文件(通常是EDIF或NGC格式)。

- 常用工具:

- Xilinx (AMD): Vivado Synthesis

- Intel (Altera): Quartus Prime Synthesis

- 第三方: Synplify Pro (以其出色的优化效果而闻名)

6. 实现

将综合生成的网表"放置"到FPGA的物理位置上,并"连接"好它们之间的布线。

完成逻辑单元的布局和布线。生成可以下载到FPGA中的物理布局信息。

- 主要工作:

- 翻译: 将综合后的网表和约束文件转换为更底层的描述。

- 映射: (在某些流程中,这一步与综合的映射合并或在此处细化)。

- 布局: 确定每个逻辑单元在FPGA芯片上的具体物理位置。

- 布线: 在逻辑单元之间建立物理连接通道。

- 输入: 综合后的网表、约束文件。

- 输出: 布局布线后的设计文件(包含详细的物理位置和延迟信息)。

- 常用工具: 厂商IDE自带(Vivado Implementation, Quartus Prime Fitter)。

7. 时序分析

在布局布线完成后,对设计进行精确的时序验证,确保电路能在目标时钟频率下正常工作。

- 目标: 验证设计是否满足所有的时序要求,特别是建立时间和保持时间。

- 主要工作:

- 静态时序分析: EDA工具会根据布局布线后得到的精确延迟信息,分析每一条路径的时序。

- 检查报告: 查看时序报告,找出所有不满足时序要求的路径。

- 迭代优化: 如果时序不满足,需要返回综合或实现阶段,通过修改约束、调整综合策略或修改RTL代码(如增加流水线)来重新优化,直到时序收敛。

- 输入: 布局布线后的设计、时序约束文件。

- 输出: 时序分析报告。

- 常用工具: 厂商IDE内置的STA工具(Vivado Timing Report, Quartus Prime TimeQuest Analyzer)。

8. 生成比特文件

当时序和功能都满足要求后,生成可以下载到FPGA芯片中的比特流文件。

- 目标: 将布局布线后的设计信息转换为FPGA可以识别的二进制配置文件。

- 主要工作: 运行"生成比特流"工具。

- 输入: 布局布线后且时序通过的设计。

- 输出: 配置文件。

- Xilinx: .bit 文件 (用于JTAG下载), .bin 文件 (用于Flash配置)

- Intel: .sof 文件 (用于JTAG下载), .pof 文件 (用于Flash配置)

9. 下载与调试

将生成的配置文件下载到实际的FPGA硬件板上,并进行在线调试。

- 目标: 在真实硬件上验证设计的最终功能。

- 主要工作:

- 硬件连接: 通过JTAG接口将PC和FPGA开发板连接起来。

- 下载: 使用下载工具将.bit或.sof文件烧录到FPGA的SRAM中。

- 在线调试: 如果出现问题,使用FPGA厂商提供的调试工具。

- Xilinx: ChipScope (较老) / Vivado Logic Analyzer (集成在Vivado中)

- Intel: SignalTap (集成在Quartus中)这些工具可以将FPGA内部的信号实时抓取出来,在PC上显示波形,类似于一个"硬件示波器"。

- 输入: 配置文件、FPGA开发板。

- 输出: 在硬件上运行的设计、调试波形。

- 常用工具: Vivado Hardware Manager, Quartus Prime Programmer。

如果需要更多学习资料和源码,想要学习FPGA实战入门进阶,请阅读下面这篇文章:

往期阅读: