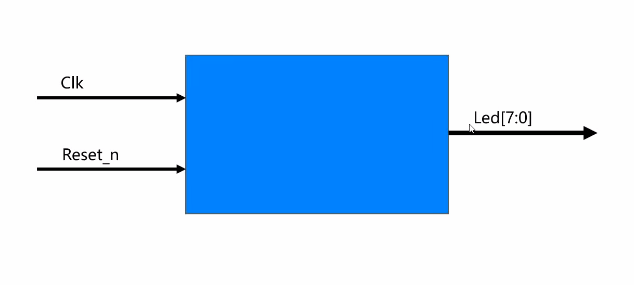

一、原理

- 时钟信号

- 复位信号

- 输出管脚,位宽为8,因为要点亮8个灯

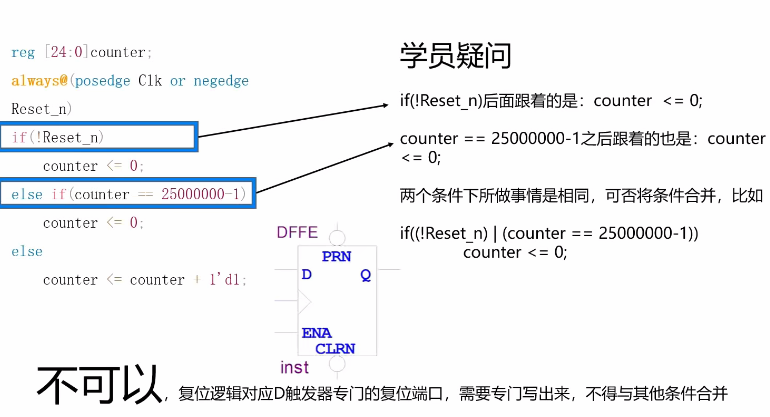

二、注意

1.

2.

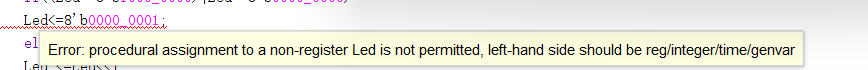

将光标拖到红线处可以提示报错信息

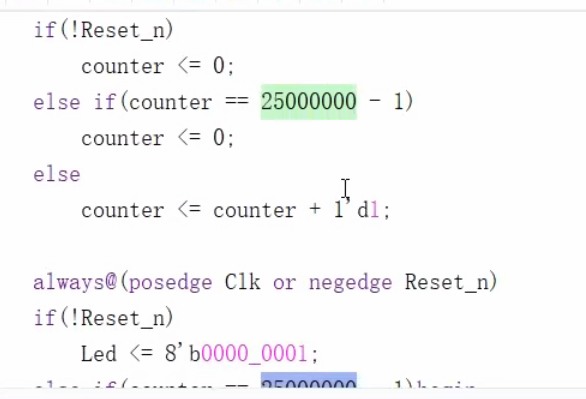

3.

这个25000000-1值影响仿真速度,在仿真时少些时间,将500ms变成了5000us

三、源文件

verilog

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/11/07 21:16:22

// Design Name:

// Module Name: led_run

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module led_run(

Clk,

Reset_n,

Led

);

input Clk;

input Reset_n;

output reg [7:0]Led;

reg [24:0] counter;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter <=0;

else if(counter ==25000000-1)

counter<=0;

else

counter<= counter+1'd1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Led <= 8'b0000_0001;

else if(counter ==25000000-1)begin

if((Led==8'b1000_0000)|Led==8'b0000_0000)

Led<=8'b0000_0001;

else

Led <=Led<<1;

end

endmodule

仿真代码

`timescale 1ns / 1ns

module led_run_tb();

reg Clk;

reg Reset_n;

wire [7:0]Led;//位宽八位

led_run led_run(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led)

);

initial Clk = 1;

always #10 Clk = ~Clk;

initial begin

Reset_n = 0;

#201;

Reset_n = 1;

//#4000_000_000;32位有符号数不能表示已经超过最大值,换另一种表达方式

//#2000_000_000;

//#2000_000_000;

#40_000_000;//缩短时间,提高仿真效率

$stop;

end

endmodule

管脚文件

set_property PACKAGE_PIN Y18 [get_ports Clk]

set_property IOSTANDARD LVCMOS33 [get_ports Clk]

set_property PACKAGE_PIN B21 [get_ports Reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports Reset_n]

set_property PACKAGE_PIN M22 [get_ports Led[0]]

set_property PACKAGE_PIN N22 [get_ports Led[1]]

set_property PACKAGE_PIN L21 [get_ports Led[2]]

set_property PACKAGE_PIN K21 [get_ports Led[3]]

set_property PACKAGE_PIN K22 [get_ports Led[4]]

set_property PACKAGE_PIN J22 [get_ports Led[5]]

set_property PACKAGE_PIN H22 [get_ports Led[6]]

set_property PACKAGE_PIN M21 [get_ports Led[7]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[0]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[1]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[2]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[3]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[4]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[5]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[6]]

set_property IOSTANDARD LVCMOS33 [get_ports Led[7]]