目录

[1. Pin Swapping 导出法](#1. Pin Swapping 导出法)

[2. 网表导出法](#2. 网表导出法)

[3. 专用工具法](#3. 专用工具法)

1. Pin Swapping 导出法

这个方法适合快速查看和初步整理引脚信息。

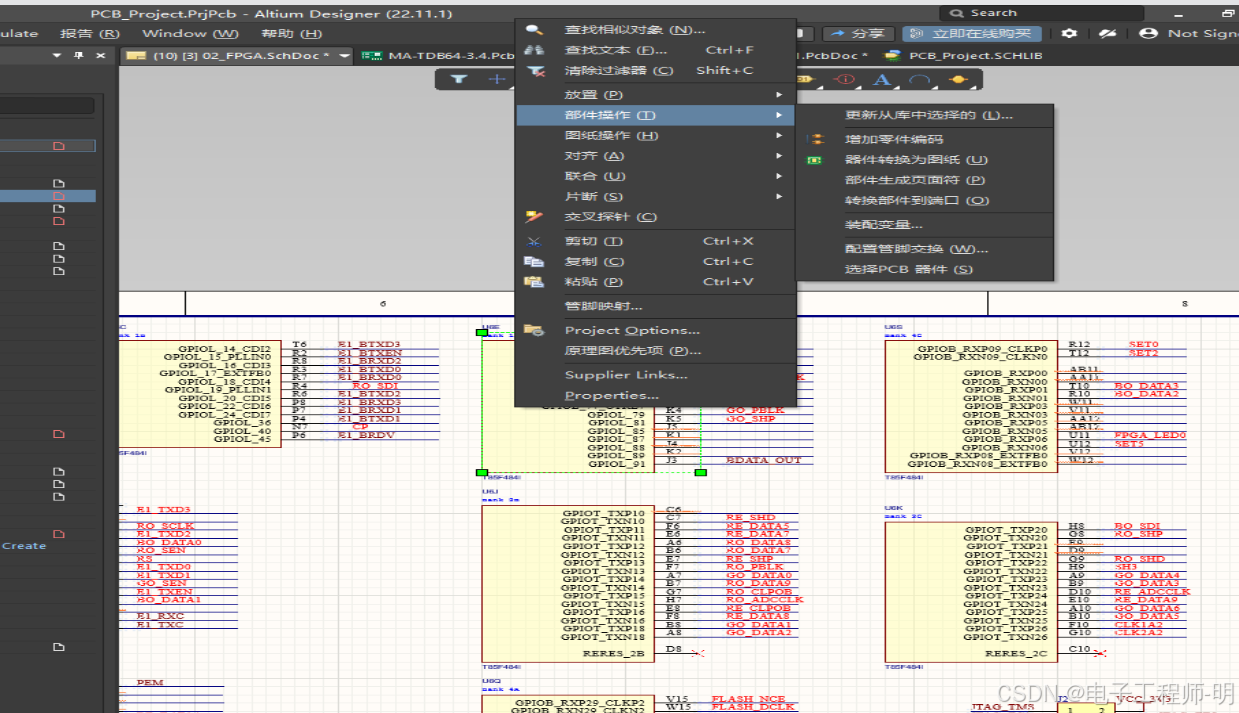

打开界面

:在原理图中,右键点击FPGA器件的其中一个Part,选择 Part Actions -> Configure Pin Swapping。

复制数据

:在打开的 "Pin Swapping" 页面,按 Ctrl+A 全选所有引脚信息,然后按 Ctrl+C 复制。

粘贴处理

:将复制的内容粘贴到Excel中。你可以在Excel里删除不必要的列,并使用筛选功能过滤掉VCC、GND等电源相关引脚,简化后续工作。

2. 网表导出法

如果你需要将引脚信息用于FPGA开发工具(如Quartus, Vivado)中的引脚约束,这个方法提供了基础数据。

导出网表

:在AD中,点击菜单栏的 Design -> Netlist for Project -> Protel。也可以尝试导出为 Verilog File 或 VHDL File,它们都能包含引脚和网络的对应关系。

处理网表

:导出的网表文件是结构化的文本文件。你可以使用文本编辑器(如Notepad++)或脚本工具(如Python)来解析这个文件,提取出FPGA引脚和网络名的对应关系,并转换成FPGA工具所需的格式(如Xilinx的XDC或Altera的QSF/TCL)。

3. 专用工具法

这是最快捷的方式,可以自动完成网表解析和整理。

获取工具

:有开发者分享了专门用于此任务的小工具,例如搜索结果中提到的 dec_net 工具。你可以从提供的网盘链接或其他开源平台查找此类工具。

运行工具

:这类工具通常需要一个输入文件(AD导出的Protel网表文件)和FPGA元件的位号(如U1)。运行后,它能自动生成一个整洁的引脚-网络对应列表文本文件。有些工具还支持对结果进行排序,让列表更清晰。

操作建议与注意事项

选择合适的方法

:根据你的需求选择。如果只是简单查看,用Pin Swapping法;如果需要导入FPGA工具,网表导出法或专用工具法更高效。

核对与筛选

:无论用哪种方法,导出的引脚列表都可能包含电源、接地等非用户I/O引脚。在生成最终的FPGA引脚约束文件前,务必仔细核对并筛选出需要分配的I/O引脚。

PCB布局考虑

:有时为了PCB布线的便利,原理图中的信号可能不会直接连接到FPGA芯片最容易布线的引脚上。因此,导出的引脚分配可能需要根据PCB的实际布局进行调整。

希望这些方法能帮助你高效地完成FPGA管脚导出工作。如果你能告诉我你使用的具体是哪个系列的FPGA(例如Xilinx的Zynq,或者Altera的Cyclone),或许我可以提供更有针对性的格式转换建议。