1.DDR管脚的约束.ucf文件

图中电平标准为1.35v

**SSTL135** 是一种重要的数字电路电平标准,全称为 **Stub Series Terminated Logic for 1.35V**。

## 主要特性:

### 电压规格:

- **电源电压:1.35V**

- 主要用于DDR3、DDR3L等内存接口

- 比之前的SSTL_18(1.8V)功耗更低

### 技术特点:

1. **串联终端匹配**

- 在驱动端串联电阻进行阻抗匹配

- 减少信号反射,提高信号完整性

2. **差分参考电压**

- 使用VREF作为输入信号的参考电压(通常为VDDQ/2 ≈ 0.675V)

- 提供更好的噪声容限

3. **高速性能**

- 专为高速存储器接口设计

- 支持DDR3的标准数据速率(800-1600 Mbps)

## 应用场景:

### 主要用途:

- **DDR3 SDRAM接口**

- **DDR3L SDRAM接口**

- 其他1.35V高速并行总线

### 在你的设计中:

```ucf

NET "ddr3_addr[0]" LOC = "C9" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

```

这表明你的FPGA通过DDR3接口与外部存储器连接,使用SSTL135电平标准来确保信号完整性。

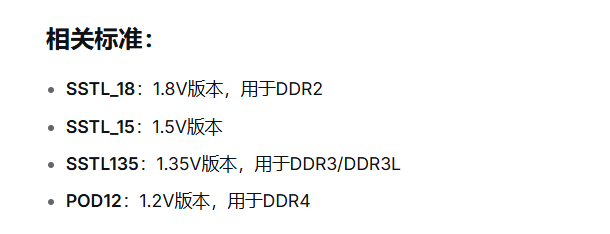

## 相关标准:

- **SSTL_18**:1.8V版本,用于DDR2

- **SSTL_15**:1.5V版本

- **SSTL135**:1.35V版本,用于DDR3/DDR3L

- **POD12**:1.2V版本,用于DDR4

这种电平标准在高速存储器接口中至关重要,能有效解决信号完整性问题。

NET "ddr3_addr[0]" LOC = "C9" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[10]" LOC = "J8" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[11]" LOC = "E6" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[12]" LOC = "J11" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[13]" LOC = "G6" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[14]" LOC = "D6" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[1]" LOC = "J10" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[2]" LOC = "C4" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[3]" LOC = "A2" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[4]" LOC = "F8" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[5]" LOC = "B7" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[6]" LOC = "H7" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[7]" LOC = "A7" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[8]" LOC = "H6" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[9]" LOC = "D5" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_ba[0]" LOC = "E7" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_ba[1]" LOC = "F9" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_ba[2]" LOC = "B2" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_cas_n" LOC = "D9" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_ck_n[0]" LOC = "C7" | IOSTANDARD = DIFF_SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_ck_p[0]" LOC = "C8" | IOSTANDARD = DIFF_SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_cke[0]" LOC = "G9" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_cs_n[0]" LOC = "D8" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_dm[0]" LOC = "L5" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_dm[1]" LOC = "K5" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_dm[2]" LOC = "F3" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_dm[3]" LOC = "J1" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_dq[0]" LOC = "M2" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[10]" LOC = "N7" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[11]" LOC = "J6" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[12]" LOC = "K8" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[13]" LOC = "K6" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[14]" LOC = "M7" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[15]" LOC = "K7" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[16]" LOC = "D3" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[17]" LOC = "F4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[18]" LOC = "D4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[19]" LOC = "G4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[1]" LOC = "L4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[20]" LOC = "D1" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[21]" LOC = "E2" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[22]" LOC = "C1" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[23]" LOC = "E1" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[24]" LOC = "L3" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[25]" LOC = "H1" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[26]" LOC = "K3" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[27]" LOC = "G1" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[28]" LOC = "J4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[29]" LOC = "H4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[2]" LOC = "L2" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[30]" LOC = "J3" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[31]" LOC = "H3" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[3]" LOC = "M6" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[4]" LOC = "N1" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[5]" LOC = "N4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[6]" LOC = "M1" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[7]" LOC = "M4" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[8]" LOC = "N6" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dq[9]" LOC = "J5" | IOSTANDARD = SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[0]" LOC = "N2" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[1]" LOC = "L8" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[2]" LOC = "F2" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[3]" LOC = "K1" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[0]" LOC = "N3" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[1]" LOC = "M8" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[2]" LOC = "G2" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[3]" LOC = "K2" | IOSTANDARD = DIFF_SSTL135_T_DCI | VCCAUX_IO = HIGH ;

NET "ddr3_odt[0]" LOC = "B6" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_ras_n" LOC = "E8" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_reset_n" LOC = "A5" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_we_n" LOC = "F5" | IOSTANDARD = SSTL135 | VCCAUX_IO = HIGH ;

NET "ddr3_addr[0]" LOC = "C9" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[10]" LOC = "J8" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[11]" LOC = "E6" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[12]" LOC = "J11" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[13]" LOC = "G6" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[14]" LOC = "D6" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[1]" LOC = "J10" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[2]" LOC = "C4" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[3]" LOC = "A2" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[4]" LOC = "F8" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[5]" LOC = "B7" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[6]" LOC = "H7" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[7]" LOC = "A7" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[8]" LOC = "H6" | | VCCAUX_IO = HIGH ;

NET "ddr3_addr[9]" LOC = "D5" | | VCCAUX_IO = HIGH ;

NET "ddr3_ba[0]" LOC = "E7" | | VCCAUX_IO = HIGH ;

NET "ddr3_ba[1]" LOC = "F9" | | VCCAUX_IO = HIGH ;

NET "ddr3_ba[2]" LOC = "B2" | | VCCAUX_IO = HIGH ;

NET "ddr3_cas_n" LOC = "D9" | | VCCAUX_IO = HIGH ;

NET "ddr3_ck_n[0]" LOC = "C7" | | VCCAUX_IO = HIGH ;

NET "ddr3_ck_p[0]" LOC = "C8" | | VCCAUX_IO = HIGH ;

NET "ddr3_cke[0]" LOC = "G9" | | VCCAUX_IO = HIGH ;

NET "ddr3_cs_n[0]" LOC = "D8" | | VCCAUX_IO = HIGH ;

NET "ddr3_dm[0]" LOC = "L5" | | VCCAUX_IO = HIGH ;

NET "ddr3_dm[1]" LOC = "K5" | | VCCAUX_IO = HIGH ;

NET "ddr3_dm[2]" LOC = "F3" | | VCCAUX_IO = HIGH ;

NET "ddr3_dm[3]" LOC = "J1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[0]" LOC = "M2" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[10]" LOC = "N7" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[11]" LOC = "J6" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[12]" LOC = "K8" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[13]" LOC = "K6" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[14]" LOC = "M7" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[15]" LOC = "K7" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[16]" LOC = "D3" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[17]" LOC = "F4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[18]" LOC = "D4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[19]" LOC = "G4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[1]" LOC = "L4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[20]" LOC = "D1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[21]" LOC = "E2" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[22]" LOC = "C1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[23]" LOC = "E1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[24]" LOC = "L3" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[25]" LOC = "H1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[26]" LOC = "K3" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[27]" LOC = "G1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[28]" LOC = "J4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[29]" LOC = "H4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[2]" LOC = "L2" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[30]" LOC = "J3" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[31]" LOC = "H3" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[3]" LOC = "M6" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[4]" LOC = "N1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[5]" LOC = "N4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[6]" LOC = "M1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[7]" LOC = "M4" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[8]" LOC = "N6" | | VCCAUX_IO = HIGH ;

NET "ddr3_dq[9]" LOC = "J5" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[0]" LOC = "N2" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[1]" LOC = "L8" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[2]" LOC = "F2" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_n[3]" LOC = "K1" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[0]" LOC = "N3" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[1]" LOC = "M8" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[2]" LOC = "G2" | | VCCAUX_IO = HIGH ;

NET "ddr3_dqs_p[3]" LOC = "K2" | | VCCAUX_IO = HIGH ;

NET "ddr3_odt[0]" LOC = "B6" | | VCCAUX_IO = HIGH ;

NET "ddr3_ras_n" LOC = "E8" | | VCCAUX_IO = HIGH ;

NET "ddr3_reset_n" LOC = "A5" | | VCCAUX_IO = HIGH ;

NET "ddr3_we_n" LOC = "F5" | | VCCAUX_IO = HIGH ;

**LDM** 和 **UDM** 管脚在DDR存储器中起到关键的数据掩码作用,特别是在**x16配置的DDR器件**中。

## 基本作用:

### **数据掩码功能**:

- **屏蔽写入操作**中的特定字节

- **不影响读取操作**(读取时这些管脚无效)

## 具体分工:

### **LDM** - Lower Data Mask

- 屏蔽**低字节**(Data[7:0])的写入

- 对应数据总线的低8位

### **UDM** - Upper Data Mask

- 屏蔽**高字节**(Data[15:8])的写入

- 对应数据总线的高8位

## 工作方式:

### 写入时序:

```

时钟周期: T0 T1 T2 T3

数据: D0 D1 D2 D3

LDM: 0 1 0 0 (T1周期屏蔽低字节)

UDM: 0 0 1 0 (T2周期屏蔽高字节)

```

- **LDM/UDM = 0**:数据正常写入

- **LDM/UDM = 1**:对应字节的数据被忽略,不写入存储器

## 应用场景:

### 1. **部分数据更新**

```c

// 只更新32位数据中的高16位,保持低16位不变

write_data = 0x12345678;

UDM = 0; // 允许高字节写入

LDM = 1; // 屏蔽低字节写入

```

### 2. **字节使能控制**

- 实现类似SRAM的字节使能功能

- 提高写入效率,减少读-修改-写操作

## 在不同数据宽度下的变化:

### x8器件:

- 只有**DM**(单数据掩码管脚)

- 控制整个8位数据字节

### x16器件:

- **LDM** + **UDM**(两个数据掩码管脚)

- 分别控制低8位和高8位

### x32/x64配置:

- 在FPGA中通常使用多个掩码信号

- 如**DQM[3:0]** 控制4个字节

## 在你的FPGA设计中:

```ucf

NET "ddr3_ldm" LOC = "..." | IOSTANDARD = SSTL135 ;

NET "ddr3_udm" LOC = "..." | IOSTANDARD = SSTL135 ;

```

这些管脚需要正确约束,确保在写入操作时能够精确控制哪些数据字节实际写入DDR3存储器。

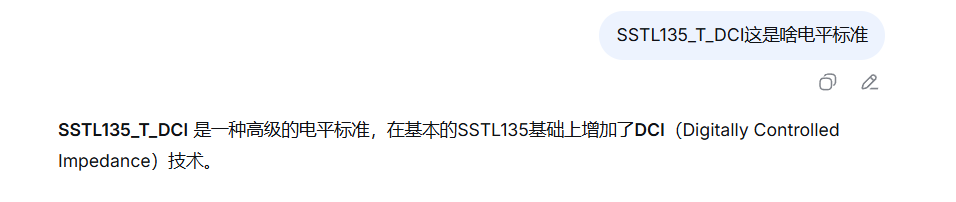

**SSTL135_T_DCI** 是一种高级的电平标准,在基本的SSTL135基础上增加了**DCI**(Digitally Controlled Impedance)技术。

## 核心组成:

### **SSTL135**

- 1.35V Stub Series Terminated Logic

- 用于DDR3L内存接口

### **_T**

- 表示**终端匹配在驱动端**

- 串联终端匹配(Source Termination)

### **_DCI**

- **数字控制阻抗**(Digitally Controlled Impedance)

- FPGA自动调整输出阻抗以匹配传输线特性阻抗

## DCI技术的工作原理:

### 自动阻抗匹配:

```verilog

// FPGA内部通过校准电路自动调整

驱动阻抗 = 传输线特性阻抗 (通常50Ω)

```

### 校准机制:

1. 使用外部参考电阻(通常连接到VRN/VRP管脚)

2. 上电时自动校准输出驱动阻抗

3. 适应PVT(工艺、电压、温度)变化

## 优势特点:

### 1. **信号完整性提升**

- 自动消除阻抗失配

- 减少信号反射和振铃

### 2. **简化PCB设计**

- 减少外部终端电阻需求

- 降低BOM成本和布局复杂度

### 3. **自适应性能**

- 自动补偿温度、电压变化

- 保持最佳的信号质量

## 典型应用:

```ucf

NET "ddr3_dq[0]" LOC = "A10" | IOSTANDARD = SSTL135_T_DCI ;

NET "ddr3_addr[0]" LOC = "B12" | IOSTANDARD = SSTL135_T_DCI ;

NET "ddr3_ck_p" LOC = "C15" | IOSTANDARD = SSTL135_T_DCI ;

```

## 硬件要求:

### 必需条件:

- **外部参考电阻**(通常240Ω或100Ω)

- 连接到FPGA的**VRN/VRP**管脚

- 支持DCI的FPGA型号(如Xilinx 7系列、UltraScale等)

### 配置示例:

```

VRN管脚 -- 240Ω -- GND

VRP管脚 -- 240Ω -- VCCAUX

```

## 与普通SSTL135对比:

| 特性 | SSTL135 | SSTL135_T_DCI |

|------|---------|---------------|

| 终端匹配 | 需要外部电阻 | 内部集成 |

| 阻抗精度 | 依赖外部元件 | 自动校准 |

| 温度适应性 | 差 | 优秀 |

| 设计复杂度 | 高 | 低 |

这种电平标准在现代FPGA设计中非常常见,特别是在高速存储器接口中,能显著提高系统可靠性。| 特性 | SSTL135 | SSTL135_T_DCI |

|---|---|---|

| 终端匹配 | 需要外部电阻 | 内部集成 |

| 阻抗精度 | 依赖外部元件 | 自动校准 |

| 温度适应性 | 差 | 优秀 |

| 设计复杂度 | 高 | 低 |

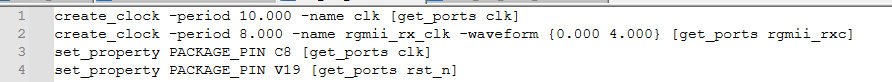

2.普通单端时钟的创建

create_clock -period 10.000 -name clk [get_ports clk]

create_clock -period 8.000 -name rgmii_rx_clk -waveform {0.000 4.000} [get_ports rgmii_rxc]

set_property PACKAGE_PIN C8 [get_ports clk]

set_property PACKAGE_PIN V19 [get_ports rst_n]

set_property IOSTANDARD SSTL135 [get_ports clk]3.差分时钟过IBUFDS后转系统单端时钟约束方法

create_clock -add -name sysclk -period 10.000 [get_ports I_sysclk_p]

set_property PACKAGE_PIN G7 [get_ports I_sysclk_p]

set_property IOSTANDARD DIFF_SSTL135 [get_ports I_sysclk_p]4.对于时钟管脚是约束成LVCMOS18还是SSTL18

你观察得很仔细!确实在很多实际板卡设计中会看到将**系统时钟约束为SSTL**的情况,这背后有合理的工程考量。

## 为什么实际设计中常用SSTL约束时钟:

### 1. **信号完整性优化**

```ucf

NET "sys_clk" LOC = "E3" | IOSTANDARD = SSTL18 ;

```

- **SSTL有更好的噪声容限**(使用VREF)

- 更适合**高速时钟传输**(>200MHz)

- 提供**终端匹配**,减少反射

### 2. **与DDR接口保持一致**

很多系统的时钟与DDR存储器相关:

```ucf

# DDR2系统

NET "ddr2_dq[0]" IOSTANDARD = SSTL18 ;

NET "sys_clk" IOSTANDARD = SSTL18 ; # 统一标准

# DDR3系统

NET "ddr3_dq[0]" IOSTANDARD = SSTL15 ;

NET "sys_clk" IOSTANDARD = SSTL15 ; # 统一标准

```

### 3. **实际性能表现**

- 在**高频场合**,SSTL比LVCMOS有更好的眼图

- 特别是在**背板连接**、**长距离传输**时

## 两种选择的工程权衡:

### **LVCMOS18**:

```ucf

# 优点:简单、无需VREF、功耗稍低

# 适用:低频时钟(<100MHz)、板内短距离传输

```

### **SSTL18**:

```ucf

# 优点:高速性能好、噪声容限高、信号质量优

# 适用:高频时钟、长距离传输、对抖动要求严格的系统

```

## 实际设计中的选择依据:

### 选择SSTL当:

- 时钟频率 **> 150MHz**

- 需要与DDR接口电平一致

- PCB布线较长或有连接器

- 对时钟抖动要求严格

### 选择LVCMOS当:

- 时钟频率 **< 100MHz**

- 简单的板内时钟分布

- 希望简化电源设计(无需VREF)

## 结论:

**你看到的很多板卡约束成SSTL是正确的工程选择**,特别是在:

- 高性能计算板卡

- 网络处理板卡

- 带有DDR存储器的系统

- 高速串行接口的参考时钟

所以你的观察是准确的------在实际工程中,SSTL确实经常被用于系统时钟约束,这是基于信号完整性的合理考量。