面向模块的综合技术之控制集优化(七)

文章目录

- 面向模块的综合技术之控制集优化(七)

- 前言

- 控制集优化

-

- [1. 什么是控制集(Control Set)](#1. 什么是控制集(Control Set))

- [2. 控制集分析](#2. 控制集分析)

- [4. 优化四板斧](#4. 优化四板斧)

-

- [4.1 合并复位 ------ 最大收益](#4.1 合并复位 —— 最大收益)

- [4.2 合并 CE ------ 无 CE 就造"常有效"CE](#4.2 合并 CE —— 无 CE 就造“常有效”CE)

- [4.3 消灭"集合只有 1 个 FF"的孤岛](#4.3 消灭“集合只有 1 个 FF”的孤岛)

- [4.4 用 `SEQUENTIAL_LATE_CELL` + `set_case_analysis` 告诉工具"常有效"](#4.4 用

SEQUENTIAL_LATE_CELL+set_case_analysis告诉工具“常有效”)

- [5. 控制集与 retiming 的联动](#5. 控制集与 retiming 的联动)

前言

控制集优化

1. 什么是控制集(Control Set)

Xilinx FPGA 里 一个触发器 的控制信号由 4 张票决定:

| 票名 | 可选值 | 说明 |

|---|---|---|

| CLK | 任意时钟 net | 时钟域 |

| CE | 任意使能 net / 1'b1 | 高/低有效均可 |

| SR | 任意复位/置位 net / 1'b0 | 高/低有效 + 同步/异步 |

| SR 类型 | {SYNC, ASYNC} | 由 always 敏感列表决定 |

只要 任意一张不同 ,就是 不同控制集。

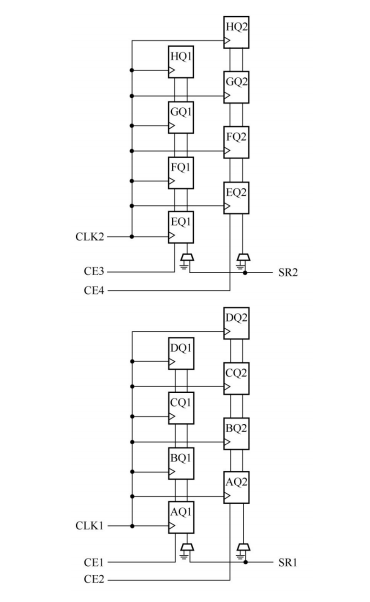

对于7系列FPGA,每个SLICE中有8个触发器,这8个触发器共享时钟端口、时钟使能端口和置位/复位端口,因此,这8个触发器只有1个控制集

对于UltraScale系列FPGA,每个SLICE包含16个触发器。这16个触发器分为两组:对于上半部分的8个共享时钟端口和置位/复

位端口,每4个端口共享1个使能端口,所以有两组控制集;下半部分的8

个触发器亦是如此。

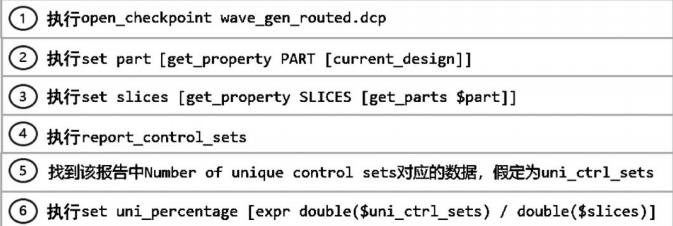

2. 控制集分析

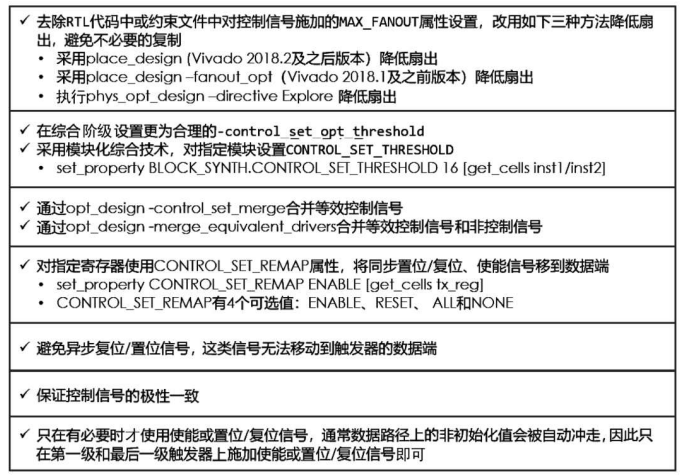

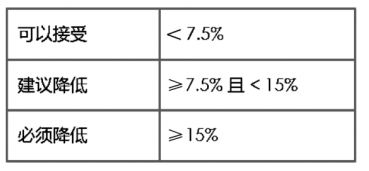

Xilinx给出了控制集百分比指导值

tcl

# 一键报表

report_control_sets -verbose -file ctrl.rpt

# 看数量

llength [lsort -unique [get_cells -hier -filter {PRIMITIVE_TYPE =~ FD*.*}]]经验红线:

- 7-Series ≤ 8 个 / UltraScale ≤ 16 个

- 超过即开始优化,别等 place 失败再回头。

4. 优化四板斧

4.1 合并复位 ------ 最大收益

verilog

// 优化前:五花八门

always @(posedge clk or negedge rst_a) ...

always @(posedge clk or posedge rst_b) ...

// 优化后:统一低电平复位

always @(posedge clk or negedge rst_n)

if (!rst_n) ...- 高电平复位 → 加反相器宏:

verilog

assign rst_n = ~rst_p; /* synthesis keep */- 异步复位 → 如非必要,改 同步释放;可省 SR 类型差异。

4.2 合并 CE ------ 无 CE 就造"常有效"CE

verilog

wire ce_global = 1'b1; // 常有效

(* keep *)

reg a /* CE = ce_global */;

always @(posedge clk)

if (ce_global) a <= d;- 不要直接写

always @(posedge clk) a <= d;

工具会生成CE=1'b1但线名不同 → 仍算独立控制集!

4.3 消灭"集合只有 1 个 FF"的孤岛

tcl

# 找出孤岛

report_control_sets -verbose -hierarchy | grep "Count.*1 "- 孤岛常来自 IP 或手写代码;wrapper 一层,把它的 CE/RST 接到 全局同名牌。

4.4 用 SEQUENTIAL_LATE_CELL + set_case_analysis 告诉工具"常有效"

tcl

set_property SEQUENTIAL_LATE_CELL TRUE [get_cells a]

set_case_analysis 1 [get_pins a/ce_global]防止工具把 1'b1 优化回独立线,导致控制集再次分裂。

5. 控制集与 retiming 的联动

verilog

// 优化前:不同控制集 → retiming 0 移动

// 优化后:同控制集 → 报告

Retiming moved 12 registers across 37 logic levels

WNS +0.38 ns同控制集 = 同滑轨 → 寄存器可在 SLICE 内 横向滑 、纵向滑,retiming/folding/clockEnableOpt 全开。