一,前言

在FPGA - Xilinx系列高速收发器---GTX中详细介绍了GTX的基础知识,以及IP核的调用,下面将补充一下GTX在使用中的高速串行数据流在接收和发送时的控制与对齐**(K码)** ,以及高速接口GTX,如果GTX建链建不起来,Vivado自带的调试工具误码率测试(Integrated Bit Error Ratio Tester,IBERT)核的使用。

二,Comma码(K码)

高速串行数据流在接收端需要重新串并转换成多个字节的并行数据,如何有效的识别32bit数据边界?这就需要一个特殊的序列,即为Comma码(K码) 。在任意数据组合中,Comma码只作为控制字符出现,在数据负荷部分不会出现,所以使用comma码字符只是帧的开始和结束标志,或者修正和数据流对齐的控制字符。

K码是一个集合,D码用来传数据字符,K码用来传控制字符 ,所有和数据本身无关的通道控制功能 都是由K码来完成的。

常见的 K 码为 K28.5,换成十六进制就是 0xBC。

使用 GT 收发器时,K码主要起到两个作用: ①K码对齐(comma alignment) ②)帧对齐(word alignment)

K码对齐(comma alignment)

定义:接收端通过K码,将连续1bit 的数据串行数据分割成有效的字节数据,也就是将有效数据从连续的 0、1中间恢复出来。K 码对齐是 GT IP 核自动完成的。

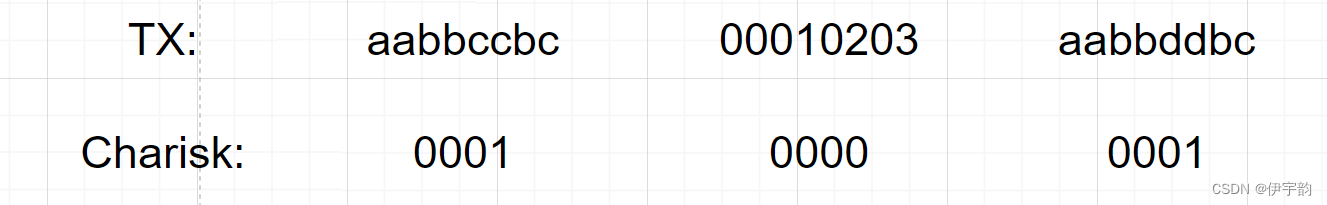

看下面例子(aabbcc可以看作为帧头,bc为K码)

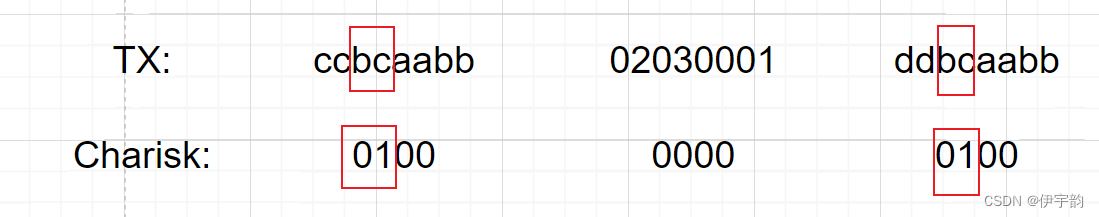

但是在实际传输中可能出现了字节偏移,如下图:

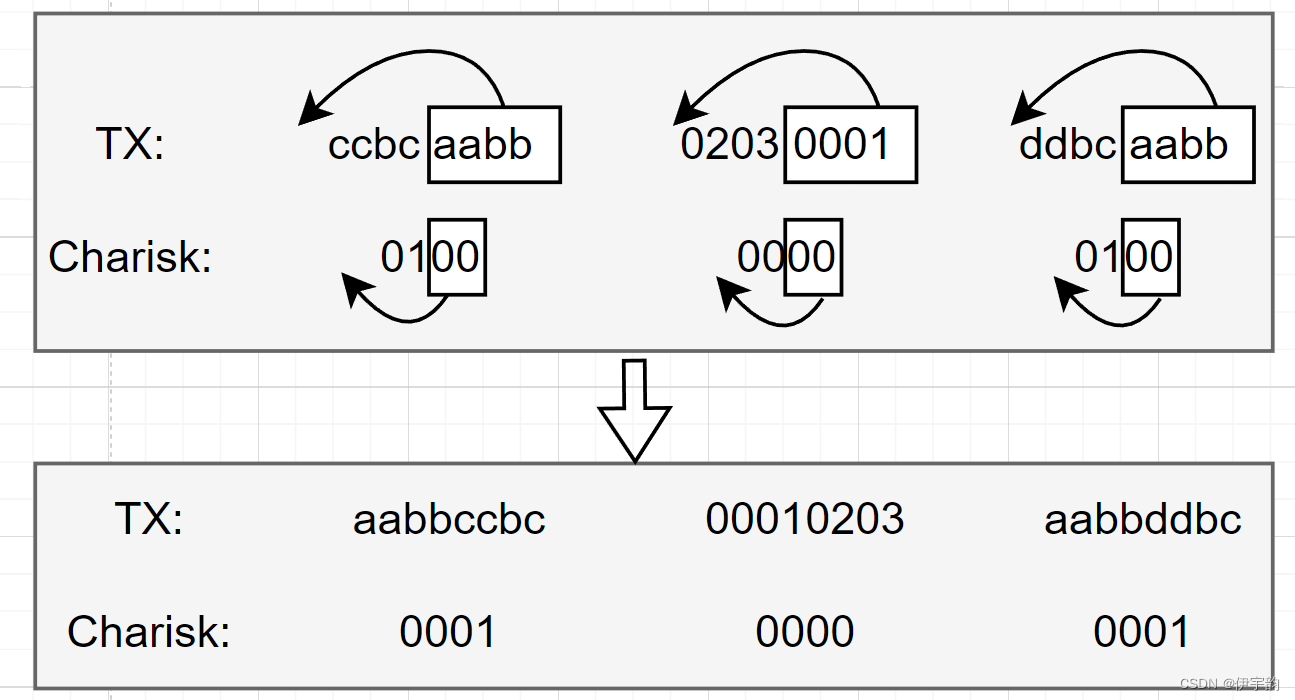

对于用户端就得设计帧对齐,即通过判断charisk的值, 来判断是否发生了字节偏移 ,**如果发生了偏移 就进行移位操作,**如下图:

三,IBERT核

1,概述

IBERT(集成误码率测试仪) 是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器 。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。

IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT可以获取误码率,观察眼图,调节串行收发器的参数,从而有助于判断可能存在的问题,便于验证硬件的稳定性和信号完整性。

2,测试原理

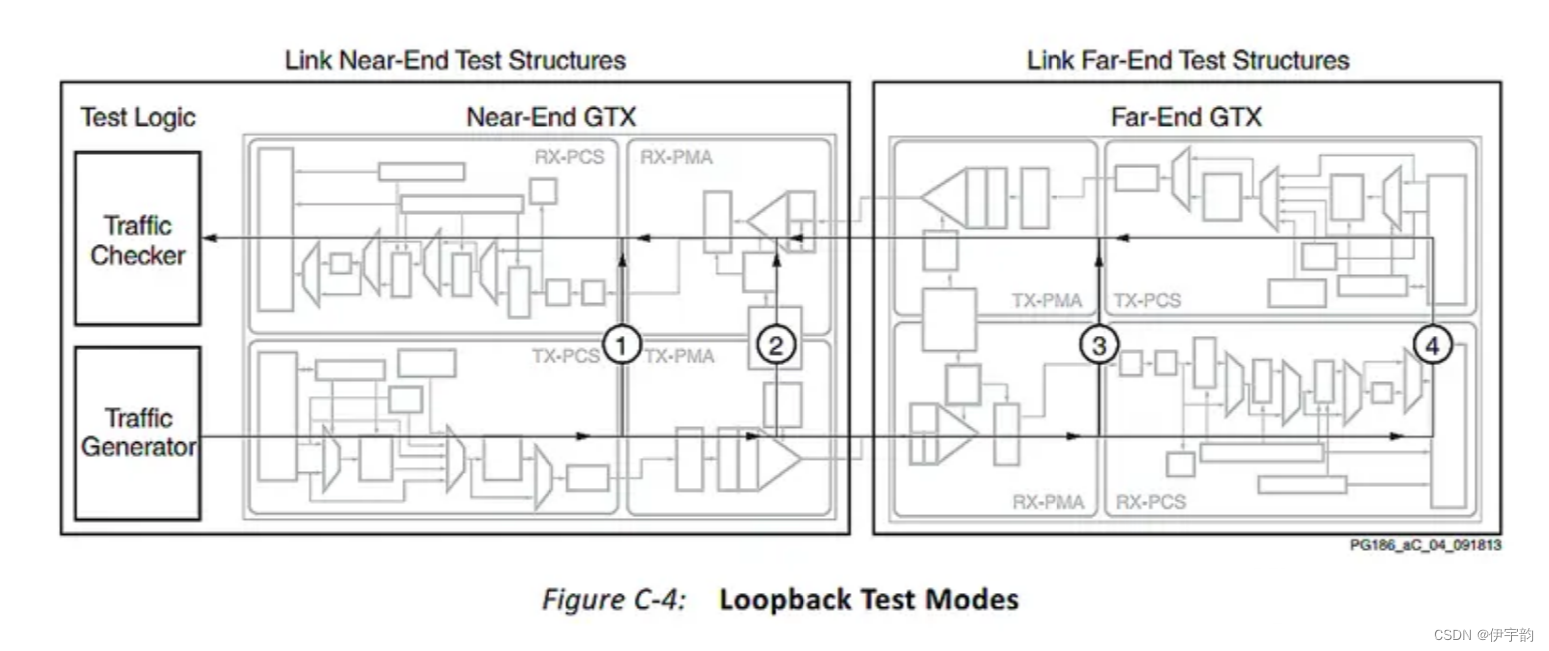

IBERT中的BERT是Bit Error Ratio Test的缩写,指比特出错概率测试 ,简而言之就是误码率 测试。Vivado中IBERT工具的测试原理是通过收发器由外部回环进行自收自发而实现。就是将同一组收发器的TX和RX进行短接,TX发送端通过发送某种特定序列的数据流,在RX接收端接收后,通过比对发送和接收的数据,从而得出接收端误码的统计值。

GTX接收和发送方向均由PMA 和PCS 两部分组成,PCS提供丰富的物理编码层特性 ,如8b10b编码、时钟校准等功能,PMA部分为模拟电路 ,提供高性能的串行接口特性,如预加重、均衡等功能。GTX同时还提供动态配置接口,用于动态的修改GTX的配置。

IBERT 工具的环回模式有:

近端PCS环回测试(路径①),数据流仅通过近端GTX的PCS部分,可用于验证近端GTX中PCS收发双向的设置;

近端PMA环回测试(路径②),数据流通过近端GTX的PCS、PMA,可用于验证近端GTX收发双向的设置;

远端PMA环回测试(路径③),数据流通过近端GTX的PCS和PMA,远端的GTX的PMA部分,通过两个GTX之间的物理连线,验证两个GTX之间物理联系的可靠性,以及验证两个GTX的PMA部分设置的正确性;

**远端PCS环回测试(路径④)**验证近端收发器和远端收发器的通信状况;以及None无环回模式即通过外部连接发送和接收。

远端PCS或PMA环回测试时板卡下载IBERT核生成的bit文件,通过两个通道上的Tx和Rx接口互相连接,其中一个通道上的模式设置为Far_End_PMA 或Far_End_PCS 模式,另一个通道设置为默认的None模式并监测误码率。

Vivado中IBERT默认模式为None模式,收发器通过外部连线由外部环回进行自收自发而实现。可将同一组收发器的TX和RX进行短接,在RX接收端接收TX发送的数据后,通过比对发送和接收的数据,从而得出接收端误码的统计值。

3,IP核配置

(1)创建工程

打开vivado,新建工程后从IP Catalog找到IBERT并双击打开;

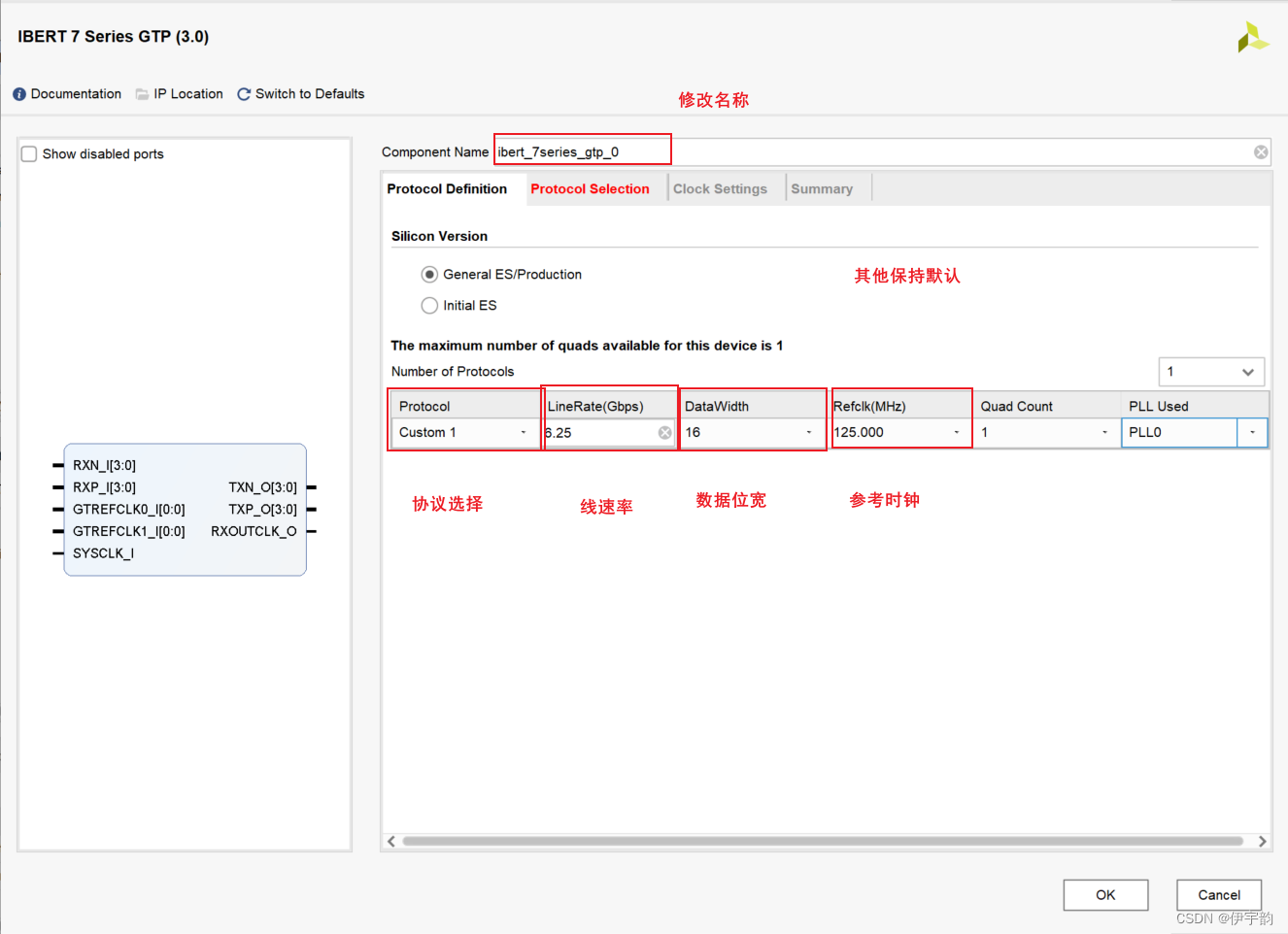

(2)第一页配置

IBERT测试协议选择Custom1,GTX参考时钟选择频率为125MHz,在配置的过程中,Refclk可选的频率是由LineRate决定,由于在板卡上Refclk已固定为125MHz,因此测试所选择的线速应支持125MHz的参考时钟。

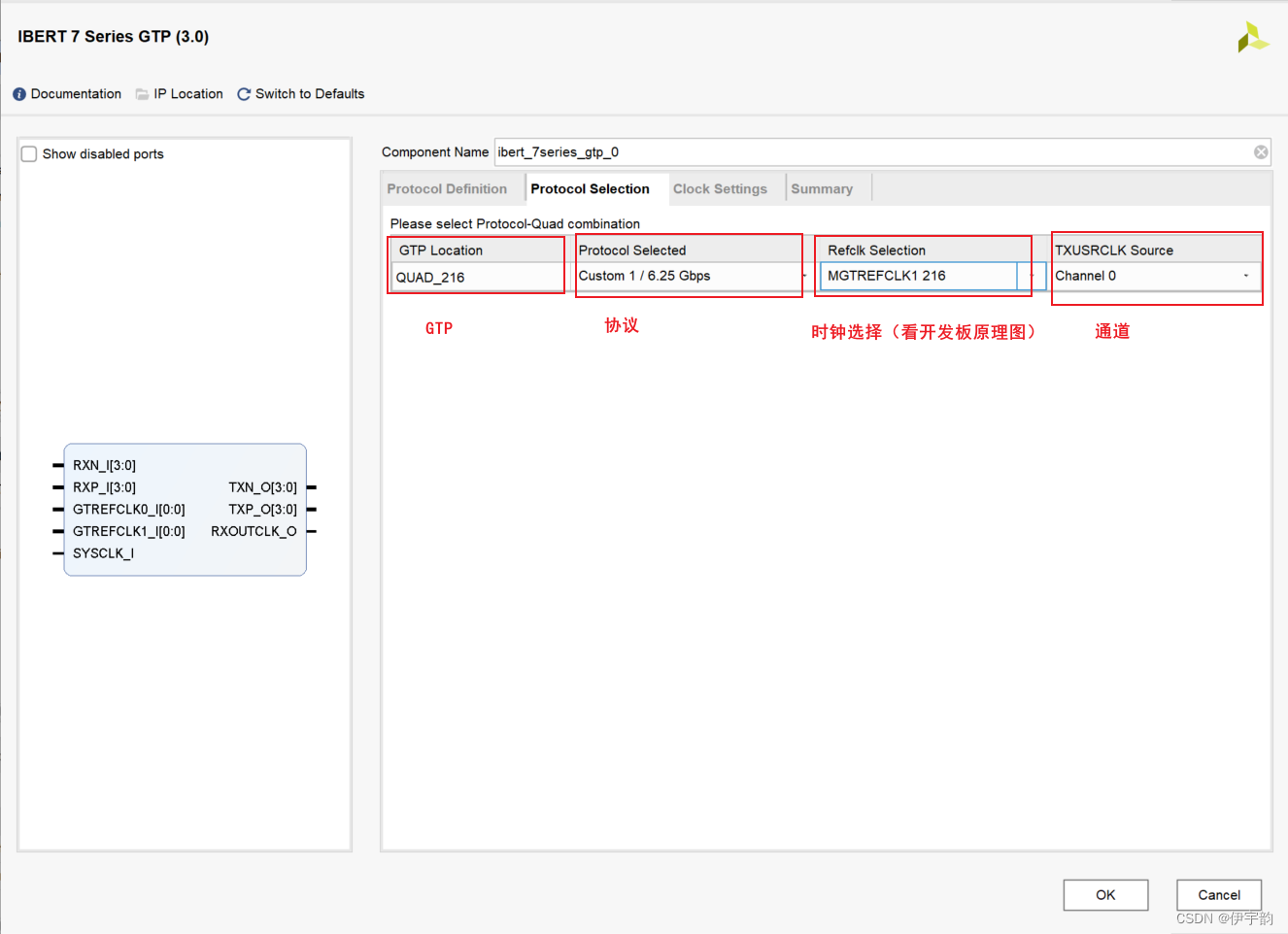

(3) 第二页配置

(4) 第三页配置

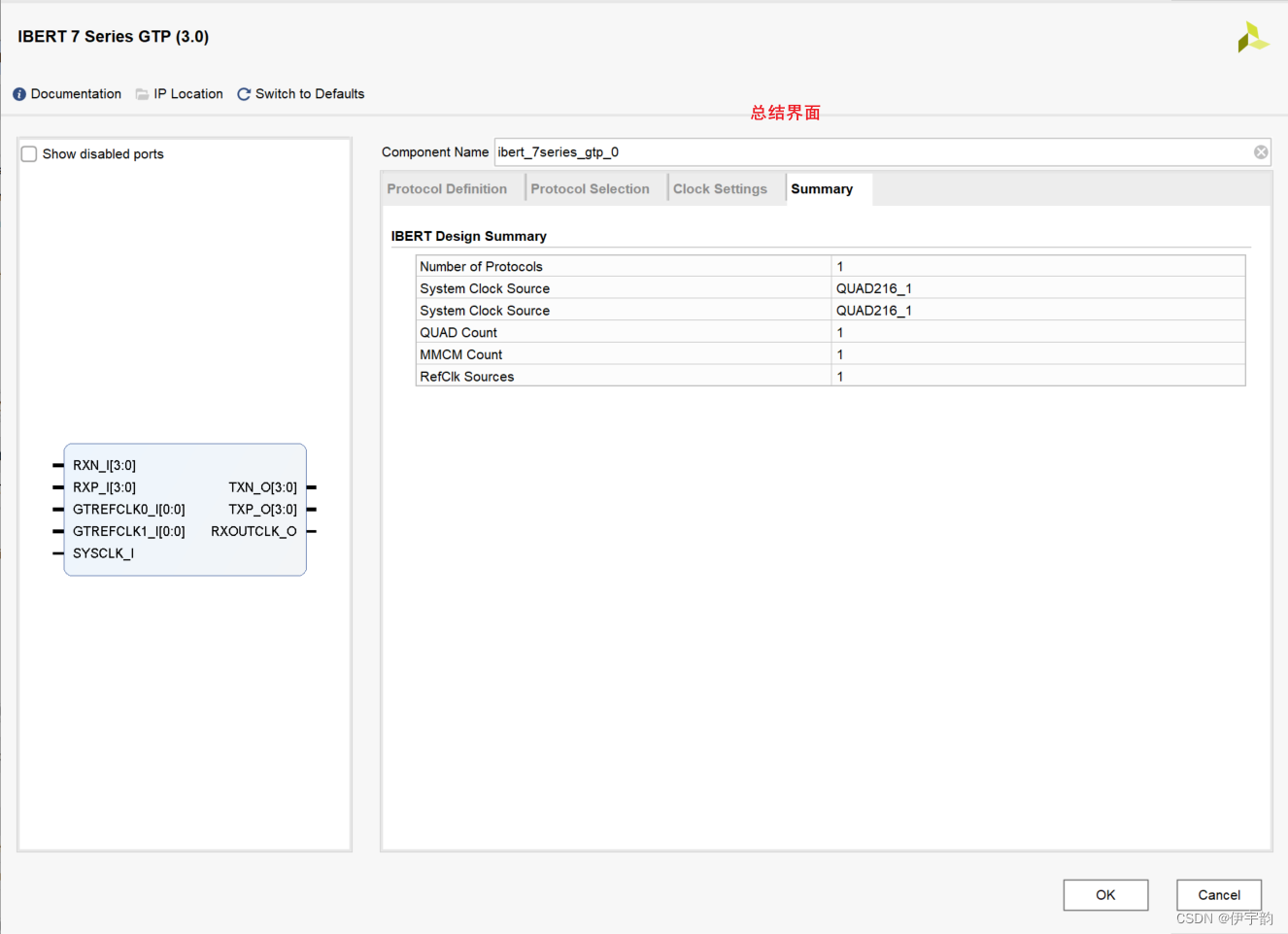

(5)第四页总结

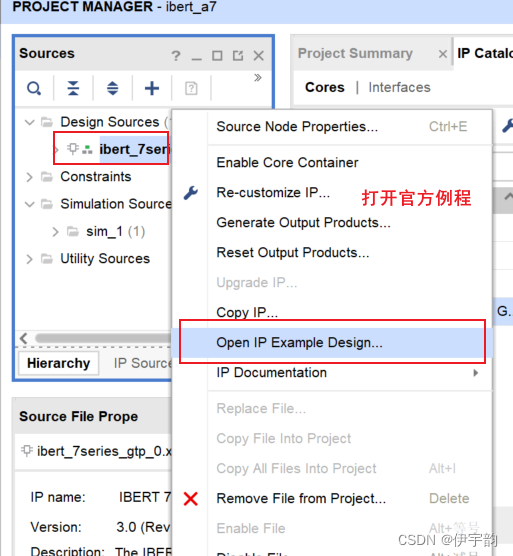

(6)打开例程

创建完成后打开官方例程

(7)生成比特流-烧录

(8)测试

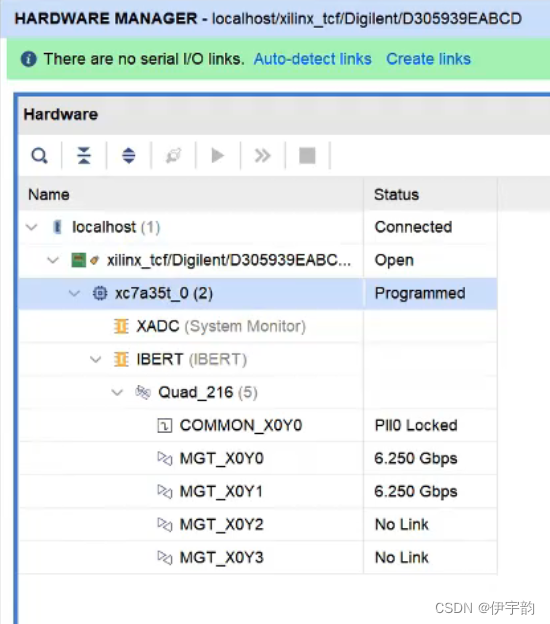

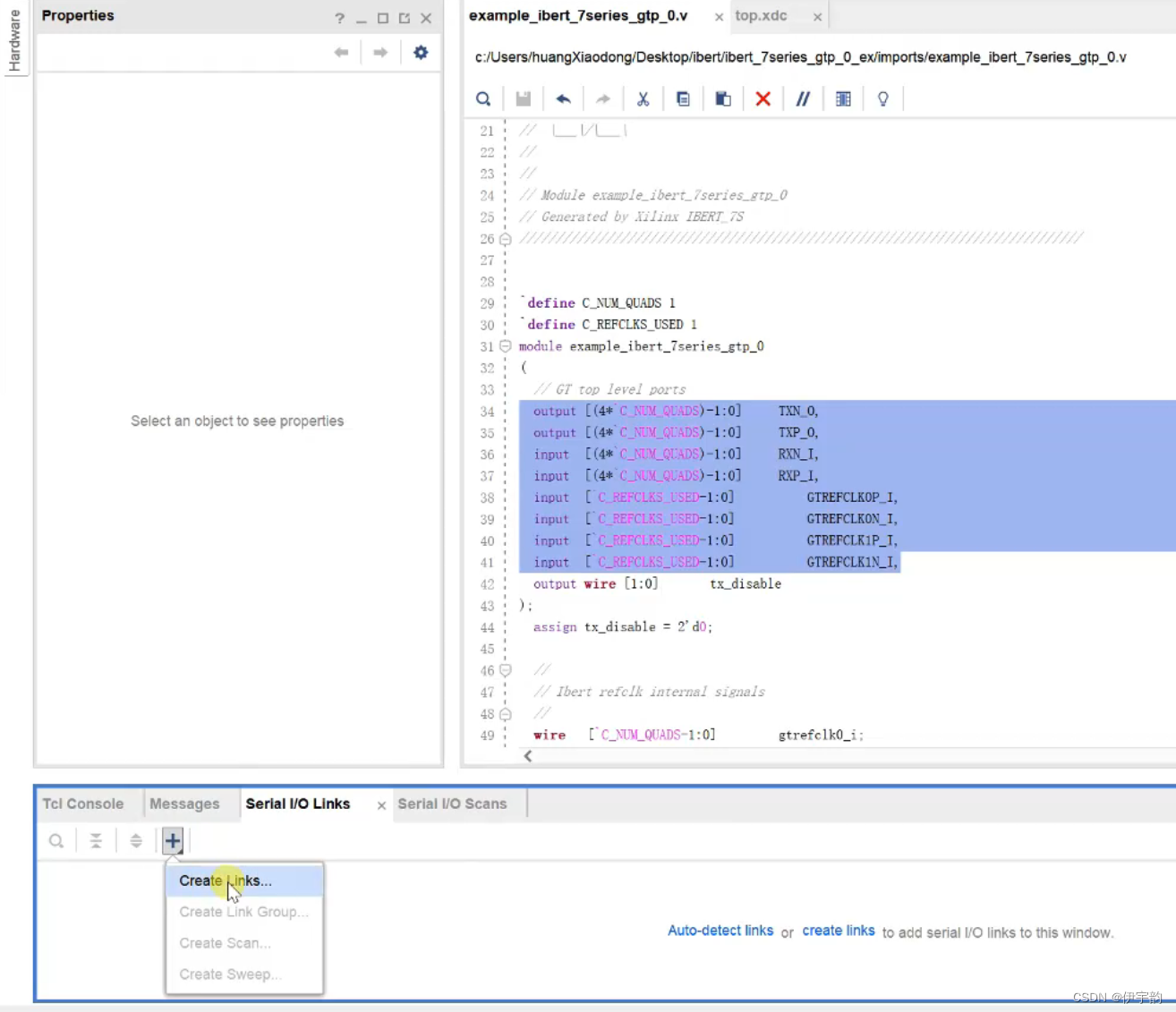

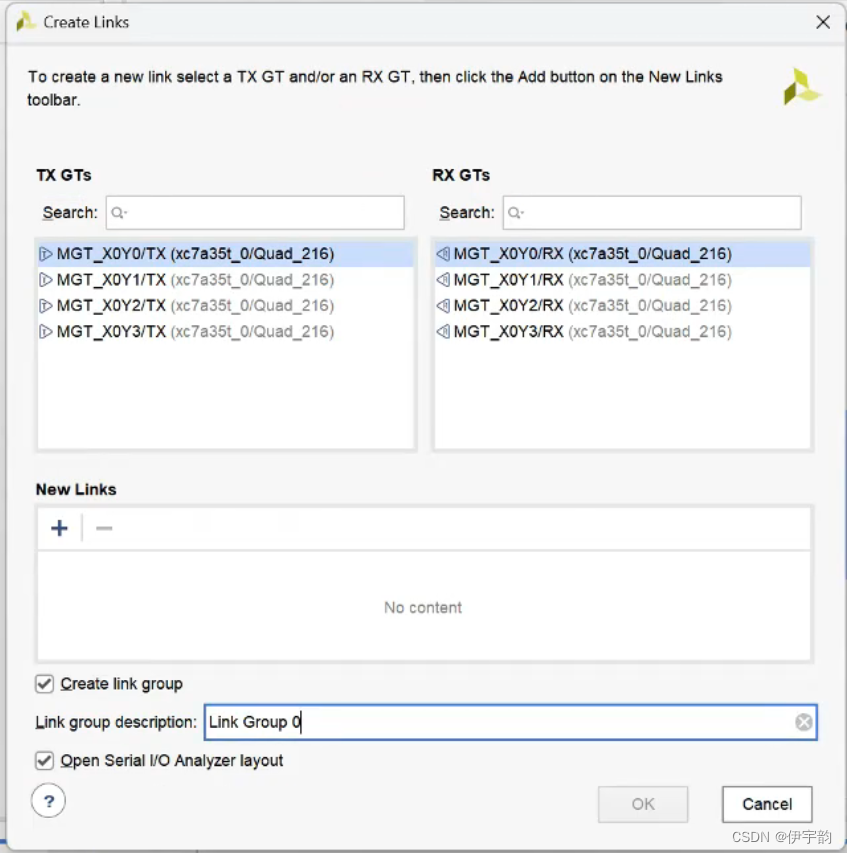

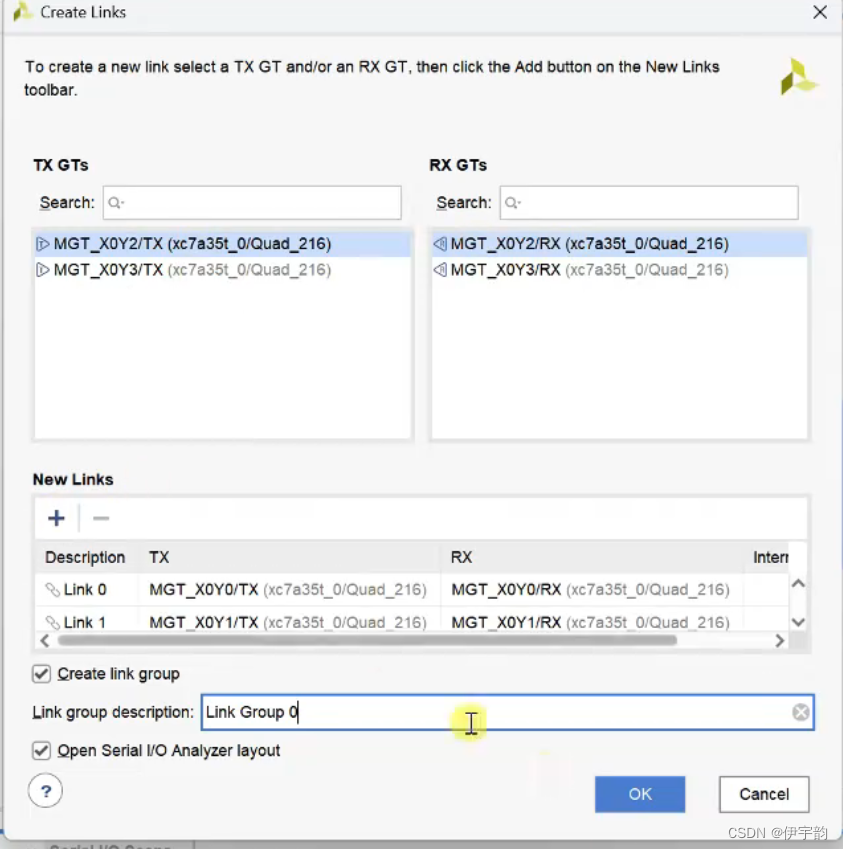

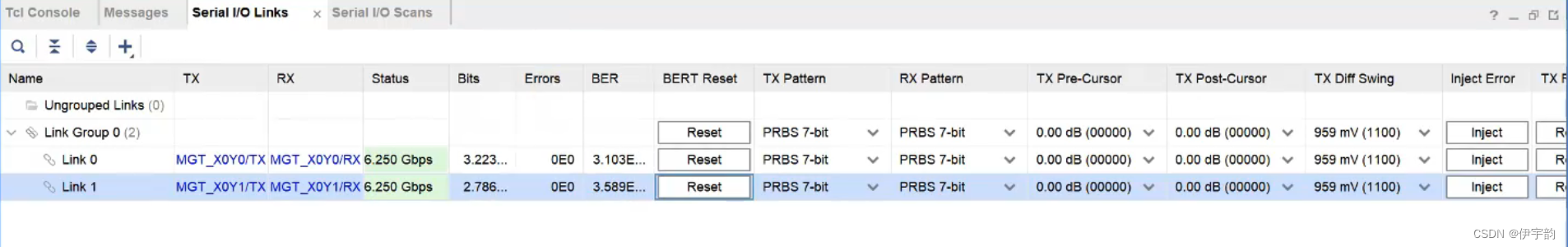

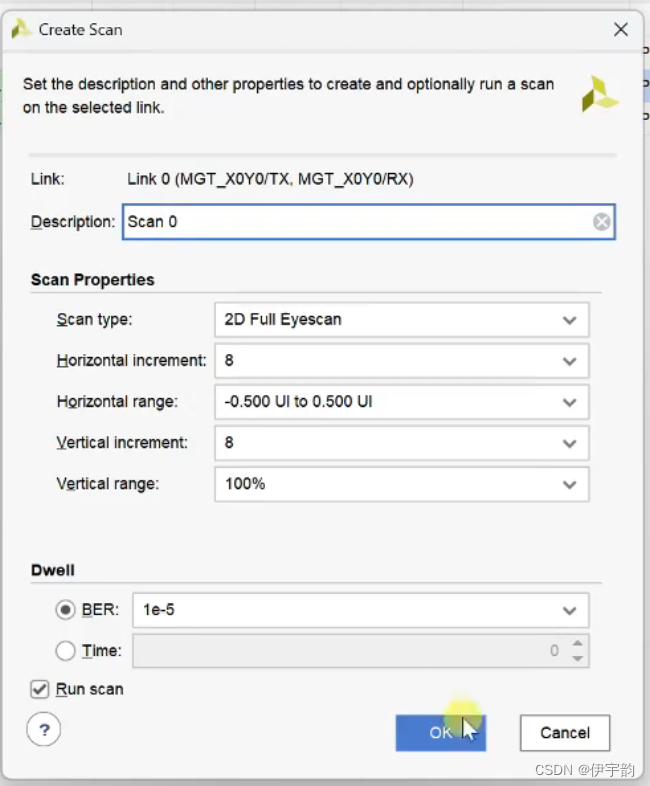

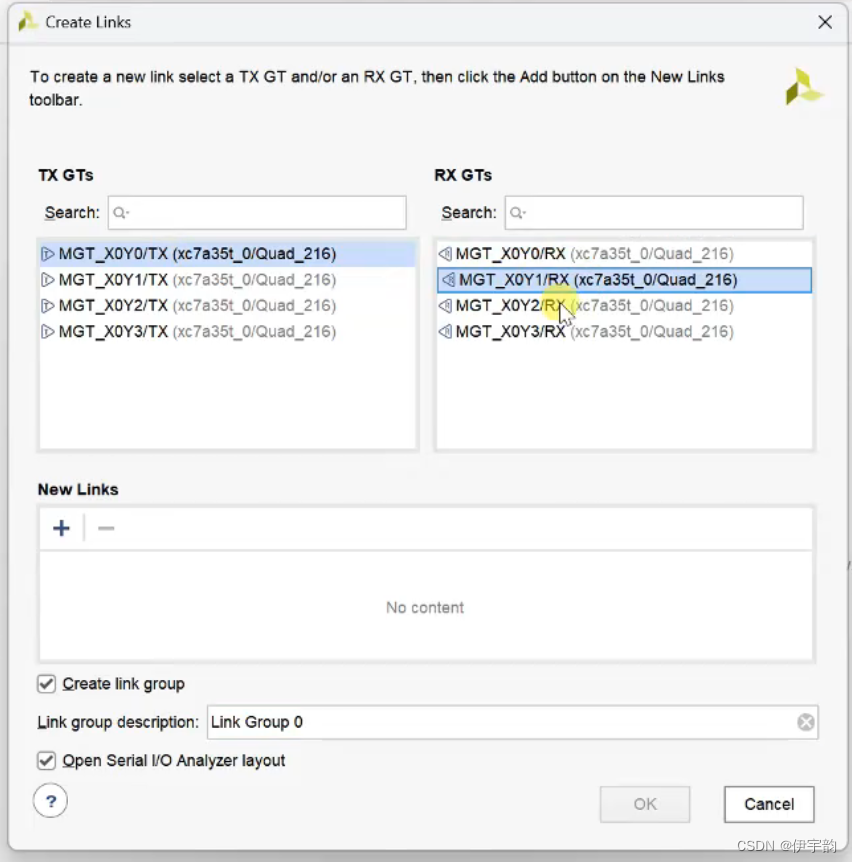

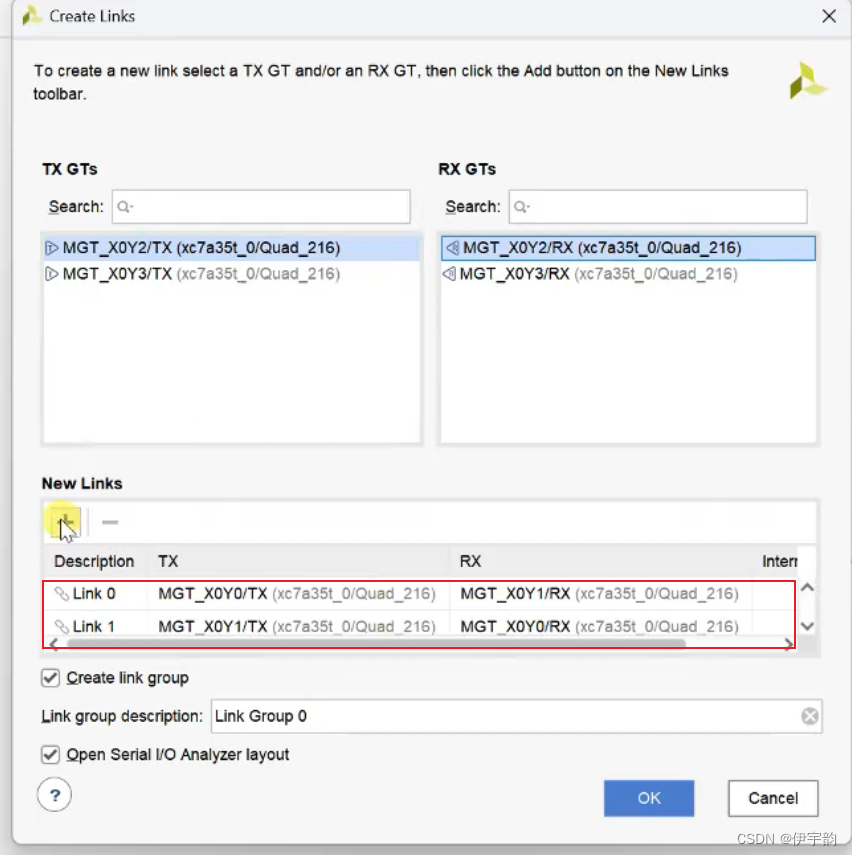

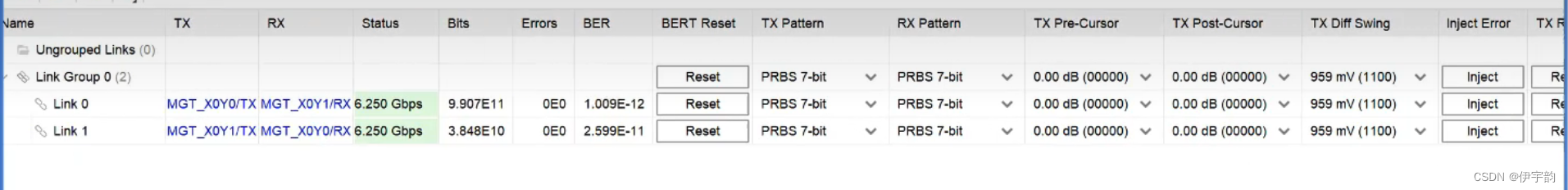

在Serial I/O Links窗口创建连接,将同1个GTX中同一个通道的TX和RX建立link。(也可以选择auto-detectlinks)

进行近端环回

选择 MGT_X0Y0/TX MGT_X0Y0/RX

MGT_X0Y1/TX MGT_X0Y1/RX

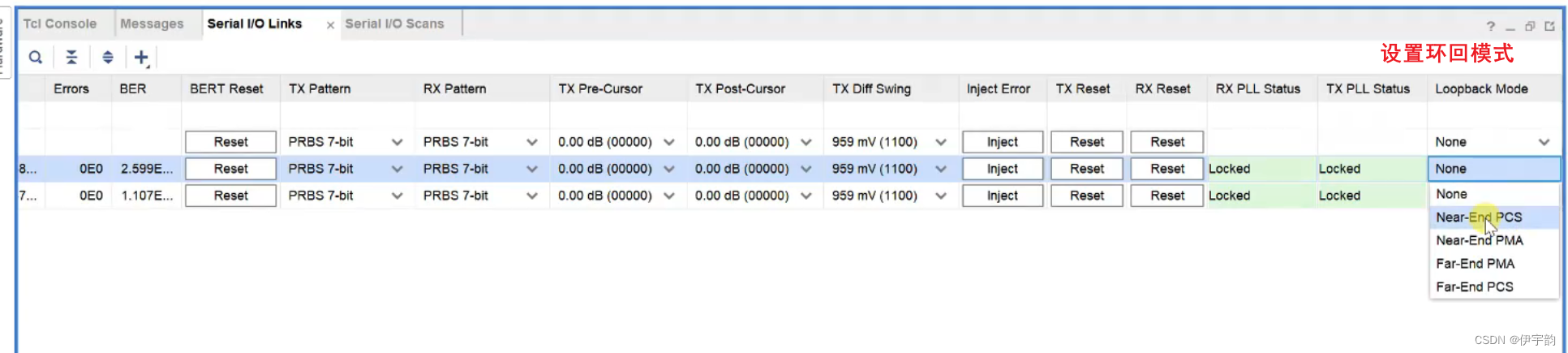

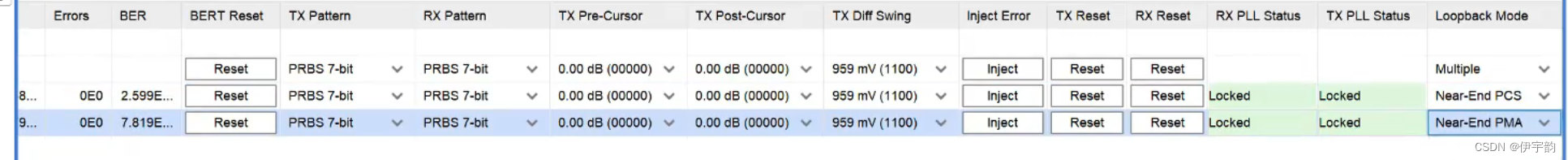

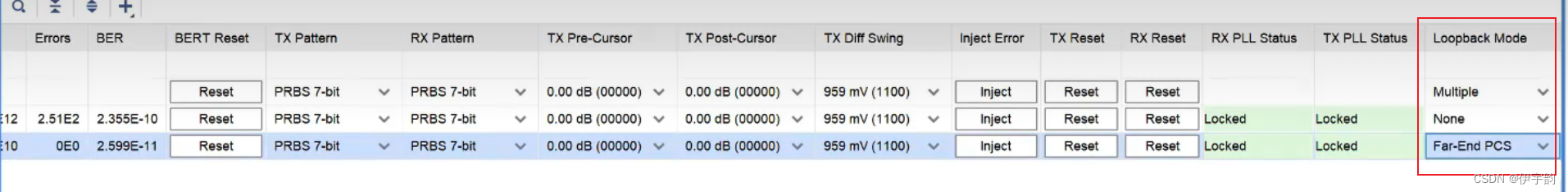

在serial I/O link最右端的loopback mode 选择近端PCS(或PMA)环回模式,在改变模式时可能会出现误码,需要点击reset重新监测。

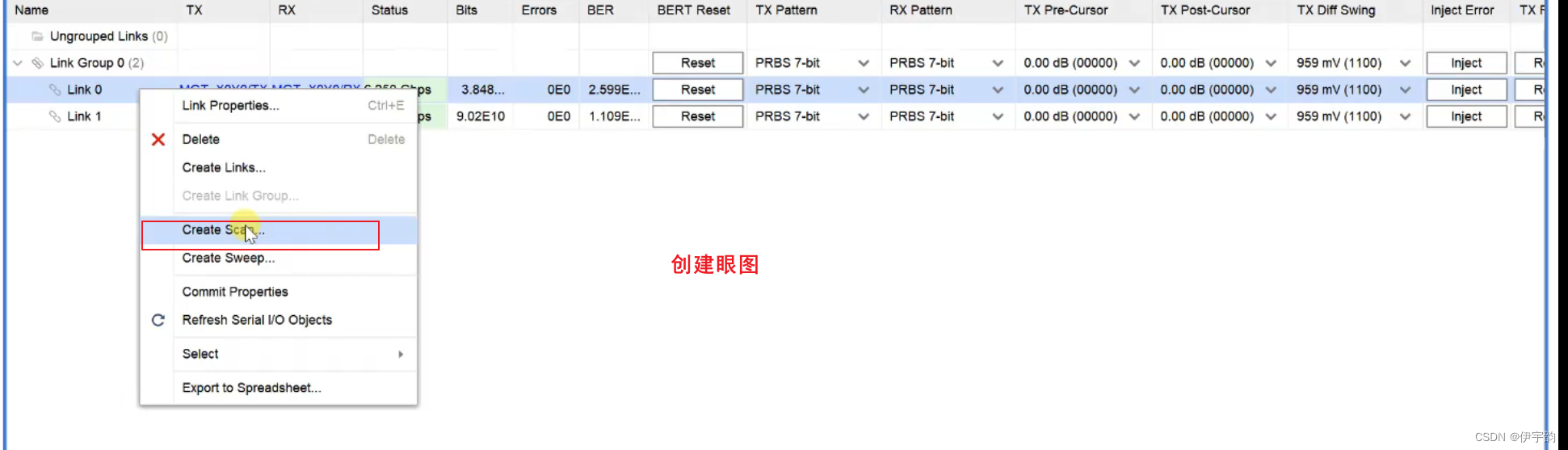

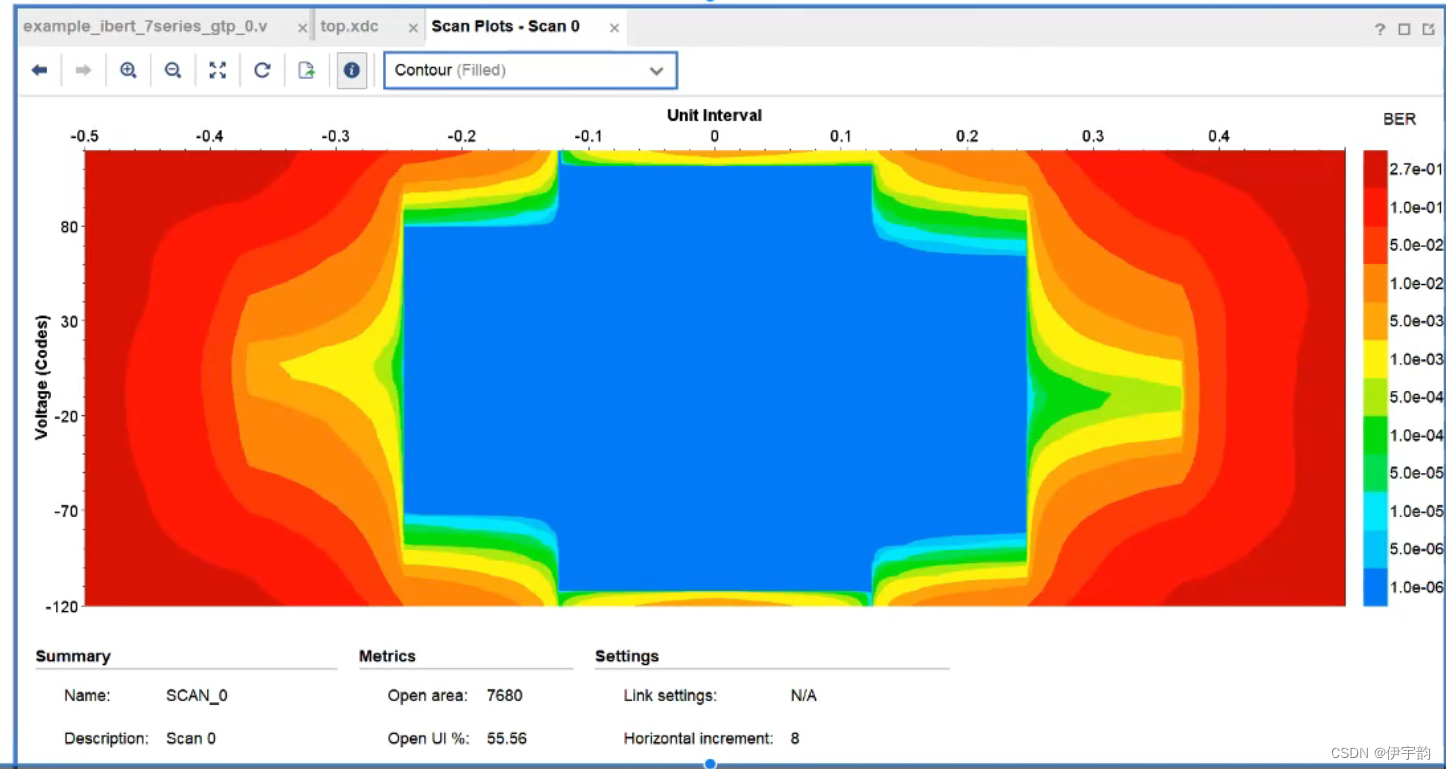

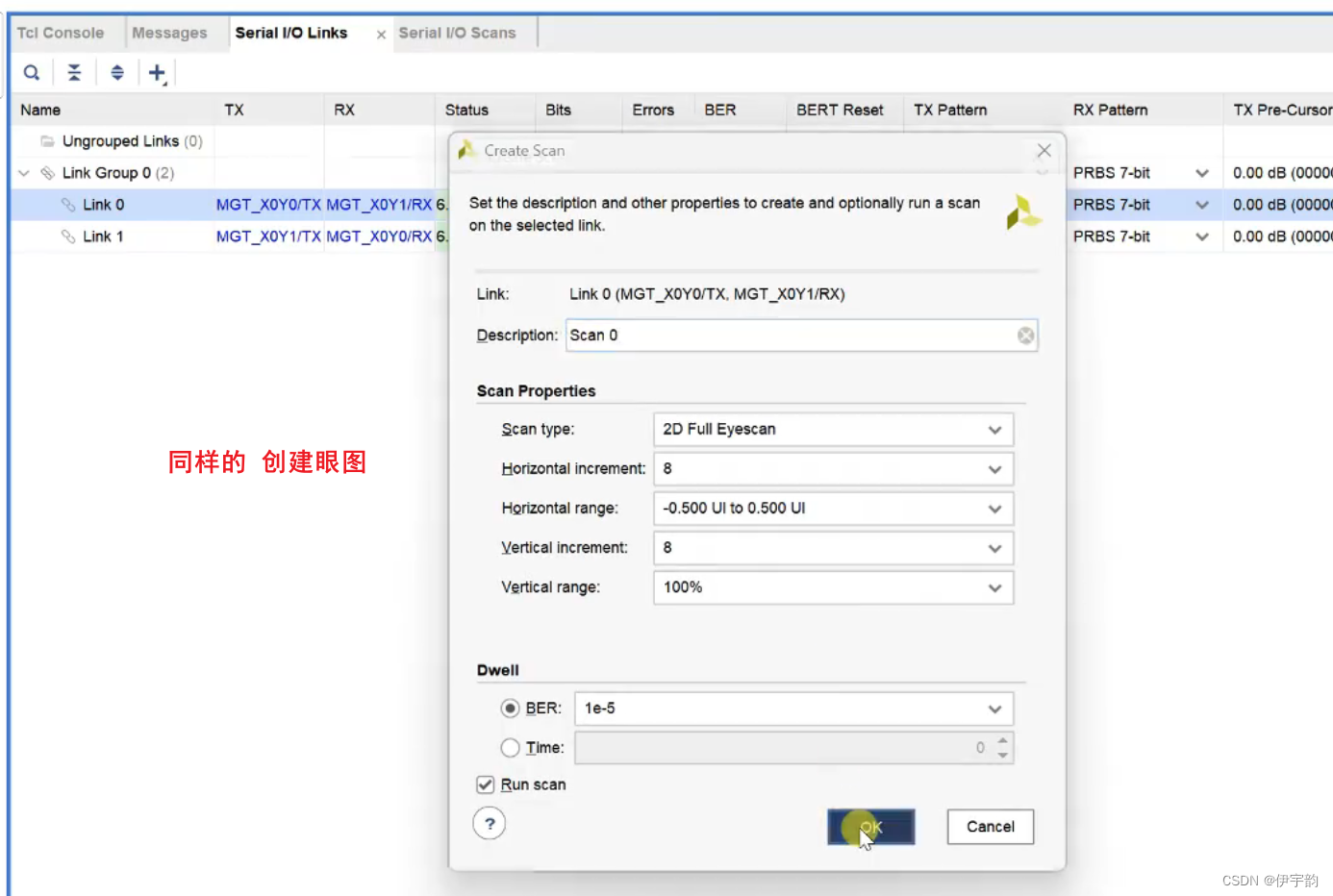

然后创建眼图:

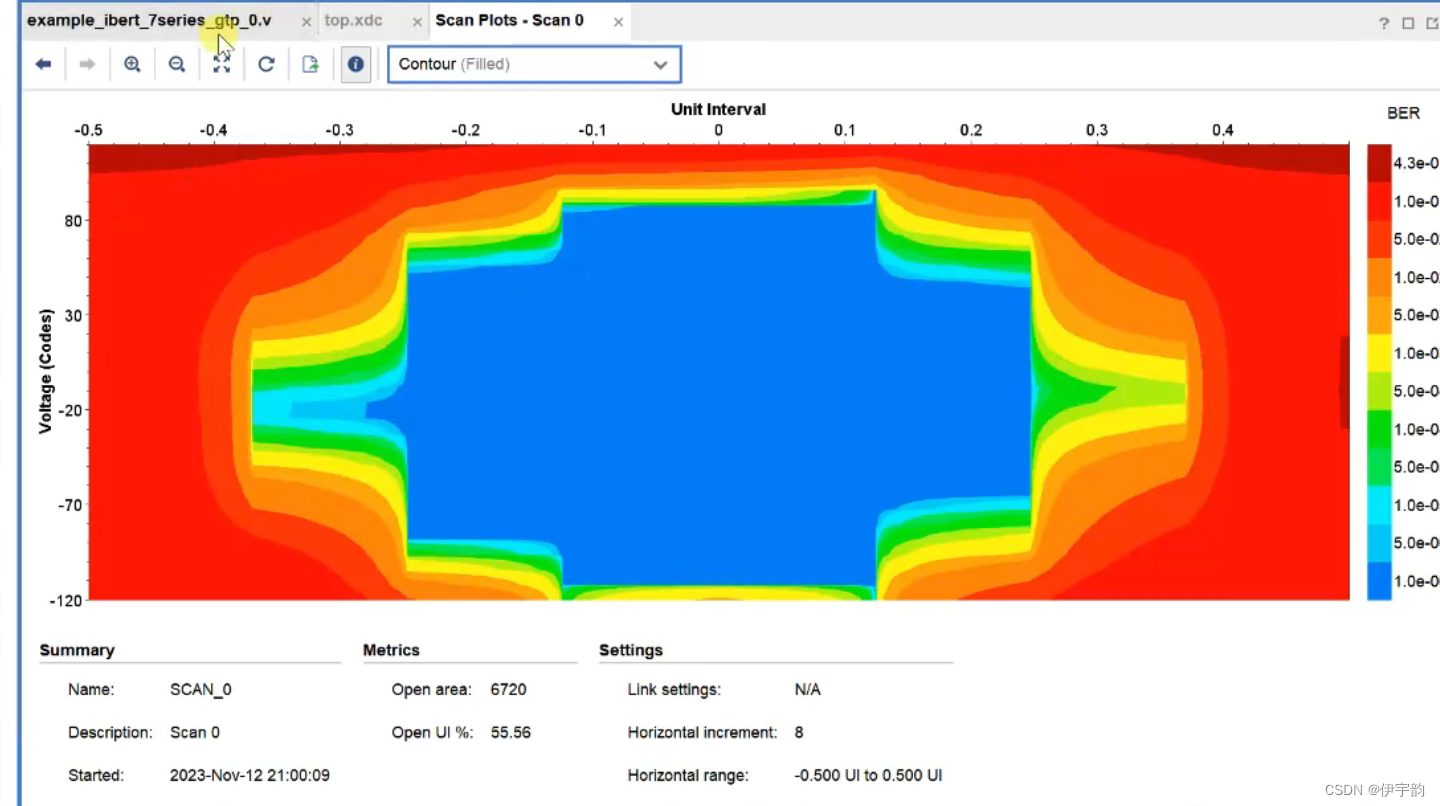

可以看到蓝色表示正常,红色表示误码

远端环回

改变环回模式后记得复位一下

创建眼图

四、总结

通过环回和开环方式进行误码率测试,可以识别问题 并测定板卡的实际支持速率 。IBERT能够在运行时配置高速串行收发通道的各项参数 ,提供多种环回模式和测试激励源,并通过自动扫描测试确定收发的最佳参数 。这能够满足硬件测试 中对高速串行收发通道信号测试 的大部分需求,也适用于故障定位等场合。