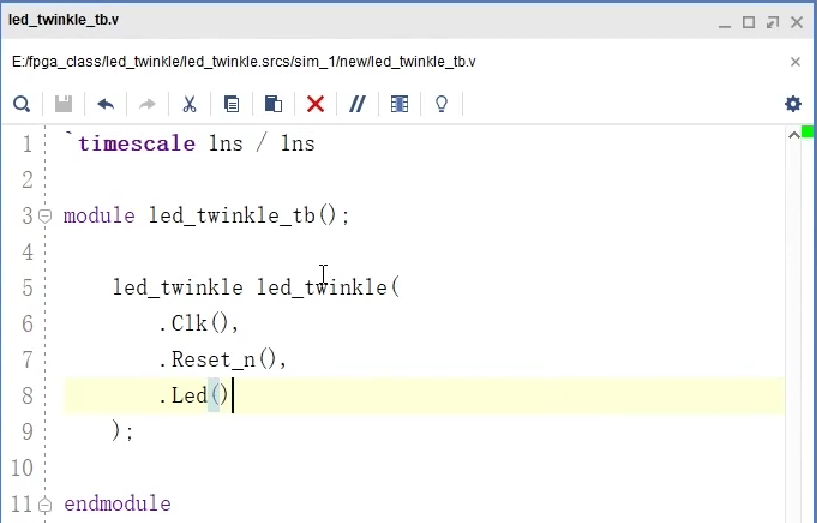

1.新建文件

先新建test bench文件,led_twinkle_tb,将需要仿真的模块添加到test bench中,也就是例化

2.搭建框架

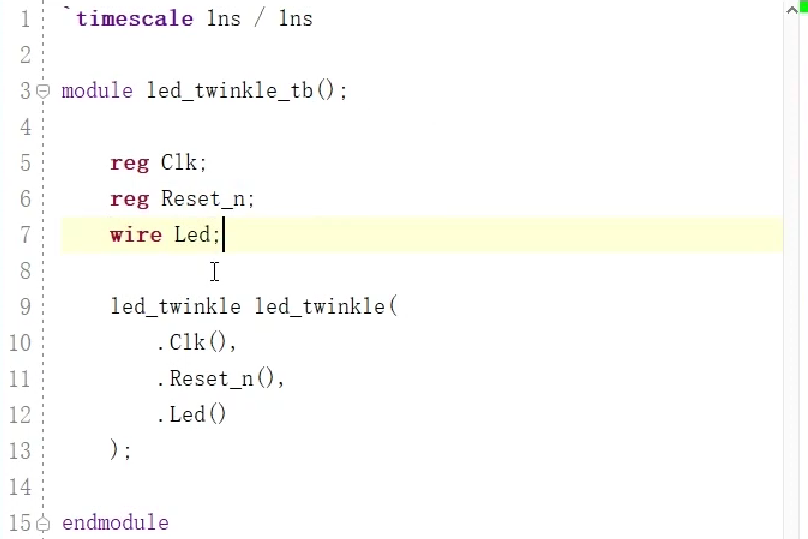

写好基本框架

3.端口定义

在test bench中添加针对输入端口的激励信号的定义以及针对输出端口的观测信号的定义

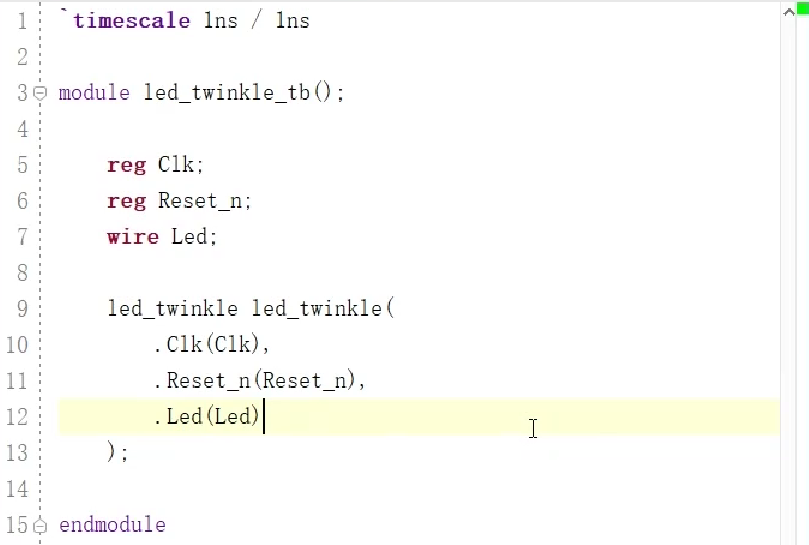

4.进行连线

定义完成后将其和被测试模块连接到一起,进行连线

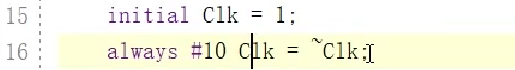

5.产生激励信号

产生时钟信号

- 20ns的周期对应10ns高电平,10ns低电平

- 先进行初始化

- always后没有其他内容,无条件的执行后面的内容,延时10ns后Clk取反,~代表按位取反

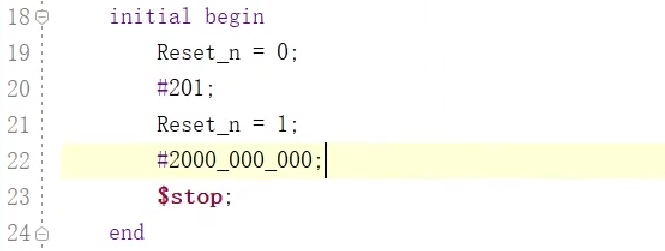

产生复位信号

- 先通过复位将D触发器的输出值设置为零,然后触发器从0开始,每个时钟周期加一

- 在仿真时间线上往后推移201ns,再将Reset_n信号拉高,这样系统就从复位状态恢复出来,开始正常计数

- #201:时钟每10ns翻转一次,10个时钟周期刚好200ns,即仿真的第200nsCLK信号刚好出现上升沿,如果此时Reset_n刚好从0到1,容易引起波形阅读的误会,影响对波形的分析,所以这里特意多等1ns

- #2000_000_000是2s

- $stop停止

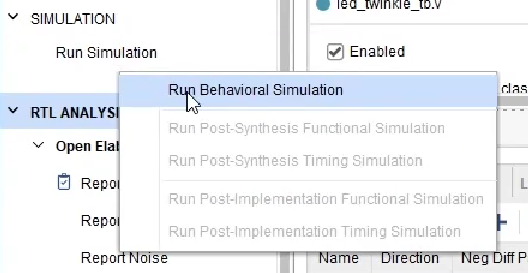

6.进行仿真

通过图示选项进行仿真

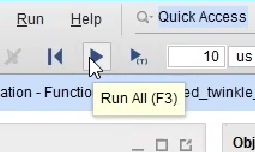

Vivado中的默认停止时间是1000ns,所以会在1000ns的时候停止,这是需要手动点击Run All让仿真继续运行

对于时序逻辑的仿真,在分析波形的时候需要看时间是否精准

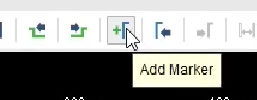

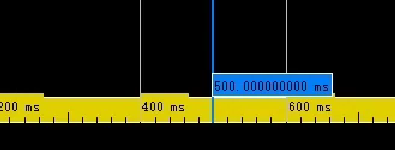

仿真软件有测量光标

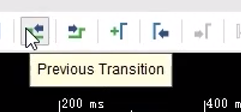

Previous Transition:前一个变化的位置

Add Marker:添加光标

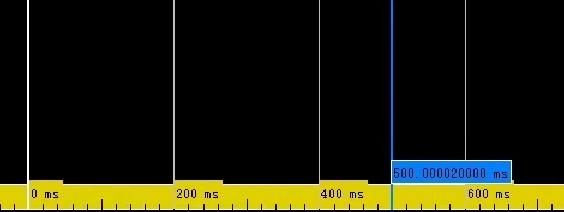

选中第一个蓝色标记线,会出现两个标记线之间的时间间隔

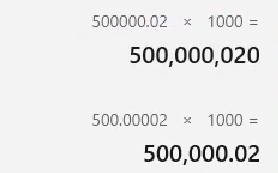

通过转换可得是500ms20ns,比预期的500ms多了20ns,刚好是一个CLK时钟周期的时间

计数器从最大值变为0也需要消耗一个时钟周期

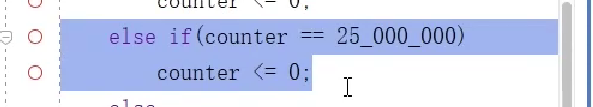

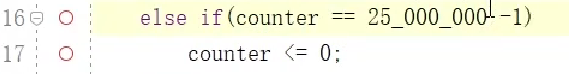

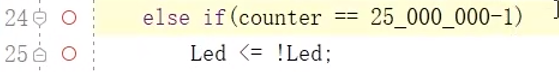

解决上述问题,只需要将原本设计好的计时最大值减1即可

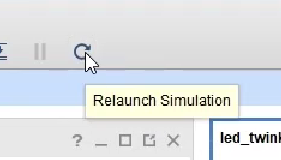

点击该图标,重新开始加载仿真

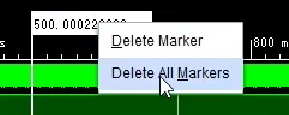

删除光标(右击光标就会出现)

Delete All Marker:删除所有光标

然后重新添加光标,重新吸附,可以看到时是500ns

initial reset信号在201ns之后才关断,所以实际计数信号是201纳秒才开始的。这个无所谓,电路一般都有个初始化过程。