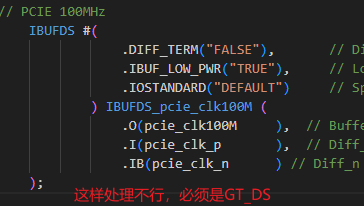

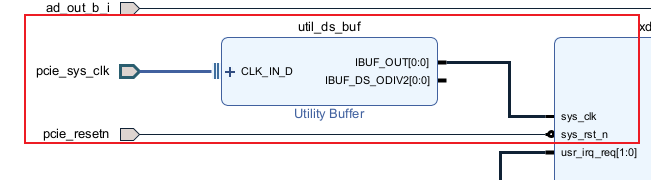

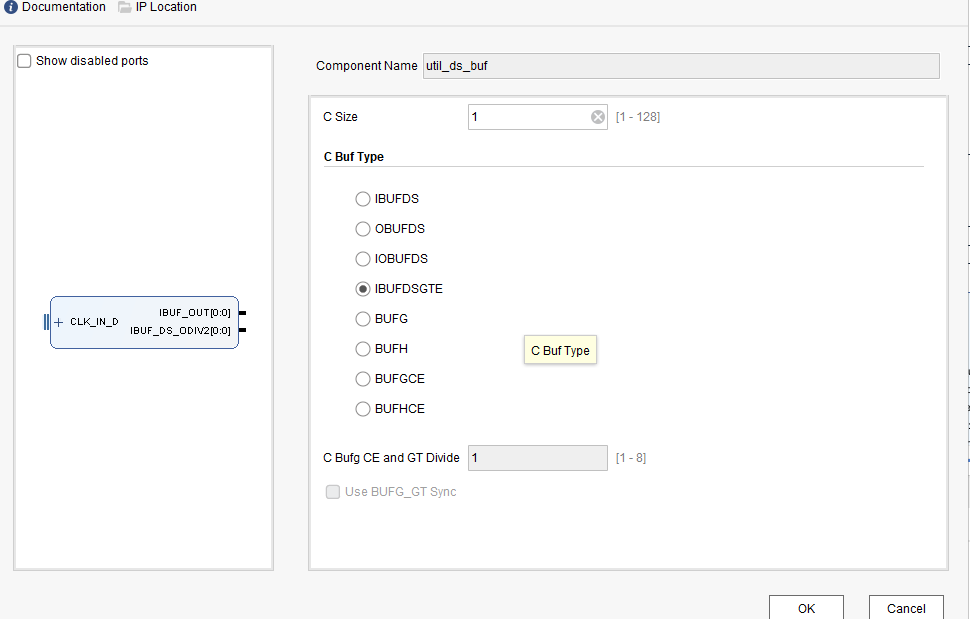

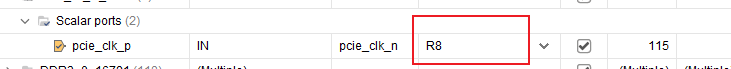

注意:pcie的参考时钟直接过IBUFDS不行,必须过IBUFDSGTE才可以绑定

成功绑定

当pcie的数据管脚的硬件连接与fpga默认的不一致时处理办法之一:

set_property PACKAGE_PIN {} [get_ports {pcie_rxp[*]}]

先将管脚置空,后再绑定

set_property PACKAGE_PIN {} [get_ports {pcie_rxp[*]}] #先将信号的管脚置空后再绑定

set_property PACKAGE_PIN AA4 [get_ports {pcie_rxp[0]}]

set_property PACKAGE_PIN Y6 [get_ports {pcie_rxp[1]}]

set_property PACKAGE_PIN W4 [get_ports {pcie_rxp[2]}]

set_property PACKAGE_PIN V6 [get_ports {pcie_rxp[3]}]

set_property PACKAGE_PIN T6 [get_ports {pcie_rxp[4]}]

set_property PACKAGE_PIN R4 [get_ports {pcie_rxp[5]}]

set_property PACKAGE_PIN P6 [get_ports {pcie_rxp[6]}]

set_property PACKAGE_PIN M6 [get_ports {pcie_rxp[7]}]

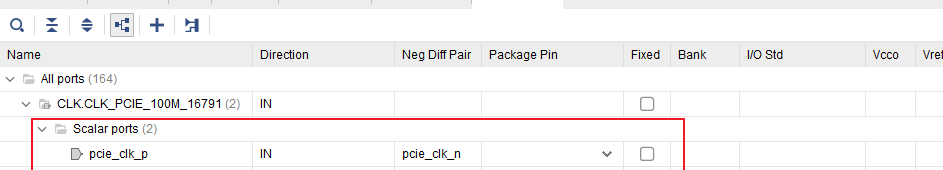

set_property PACKAGE_PIN R8 [get_ports {pcie_clk_p}]