晶振频率正确也可能导致系统采样错误、通信异常或启动不稳定,这通常与信号边沿速度和占空比有关。时钟信号不仅控制系统节拍,还定义每一拍的时序边界。

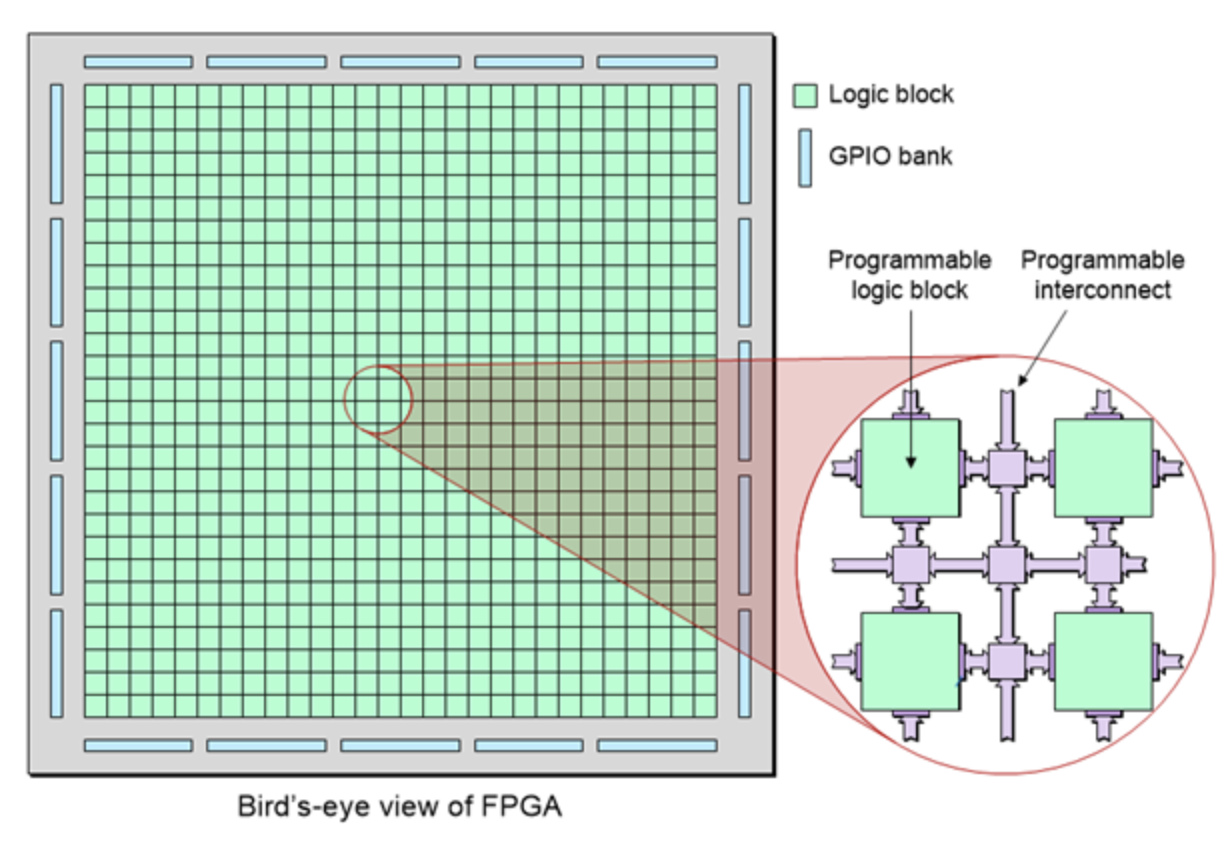

在微控制器(MCU)、现场可编程逻辑器件(FPGA)、以及串行器/解串器(SerDes)等高速器件中,信号边沿的微小偏差或抖动会影响采样精度。

在FPGA系统中,如果时钟上升沿过慢,不同逻辑通道间的采样触发点可能出现微秒级偏差,导致时序裕量被压缩;若占空比偏离50%,触发信号提前或滞后,也会增加抖动与误码风险。

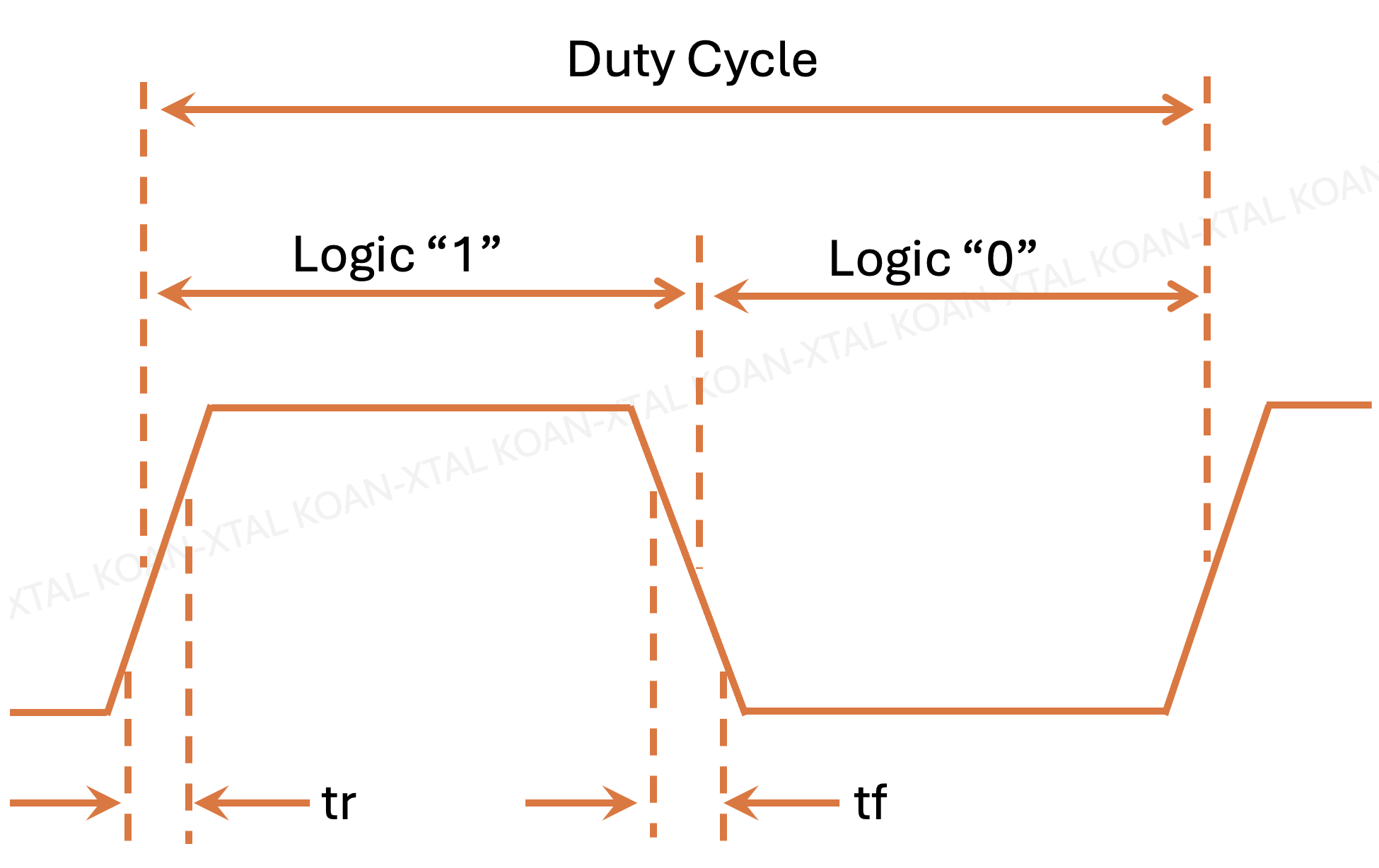

***1.***参数含义

当上升下降时间过慢或波形不对称时,时钟边界模糊,设备容易出现采样偏差。

- 上升时间Tr:信号从低电平的10%Vdd上升到高电平90%Vdd所需的时间。

- 下降时间Tr:信号从高电平的90%Vdd下降到低电平10%Vdd所需的时间。

- 占空比Duty Cycle:一个周期内,高电平持续时间占总周期的比例,理想值为50%。

***2.***影响晶振波形质量的主要因素

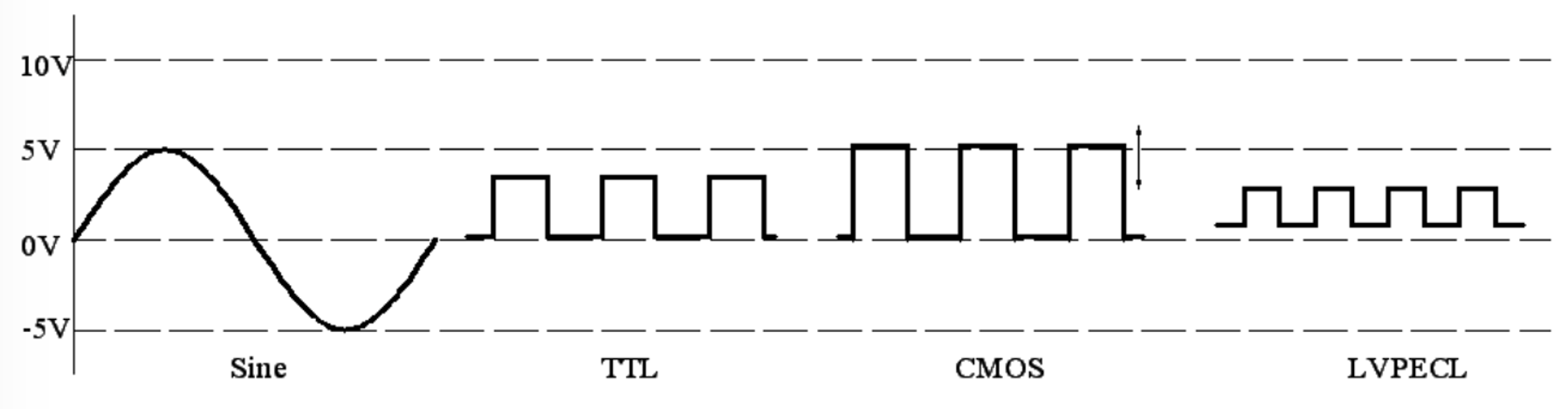

不同输出类型的晶振适用于不同场景:

- 差分输出晶振 (LVDS、HCSL、LVPECL):边沿快、幅度低、抗干扰强,适合高速数字接口或高同步精度系统。

- CMOS/TTL输出:性能稳定,适合控制类电路或通用逻辑系统。

- 射频/GPS系统:常用Clipped Sine或纯Sine输出,保证模拟信号完整性。

2.1 输出驱动结构

- CMOS输出采用推挽电路,性能受晶振驱动能力和输出端负载影响,负载过大或驱动不足会减慢边沿速度。

- LVDS/HCSL采用恒流差分驱动,信号变化快、对称性好,抗干扰能力强。

2.2 负载电容和PCB走线

晶振内部有典型负载电容(如15pF),保证波形稳定。实际电路中,PCB 走线、电路输入端和其他器件的电容会与晶振内部电容一起形成总负载:

- 总负载过大:上升/下降沿变慢;

- 总负载过小:波形尖锐但易振铃或抖动。

2.3 电源噪声

晶振对电源纹波敏感,电源噪声会导致输出抖动。设计时应加滤波电容,保持地平面连续,让高速信号有稳定返回路径,减少反射和干扰。

2.4 设计建议

- 总负载尽量接近规格书推荐值,可通过PCB走线长度、控制阻抗、匹配电容实现;

- 时钟走线短,阻抗约50Ω;

- 差分线等长,保证同时到达,减少干扰和失真;

- 走线远离高速信号和噪声源,必要时增加地隔离线。

**3.KOAN晶振实例

在设计中,特别关注晶振的关键性能指标,如上升/下降时间(Rise/Fall Time)、占空比(Duty Cycle)等,以确保输出信号符合目标器件的接口要求。晶振针对不同应用提供多种输出波形,包括LVDS、HCSL、Clipped Sine、Sine等。可满足通用控制、高速数字接口及射频/GPS系统的需求。

我们产品8MHz-CMOS输出的时钟振荡器的实测数据:

从测试数据可以看出:

- 上升/下降沿平滑,占空比接近50%,满足通用控制类数字接口要求;

- 通过合理PCB设计和电源滤波,晶振输出波形稳定,信号干扰小。