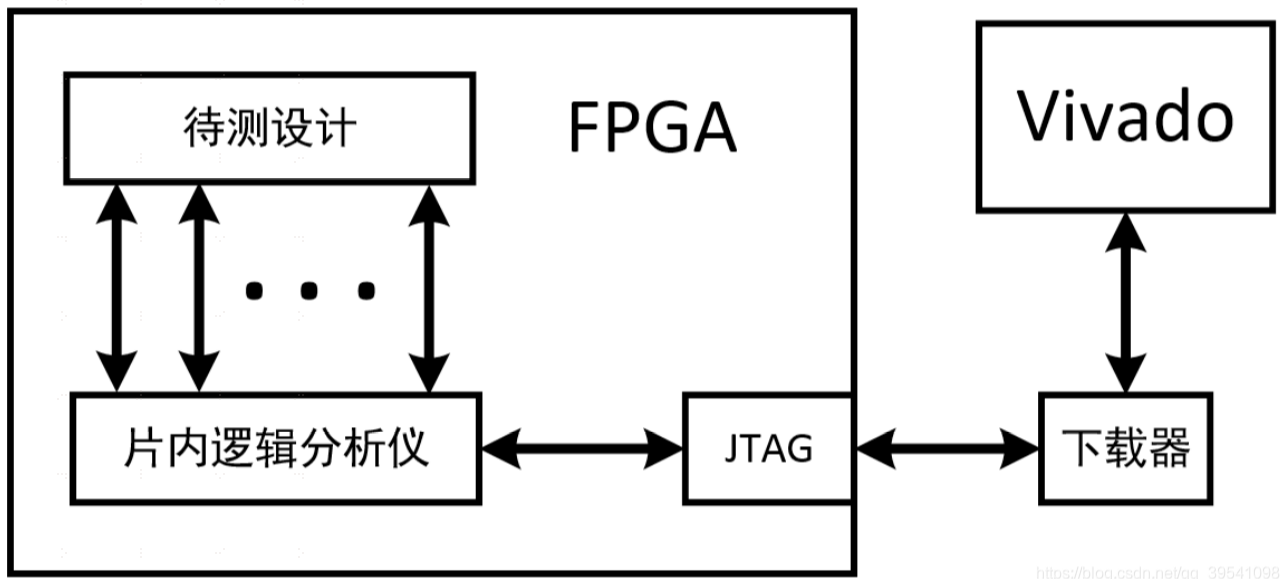

FPGA测试过程中可能会遇到一些信号状态定位困难的问题,有时候仿真并不能找出问题所在,尤其是使用Xilinx IP的设计。针对这种情况我们可以使用Vivado工具内置的ILA(在线逻辑分析仪),先在版本里插入逻辑分析仪,然后将测试机与单板通过JTAG接口连接,通过Vivado软件和串口操作进行波形抓取,定位问题所在。

1 逻辑分析仪插入方法一

2 逻辑分析仪插入方法二

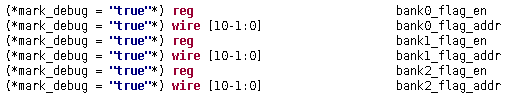

1.在代码中进行标记,在需要抓取的信号定义前面加上 (* mark_debug = "true" *) 即可进行标记,如下所示:

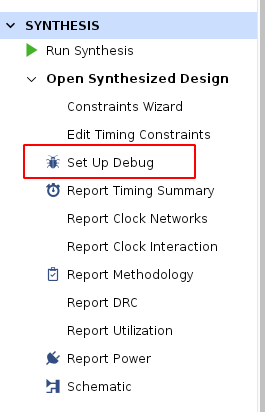

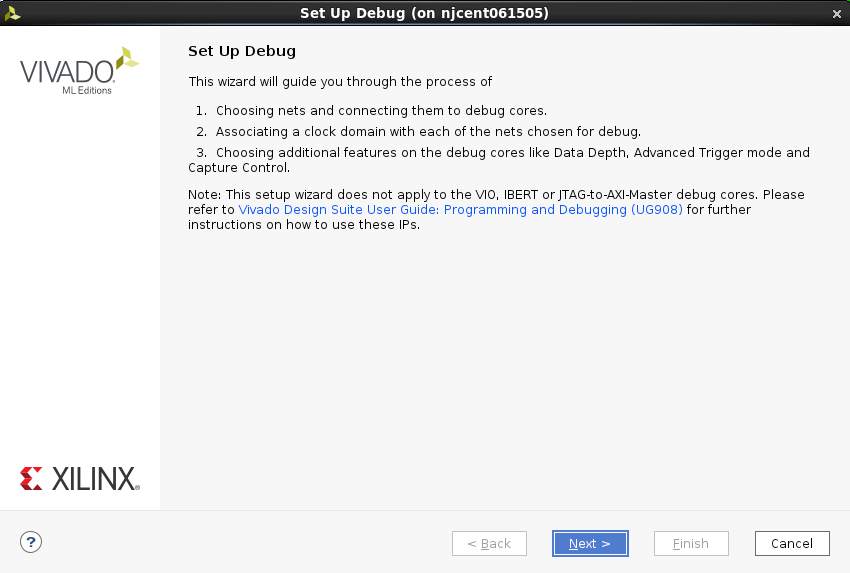

2.对工程进行综合,点击【Run Synthesis】,综合完成之后,综合完成后点击【Set up Debug】:

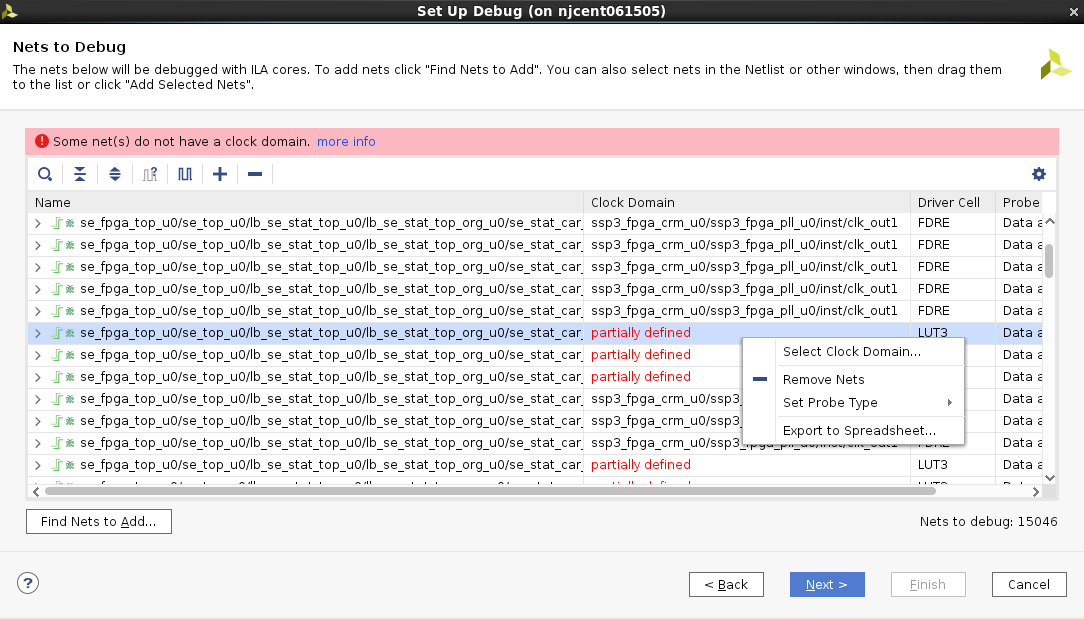

点击Next后,可以看到先前(*mark_debug = "true"*)标记的信号均已添加至列表,但有些信号的时钟未定义,选中后右键点击Select Clock Domain,选择一个频率相对较快的时钟即可:

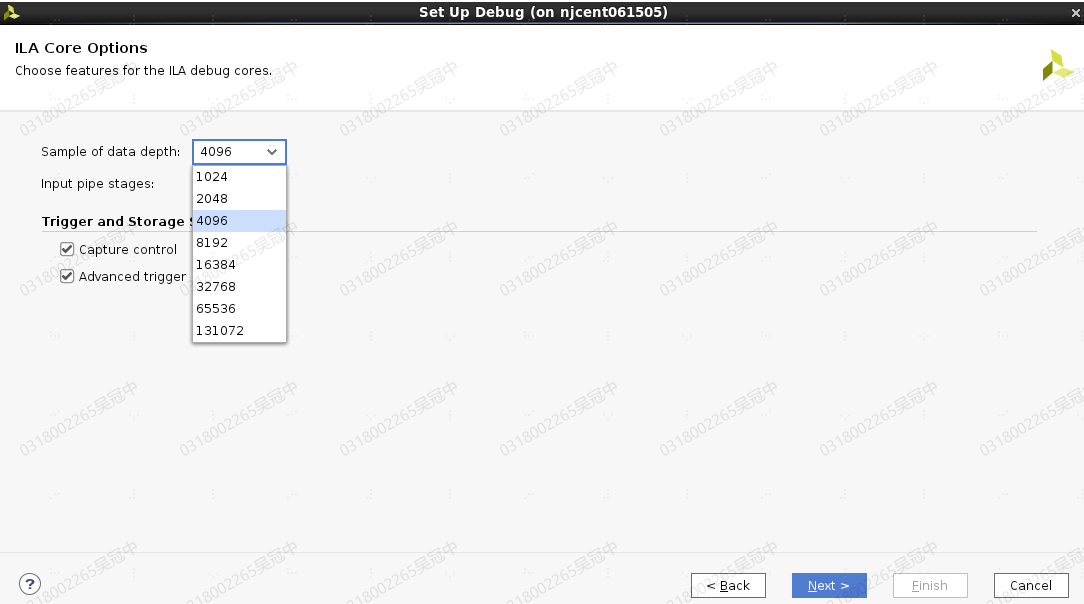

点击Next后,可对抓取波形的深度进行设置,根据实际需求和资源情况按需设置,勾选Trigger and Storage Setting:

3.设置完成后会生成新的xdc约束文件,保存后生成bitstream。

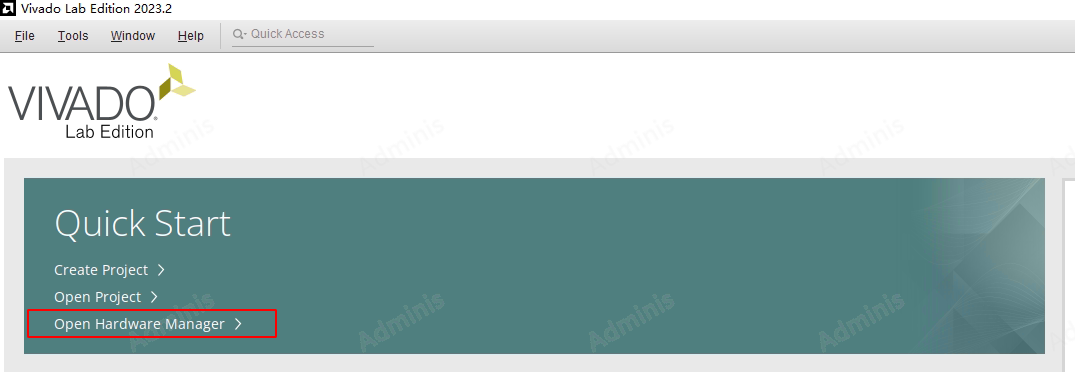

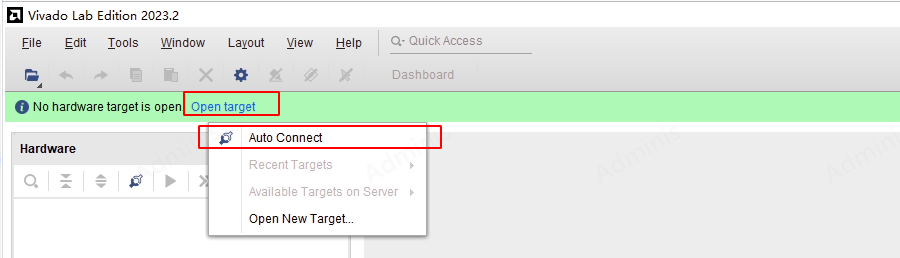

4.在测试机打开vivado,点击[Open Hardware Manger]。jtag接线完成的情况下,点击Open target,再点击auto connect:

5.连接成功后,右键选择Program Device烧录对应bit文件和ltx文件。

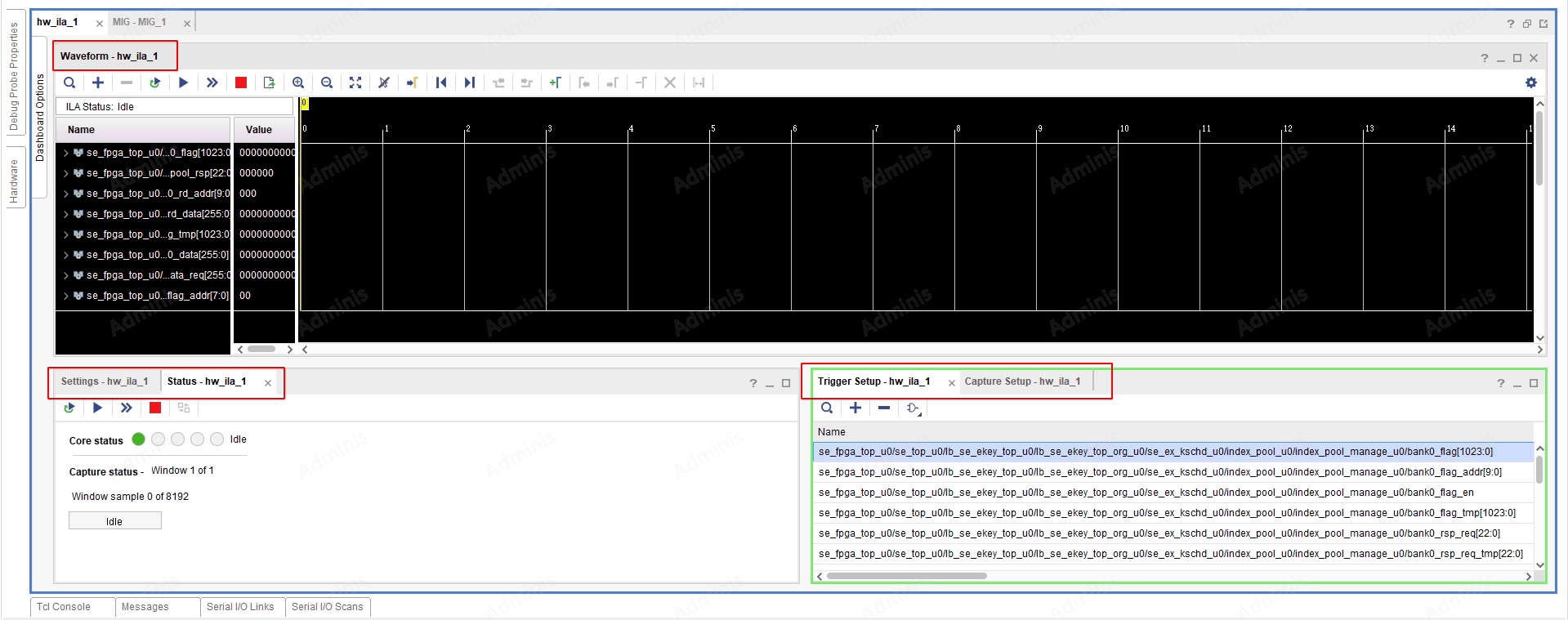

6.bitstream文件和debug文件烧录完成后会自动出现如下图所示界面,该界面即 ILA 调试界面。

1)波形显示窗口,可以通过点击+添加想查看的波形的信号,这里面包括之前所有标记的信号;

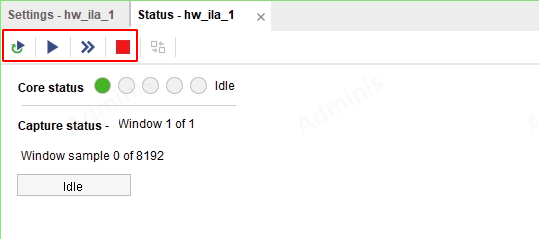

2)ILA Croe 的状态控制和显示窗口,四个按键从左到右功能依次是

<1>设置采样执行过程为循环采样。

<2>启动采样按钮。按下后将启动 ILA 采样,记录触发条件第一次满足的波形,最常用。根据是单次采样还是循环采样,以及是有条件触发还是无条件触发,启动采样后,会呈现 ILA 状态的周期性变化或等待触发条件的到来。

<3>无条件执行 ILA 采样(记录当前最新时间波形)。

<4>停止采样。

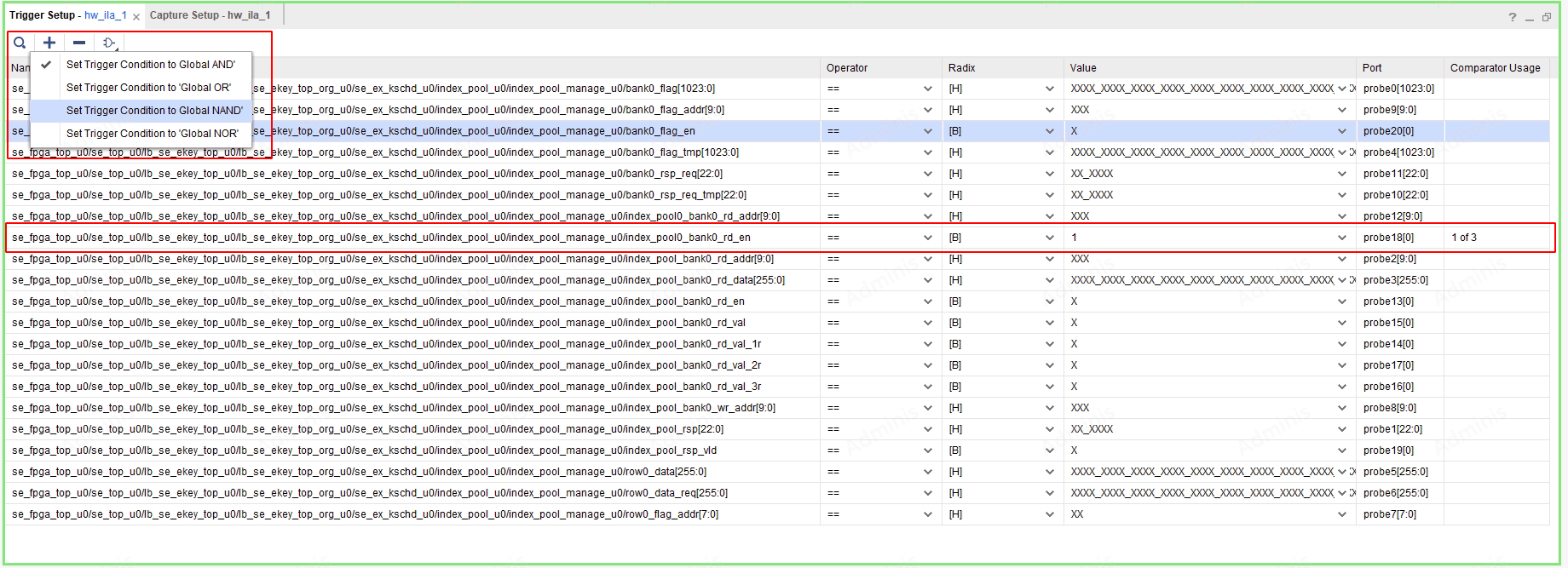

3)触发信号设置窗口,点击窗口内+添加产生触发条件的信号,添加之后如可以设置其触发条件和触发情况。支持设置多个信号产生触发信号时的条件,与、或、同或、异或;也可以只设置一个信号的触发条件。

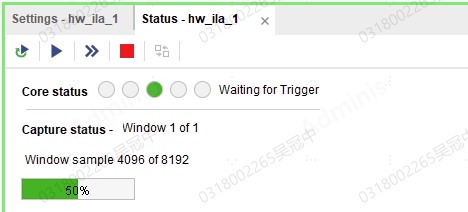

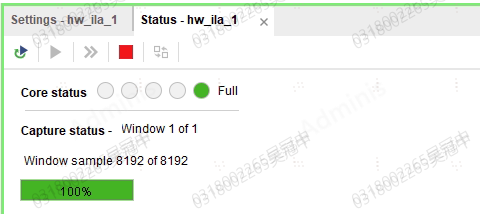

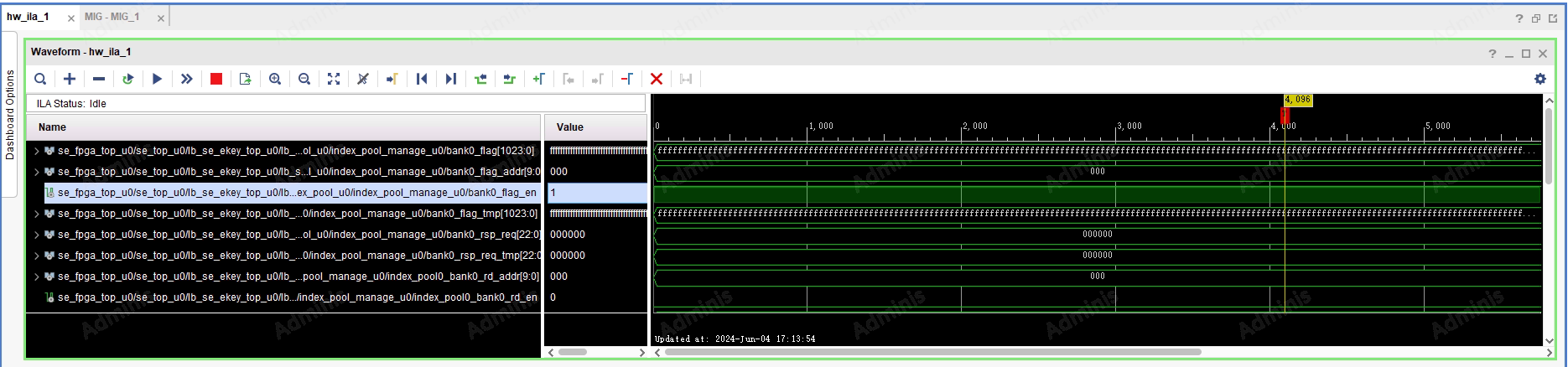

7、触发条件设置完成后,点击运行,此时等待触发状态为50%。软件进行发流测试,满足触发后状态变为100%,波形输出显示:

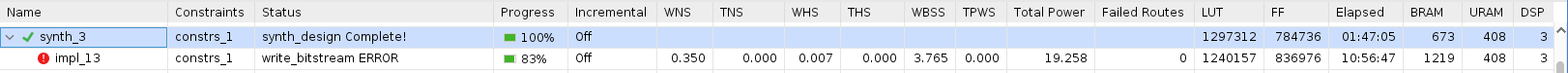

3 综合实现均正常通过情况下,bitstream生成失败

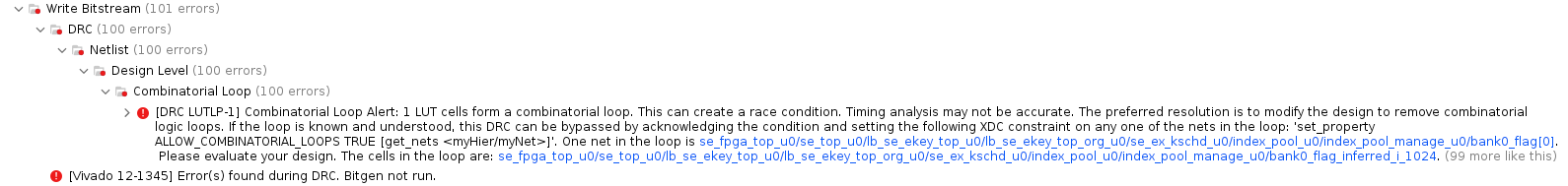

Vivado综合和实现完成后,在生成bitstream文件时出现已知设计原理的DRC错误,例如下面图中的DRC LUTLP-1的loop错误是添加ILA IP后引入的:

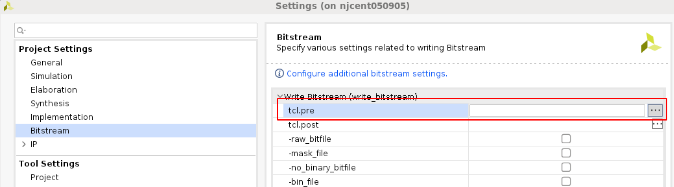

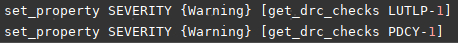

对于这种设计可接受的错误,可以在每次生成bitstream在setting设置界面的tcl.pre出添加一个tcl文件,文件内使用set peoperty设置把对应规则从error降为warning:

另一种方法是,将上述两条命令加到xdc文件的最后。

设置完成后,即可生成工程的bitstream。