IP核之PLL

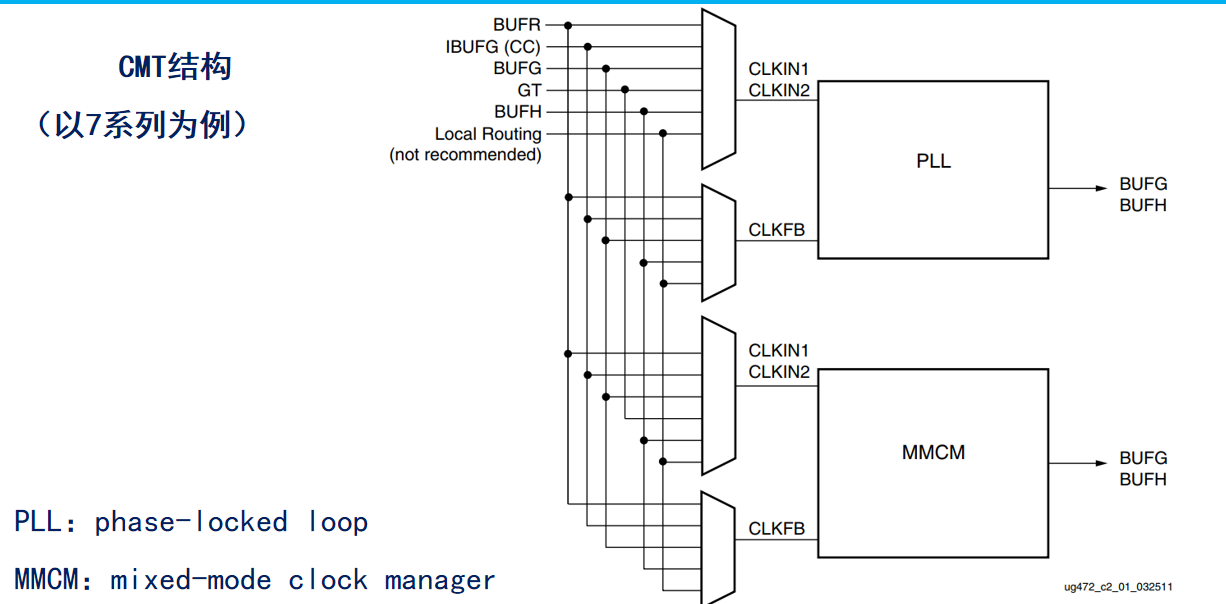

Xilinx FPGA的时钟管理

CMT(Clock Management Tiles):时钟管理单元,可以对时钟进行管理,具有时钟倍频、分频、相位偏移、可编程占空比和优化抖动等功能。

MMCM和PLL

1.MMCM是在PLL基础上加入DCM(数字时钟管理单元)的一部分以进行精细的相移,即MMCM在PLL的基础上加上了相位动态调整功能。MMCM相对PLL的优势就是相位可动态调整,但PLL占用的面积更小

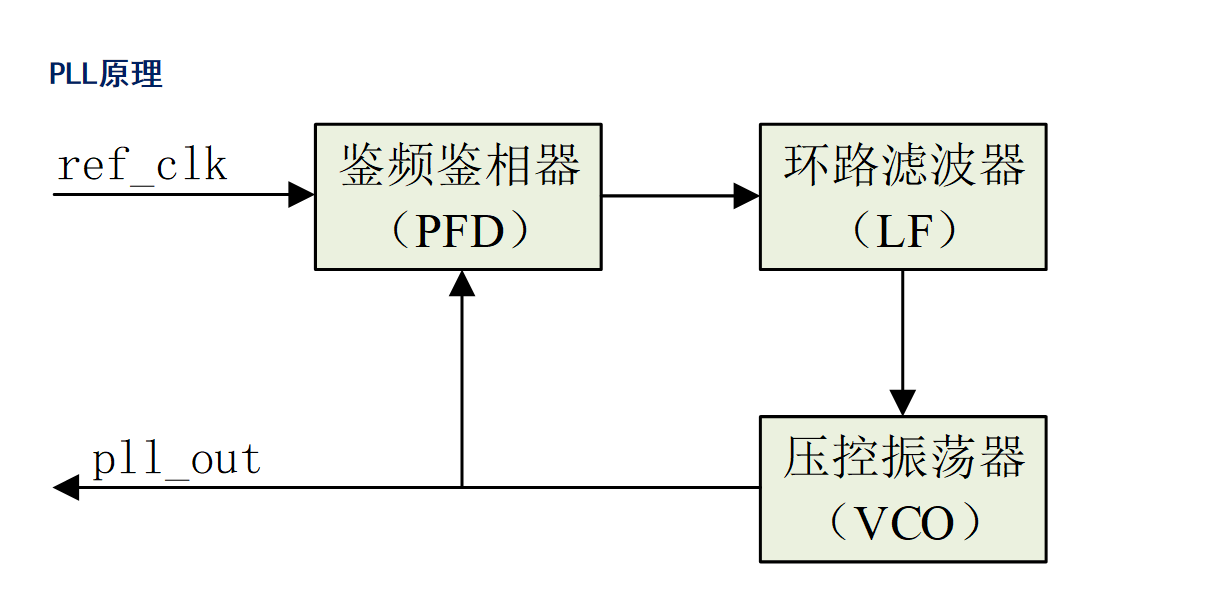

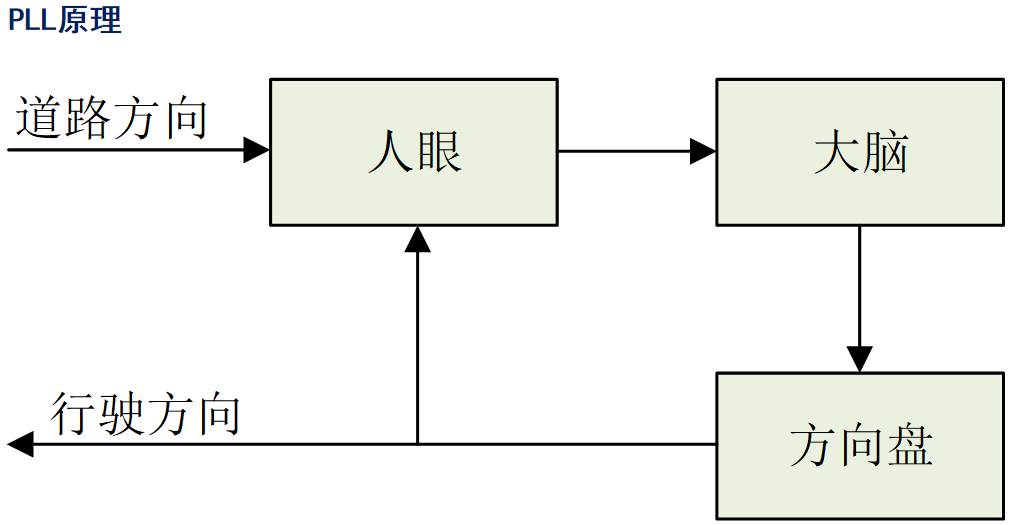

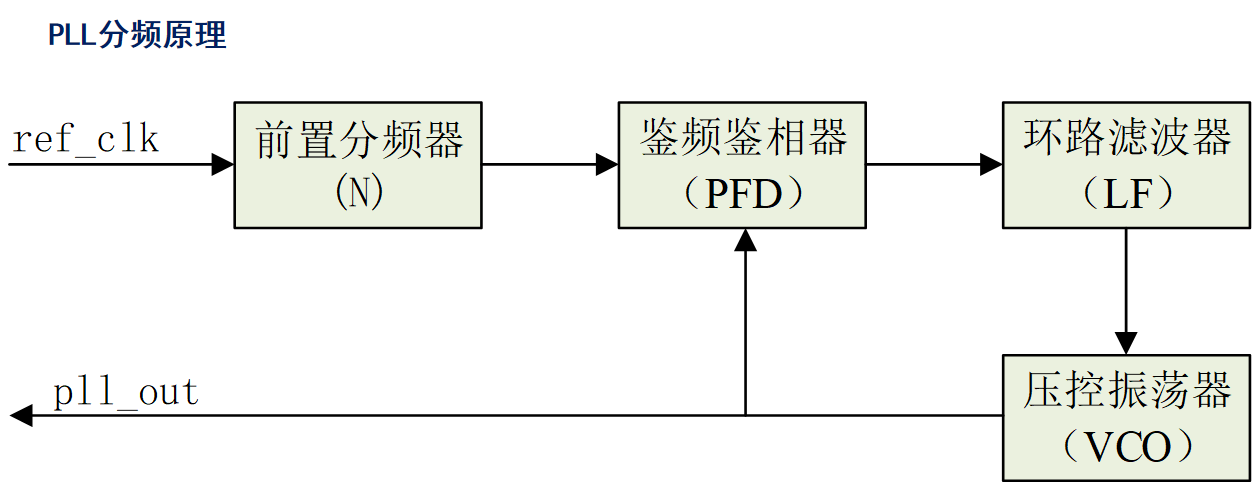

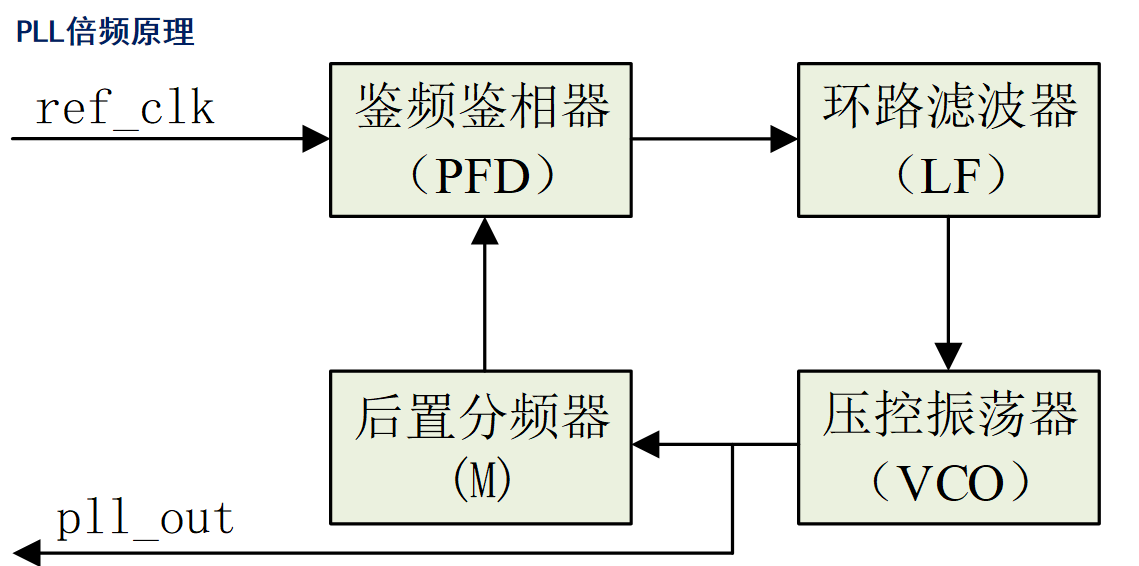

2.PLL:Phase Locked Loop(锁相环)PLL是一种时钟反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。

ref_clk:参考时钟源输入

PFD:将ref_clk的频率、相位和pll_out相比较

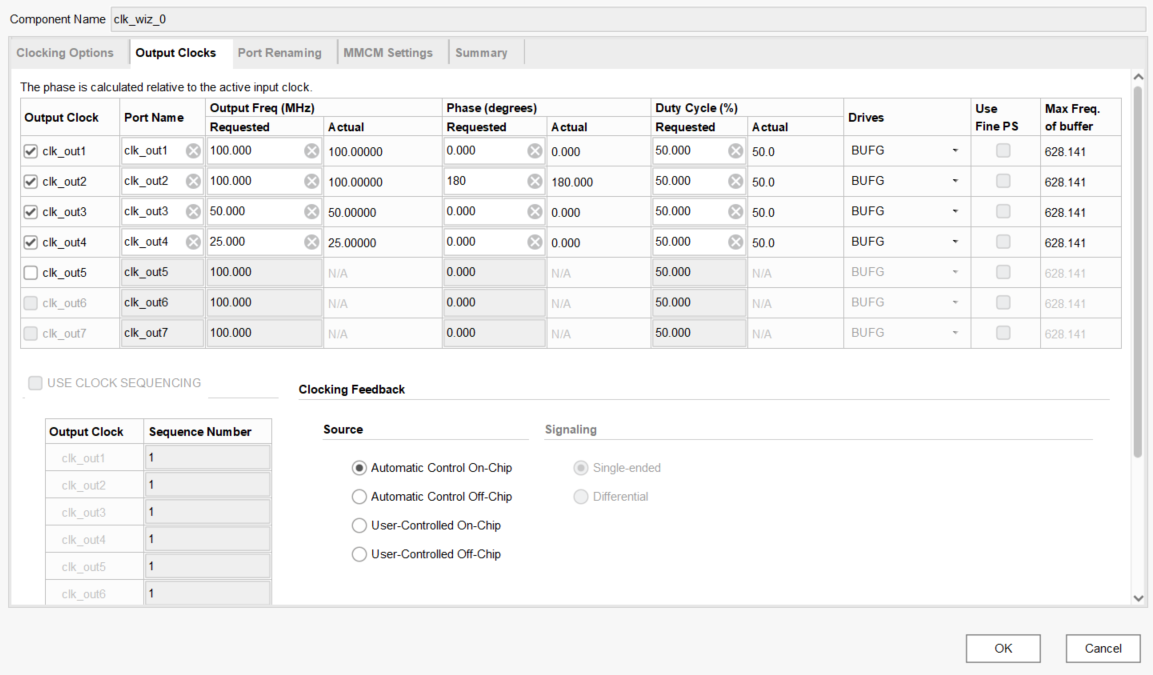

实验任务

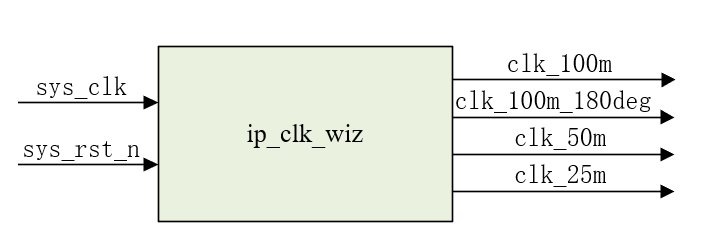

使用开发板输出4路不同频率或相位的时钟,时钟分别为100Mhz,100Mhz(相位偏移180度)、50Mhz和25Mhz。将四路时钟分别输出至扩展口的端口,并通过示波器来测量输出结果是否正确。

系统框图

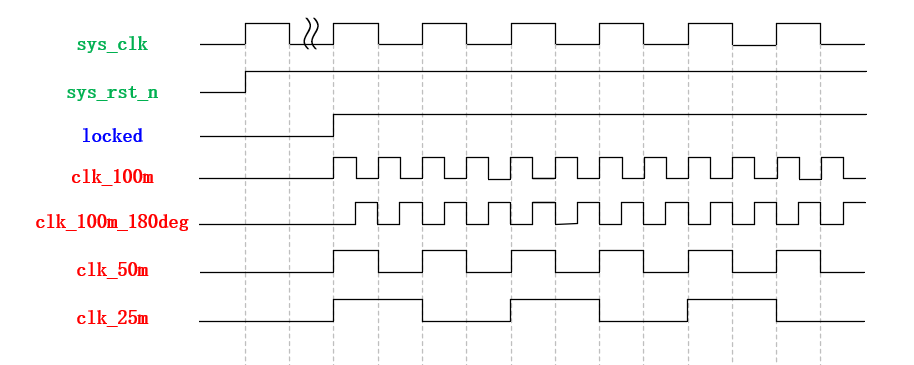

波形图

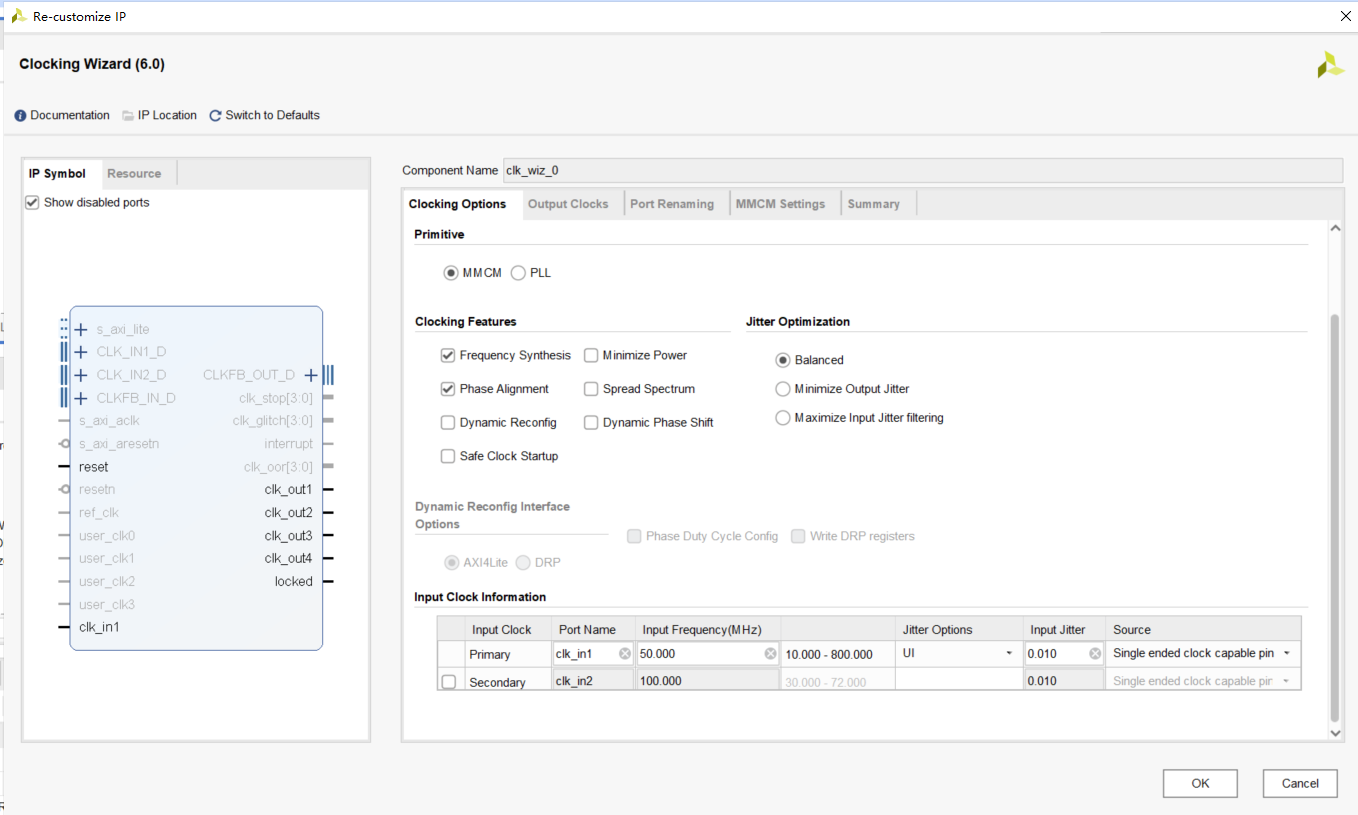

IP核配置

IP核例化代码

module ip_clk_wiz(

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

//输出时钟

output clk_100m , //100Mhz时钟频率

output clk_100m_180deg, //100Mhz时钟频率,相位偏移180度

output clk_50m , //50Mhz时钟频率

output clk_25m //25Mhz时钟频率

);

//wire define

wire locked;

//*****************************************************

//** main code

//*****************************************************

//PLL IP核的例化

clk_wiz_0 clk_wiz_0

(

// Clock out ports

.clk_out1 (clk_100m ), // output clk_out1

.clk_out2 (clk_100m_180deg), // output clk_out2

.clk_out3 (clk_50m ), // output clk_out3

.clk_out4 (clk_25m ), // output clk_out4

// Status and control signals

.reset (~sys_rst_n ), // input reset

.locked (locked ), // output locked

// Clock in ports

.clk_in1 (sys_clk ) // input clk_in1

);

endmoduleFPGA激励文件(Testbench)编写,其用于验证FPGA设计功能正确性的测试脚本,通过模拟输入信号并检查输出响应,确保设计符合预期。

`timescale 1ns / 1ps //仿真单位/仿真精度

module tb_ip_clk_wiz();

//parameter define

parameter CLK_PERIOD = 20; //时钟周期 20ns

//reg define

reg sys_clk;

reg sys_rst_n;

//wire define

wire clk_100m;

wire clk_100m_180deg;

wire clk_50m;

wire clk_25m;

//信号初始化

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

//产生时钟

always #(CLK_PERIOD/2) sys_clk = ~sys_clk;

ip_clk_wiz u_ip_clk_wiz(

.sys_clk sys_clk ),

.sys_rst_n (sys_rst_n ),

.clk_100m (clk_100m ),

.clk_100m_180deg (clk_100m_180deg),

.clk_50m (clk_50m ),

.clk_25m (clk_25m )

);

endmodule时钟IP核的仿真

.xdc文件

#时序约束

create_clock -period 20.000 -name sys_clk [get_ports sys_clk]

#IO引脚约束

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN N16 IOSTANDARD LVCMOS33} [get_ports sys_rst_n]

set_property -dict {PACKAGE_PIN U20 IOSTANDARD LVCMOS33} [get_ports clk_100m]

set_property -dict {PACKAGE_PIN T20 IOSTANDARD LVCMOS33} [get_ports clk_100m_180deg]

set_property -dict {PACKAGE_PIN N18 IOSTANDARD LVCMOS33} [get_ports clk_50m]

set_property -dict {PACKAGE_PIN P19 IOSTANDARD LVCMOS33} [get_ports clk_25m]