一,

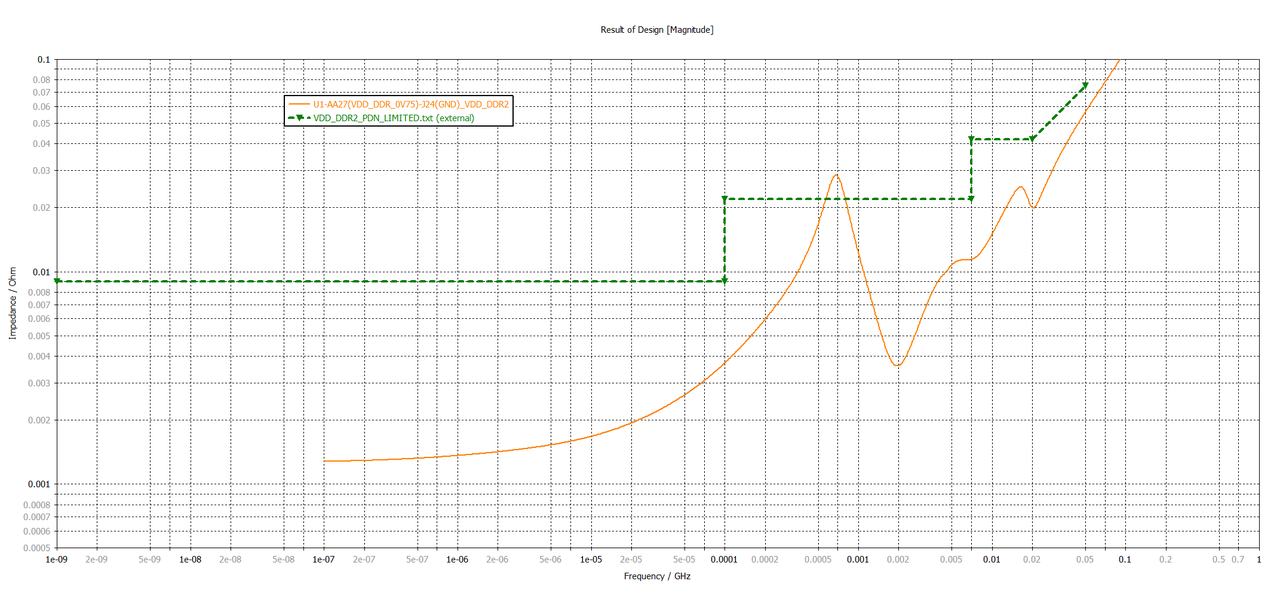

VDD_DDR2:

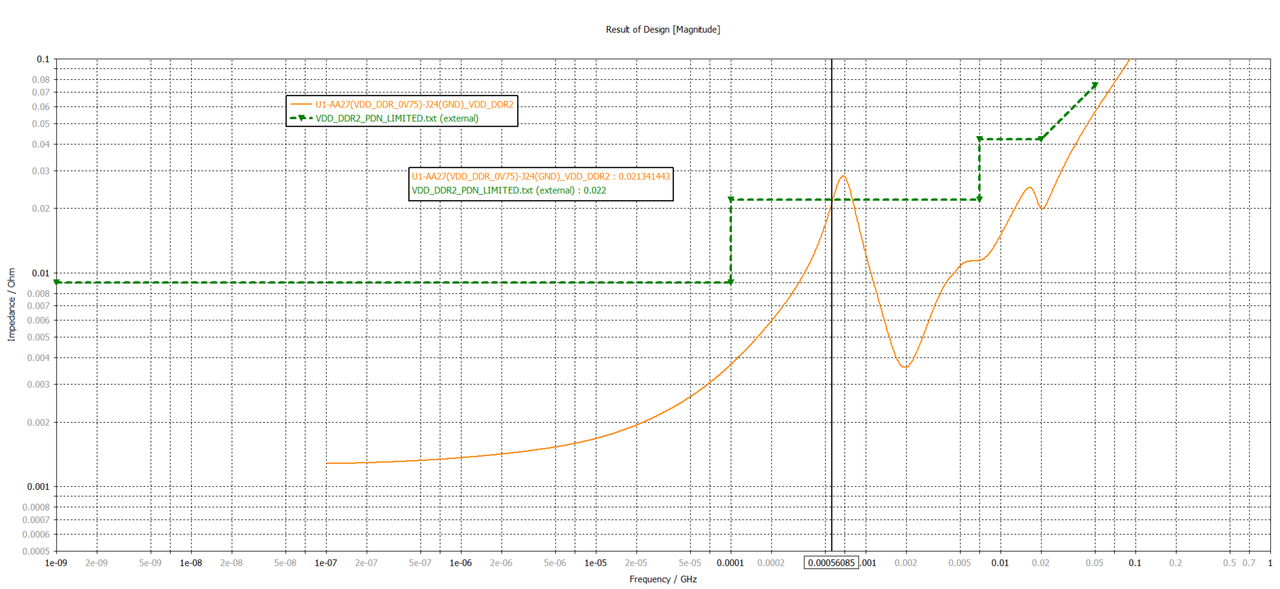

0-100KHZ,阻抗要求是9mohm;

0.1MHz--7MHz,阻抗要求是22mohm;

7MHz--20MHz,阻抗要求是42mohm;

50MHz,阻抗要求是75mohm;

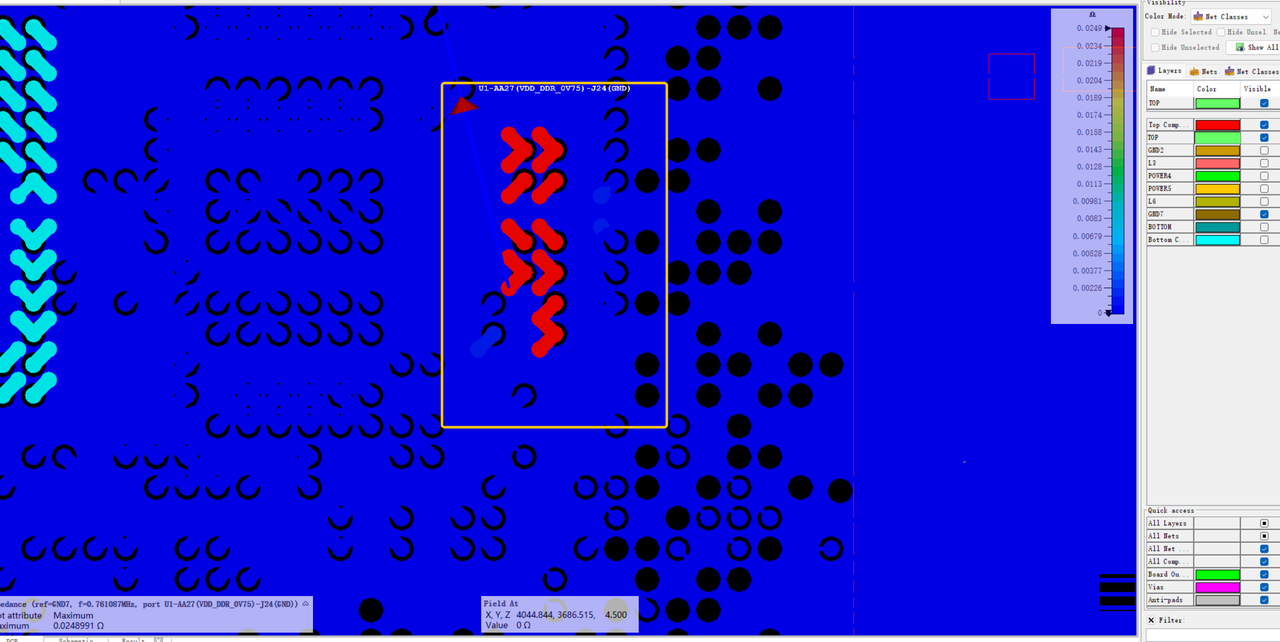

重新仿真去分析一下,我们接着看右边的边的VDD_DDR2这组。

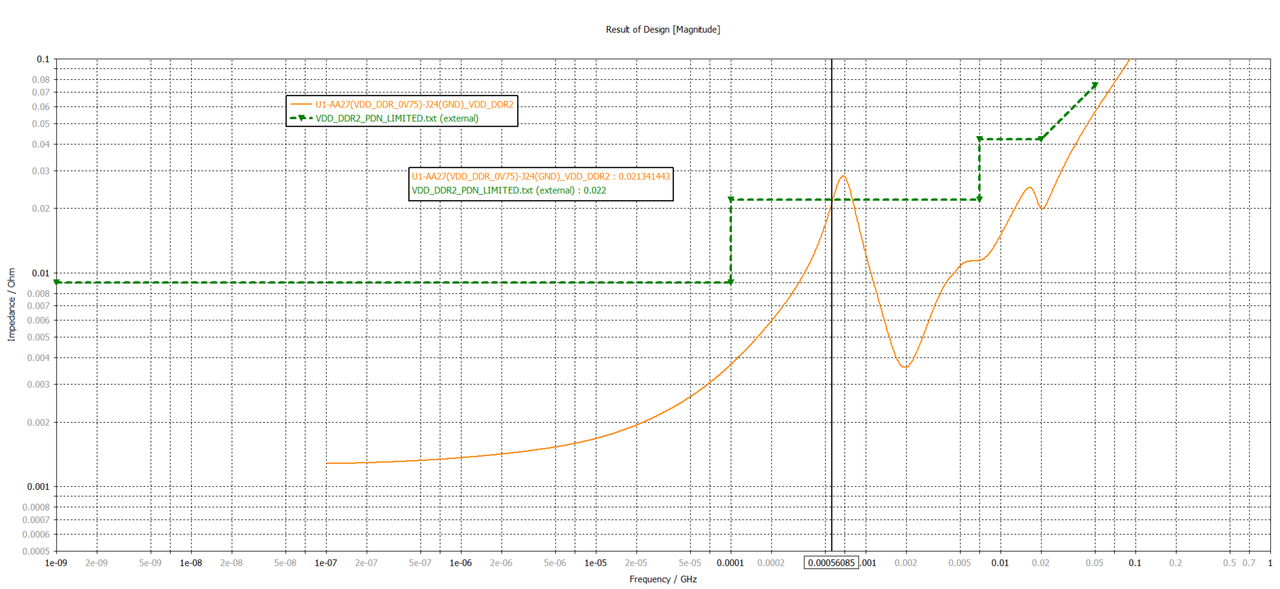

二,VDD_DDR2的电源网络PDN的仿真结果如下所示:

结果是在0.5MHz-0.7MHz之间是不满足要求的

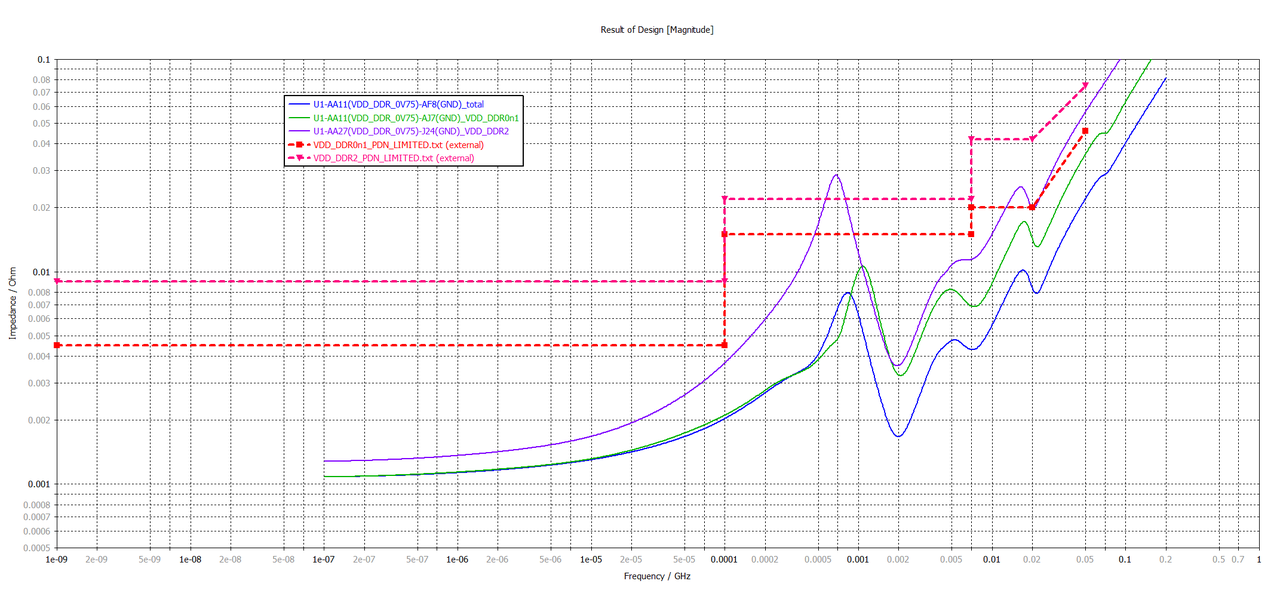

三,总的结果放在一起看下:

那我们改如何去改善VDD_DDR2的电源网络0.5MHz-0.7MHz之间是不满足要求的这个现象?

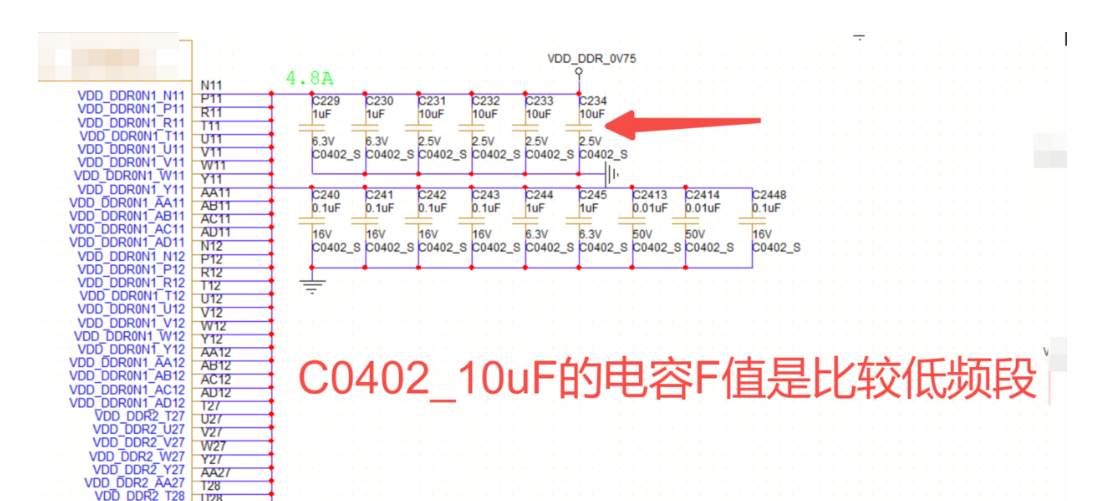

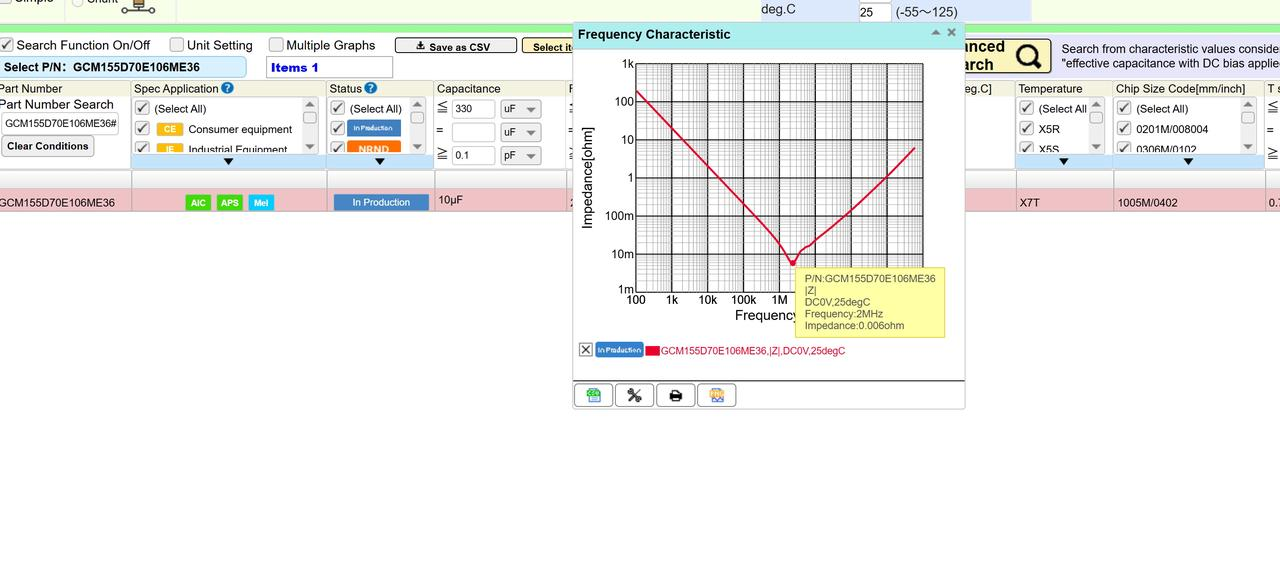

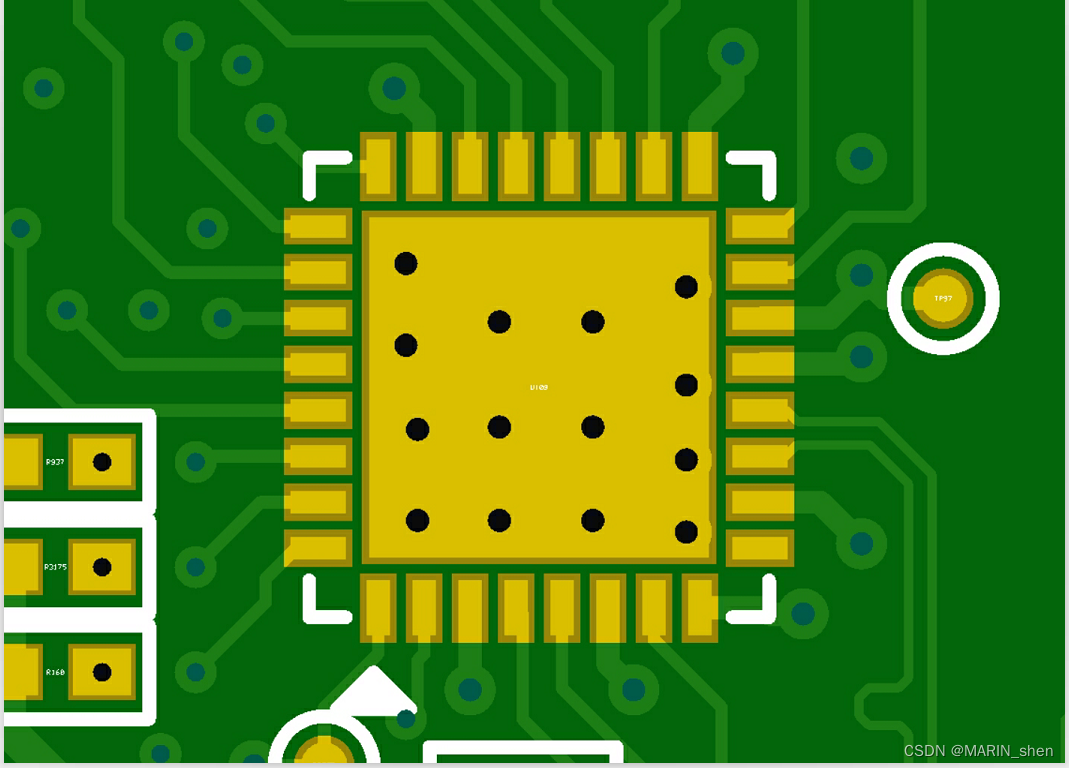

四,通过负载芯片上原理图的设计发现只有C0402_10uF的电容勉强算是相对来说是低频段的了,这个电容的阻抗频率特性曲线如下所示:F=2MHz,阻抗是最低为6mohm。

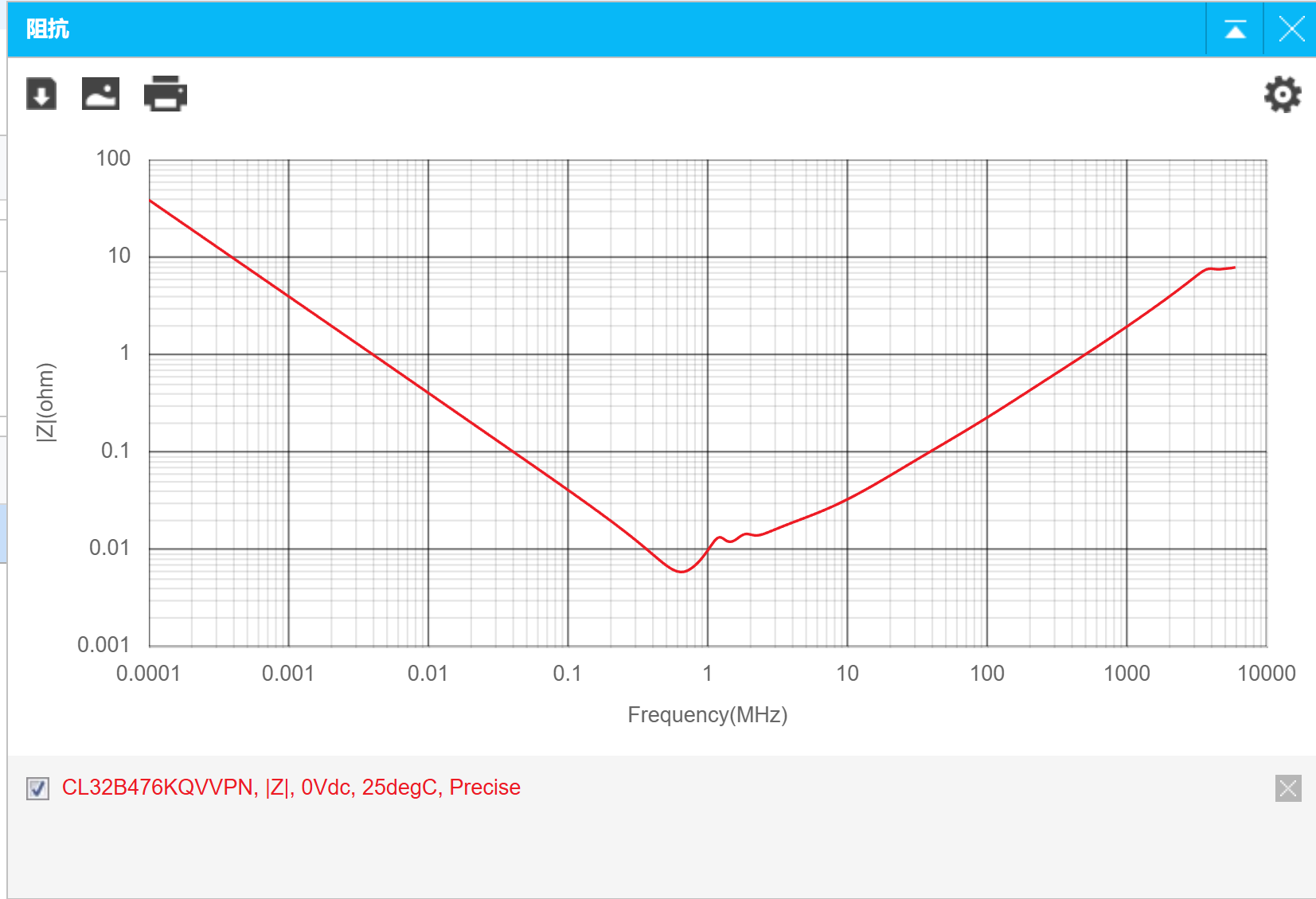

VRM芯片端口的C1210_47uF的电容:供应商为三星,

这颗电容物料为1210封装的容值为47uF,相对于负载BGA芯片里面的小容值小封装的电容C0402_0.1uF属于比较大的电容了,

五,这个波峰的造成原因主要是由于C1210_47UF的电容和C0402_10UF的电容以及C0402_1UF 的并联反谐振造成的,我们可以试着从减少C1210_47UF的电容的ESL或者是降低C0402_10UF的电容以及C0402_1UF 的ESR来着手去解决。

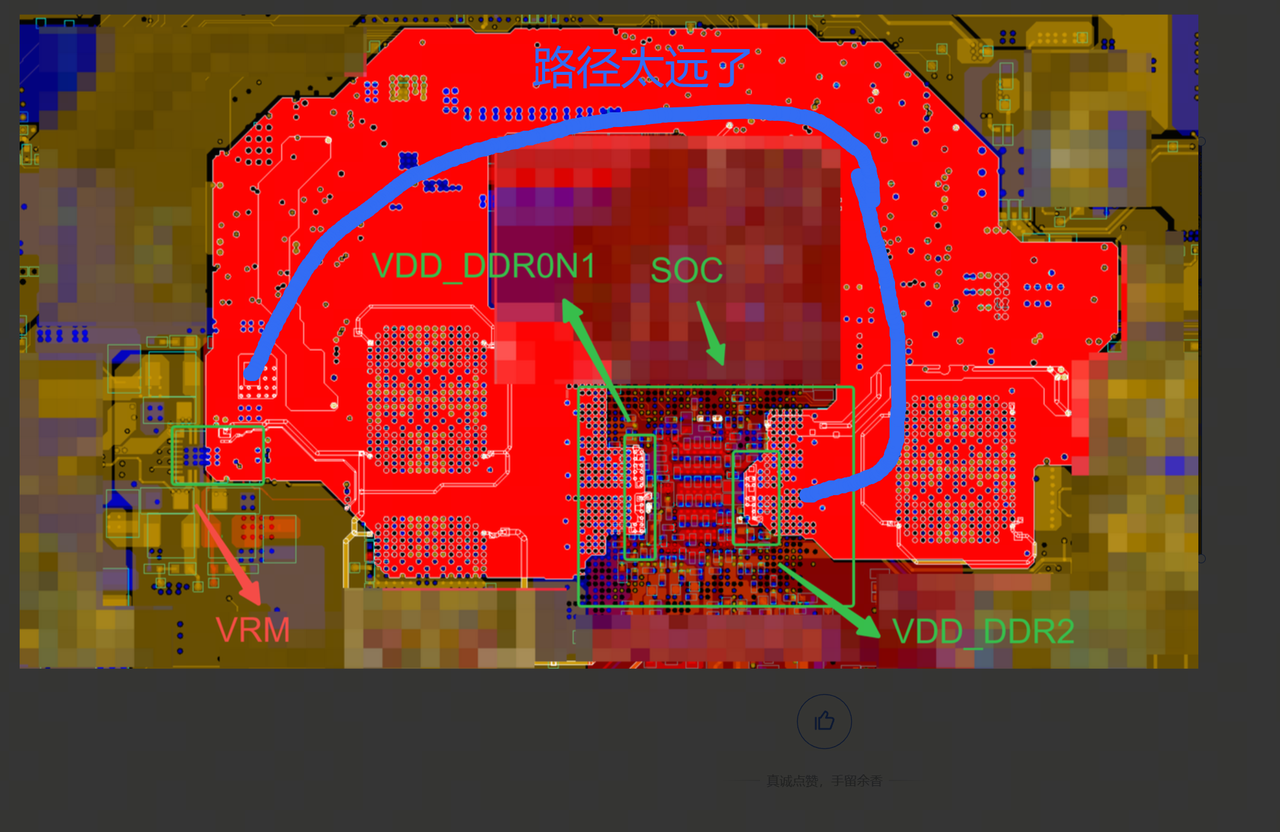

六,通整体的布局来看,造成这个0.5MHz-0.7MHz之间是不满足要求的原因主要还是VRM模块的布局离主芯片上的VDD_DDR2的电源网络管脚位置太远了,理想的VRM布局位置其实还是在中心的位置比较好些,这样离左右两边的负载端口的距离都差不多了。

七,还有一个改善的方式就是在内层补偿这个电源网络的铺铜面积,主要补偿的是阻抗最低的路径上的铜皮的面积,当然了前提是层面足够的情况下。

以上就是本期的所有内容了,我们下期文章不见不散了,最后记得点赞加关注哦。

--------声明:本文属于小编的原创文章,如需转载请注明来源!