本文详细介绍基于Terasic FPGA开发板TSP(又名C5P和OSK)和其板载CP2102N USB-UART桥接芯片的串口通信系统设计与实现。系统采用Verilog HDL编写UART收发控制器,通过CP2102N实现FPGA与PC间的快速稳定通信。

关于串口通信的基础知识请参考之前文章:1-串行通信基础知识

1 CP2102N简介及其驱动安装

查阅数据手册TSP_v.x.x.x_SystemCD\Datasheet\Uart_to_USB\cp2102n-datasheet.pdf可知CP2102N关键特性:

-

支持300bps至3Mbps波特率

-

内置USB 2.0全速控制器

-

自动波特率检测和信号极性控制

-

3.3V UART接口电平,与FPGA直接兼容

在之前文章1-串行通信基础知识提到在使用UART转USB口之前,主机需要安装串口驱动程序,在操作系统中创建一个虚拟串口(如 COM3)。这样,上位机软件就可以像操作传统串口一样,通过这个虚拟串口与 FPGA 通信了。

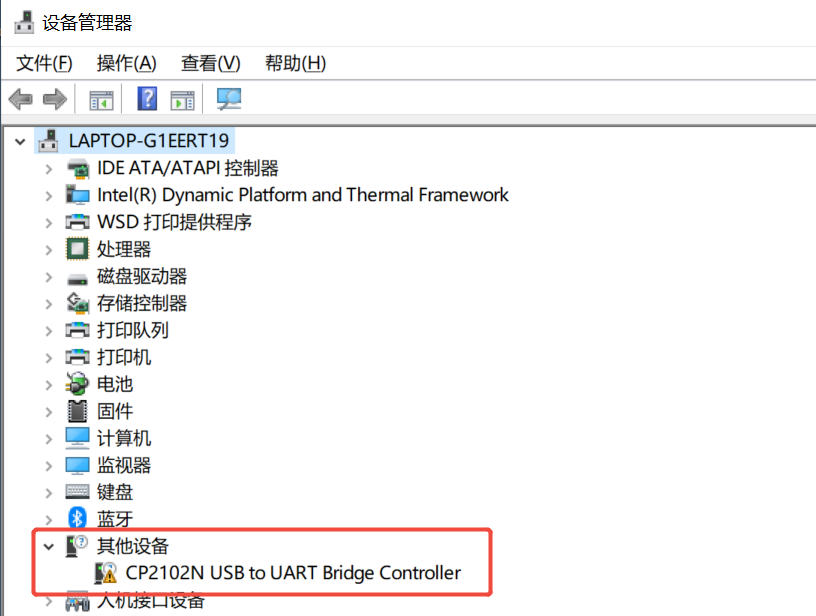

当TSP开发板的串口J6口插到PC的USB口以后,电脑设备管理器会出现如下设备:

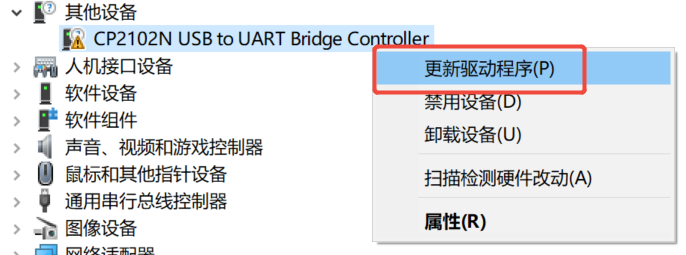

右击选中CP2102N USB to UART Bridge Controller 设备,选择更新驱动程序(P):

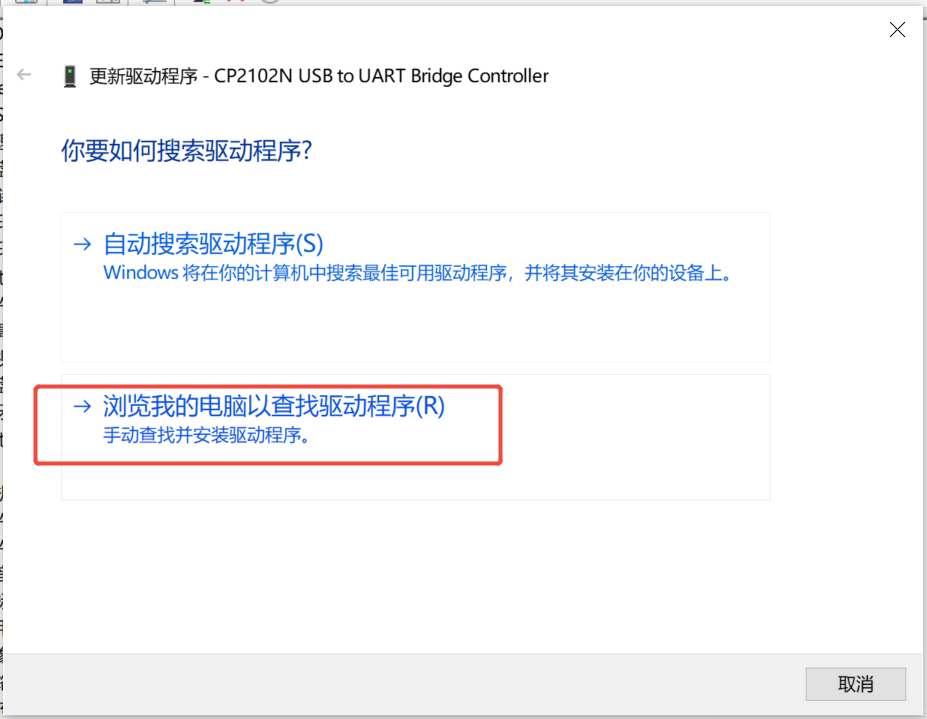

然后选择浏览我的电脑以查找驱动程序(R):

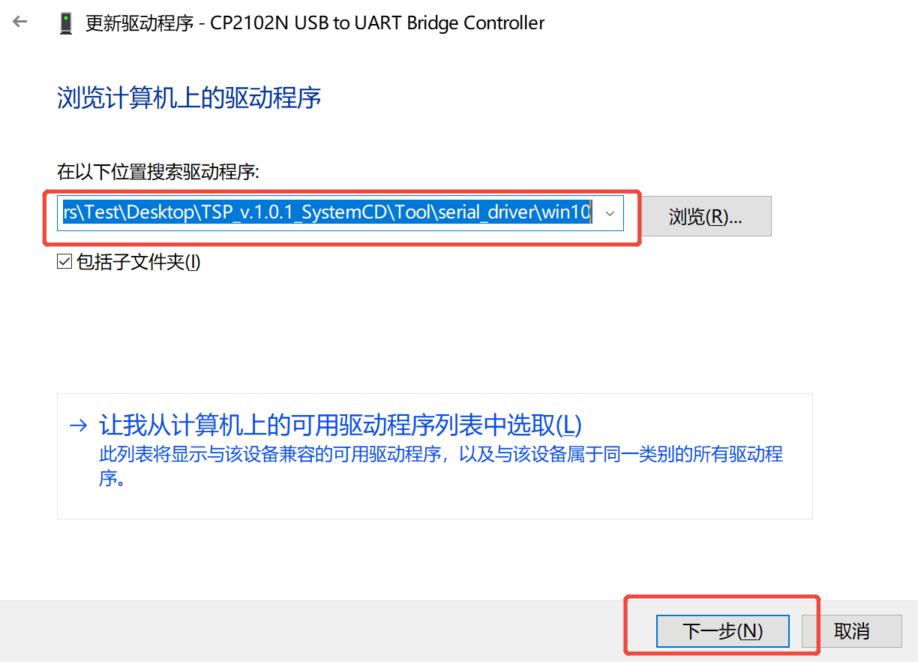

CP2102N的PC端驱动文件在TSP_v.x.x.x_SystemCD\Tool\serial_driver(该压缩包在友晶官网下载)路径下, 比如您的电脑当前版本是Win10, 事先解压win10文件夹下的CP210x_Universal_Windows_Driver.zip压缩包到当前路径,然后将驱动路径指到刚解压的文件路径:

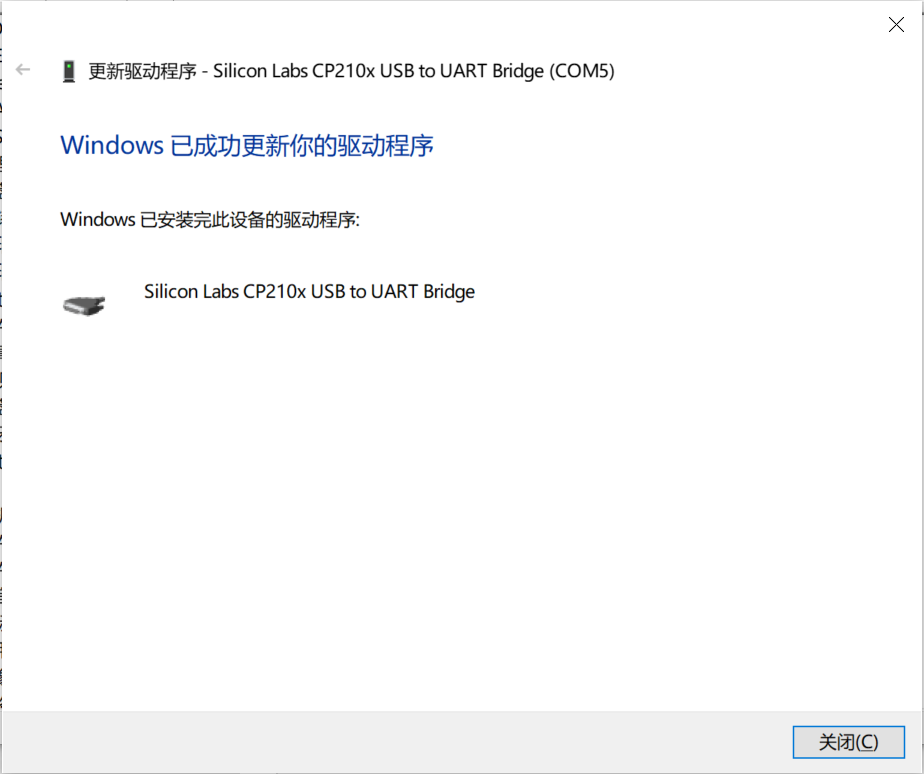

在点击下一步后会弹出驱动安装成功窗口,最后点击关闭按钮即可:

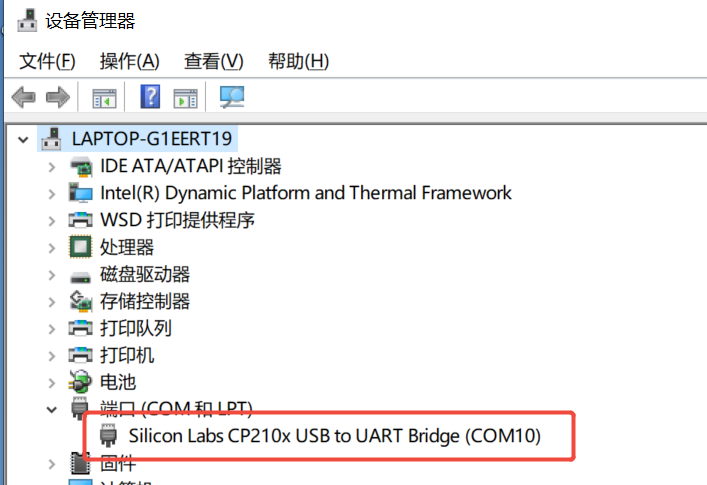

安装以后PC设备管理器如下:

1

TSP的串口硬件电路

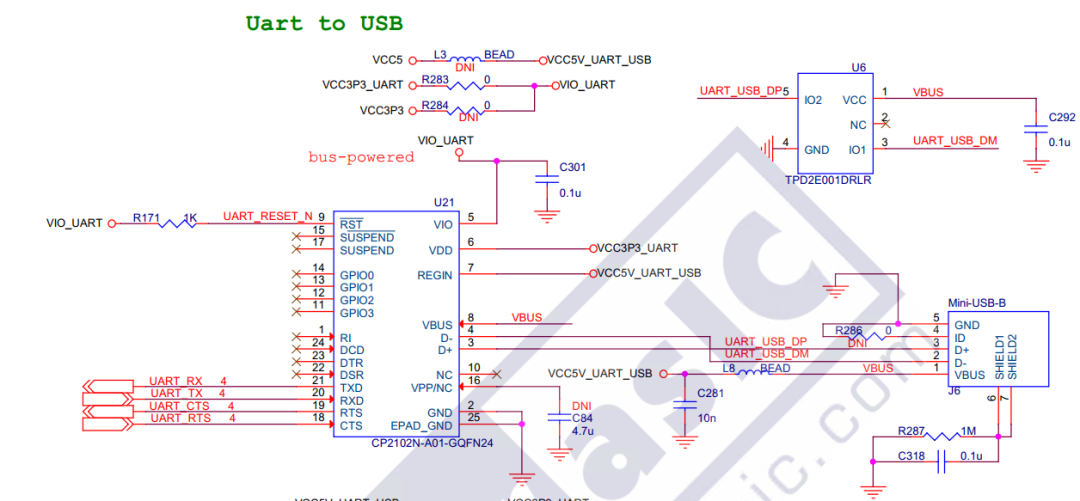

TSP的串口硬件电路图如下:

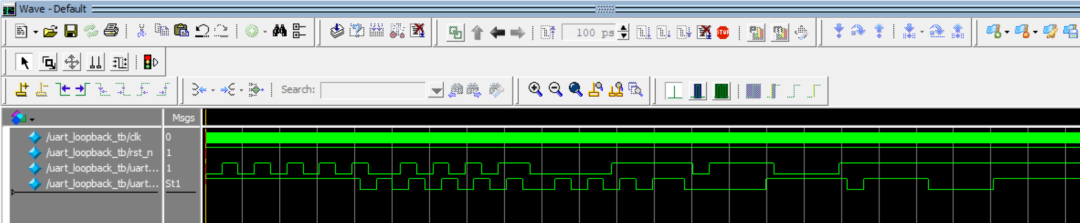

1 串口代码设计与功能仿真

代码设计思想参考2-基于FPGA开发板DE23-Lite的串口通信设计 (FT2232H),Quartus工程下载:参见本文末,本工程使用Quartus 17.1 Lite版本,仿真(仿真设置步骤请参考06-基于FPGA和LTC2308的数字电压表设计-ModelSim仿真与Matlab模拟信号产生)结果如下:

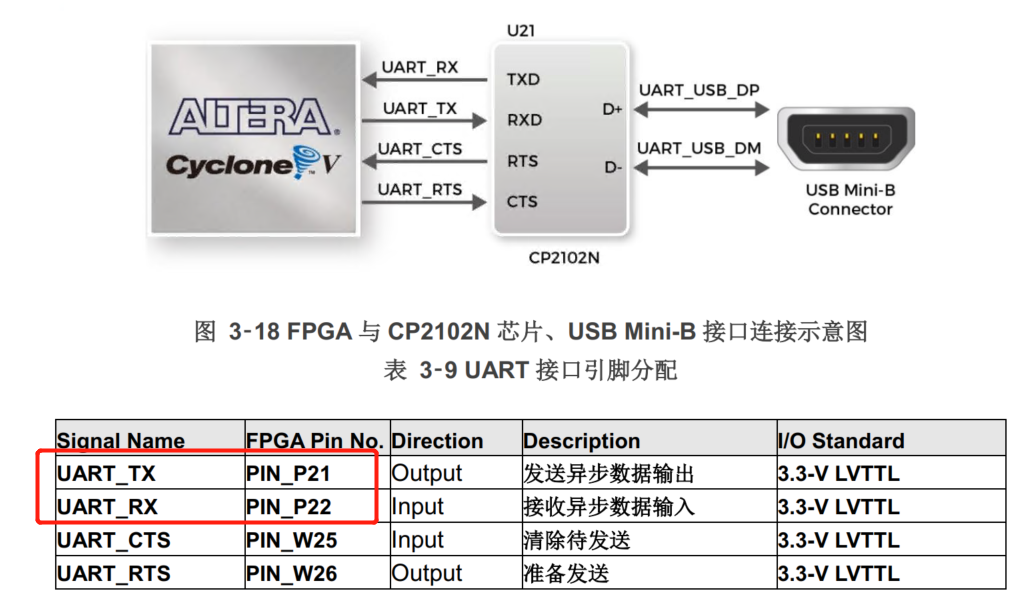

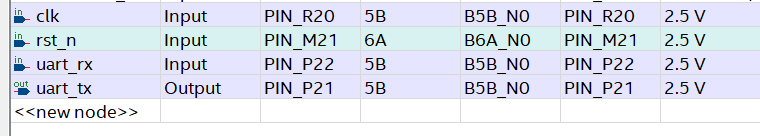

引脚分配如下:

1 串口设计下板验证

测试之前硬件连接如下:

-

连接串口J6 到PC;

-

用USB Blaster线缆连接开发板和PC;

-

连接12V电源到开发板;

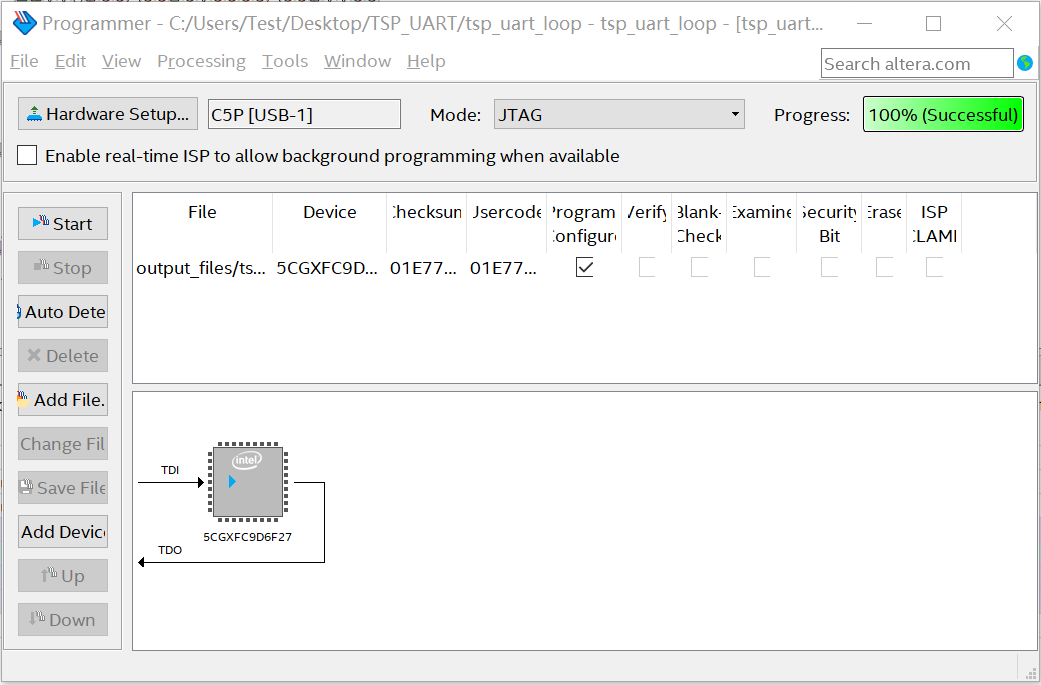

将sof配置文件下载到开发板:

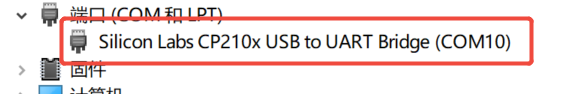

先从设备管理器里面找到当前串口的名称:

然后双击putty.exe打开串口调试工具:

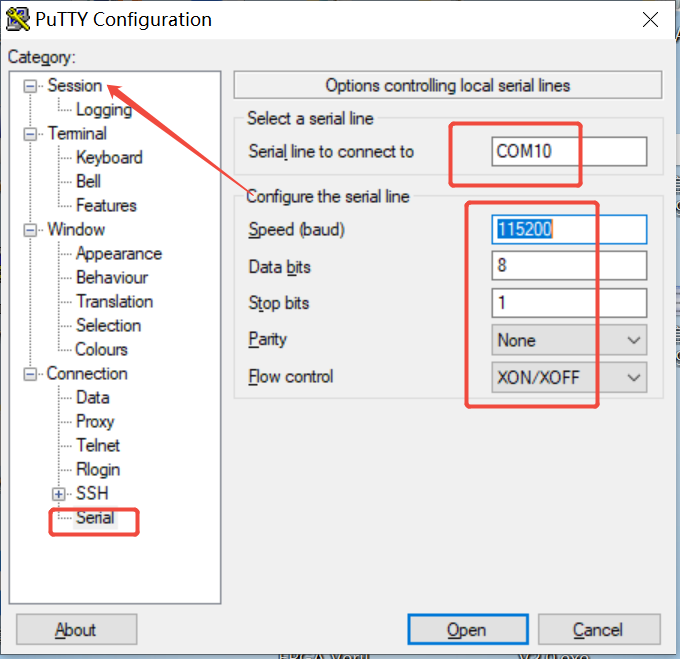

点击Serial设置串口为COM10,波特率设置为115200,停止位设置为1,然后点击Session:

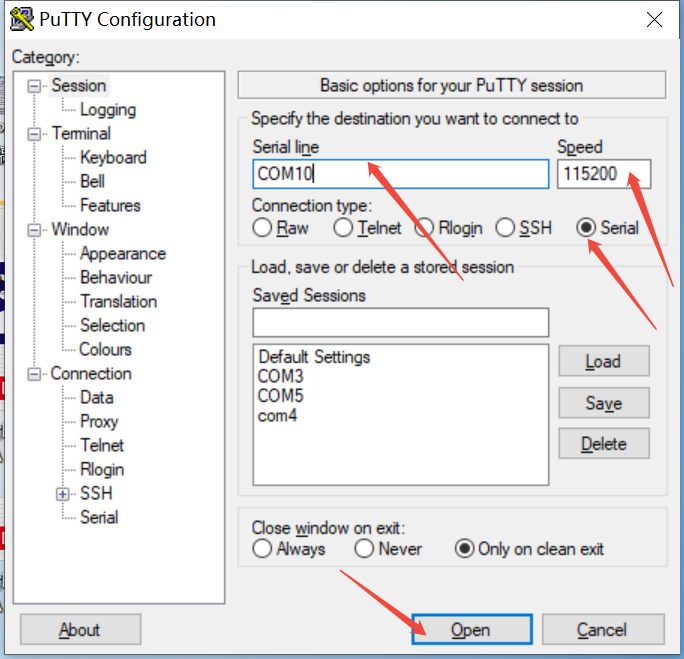

点击 Session以后出现如下界面,点击Open打开串口:

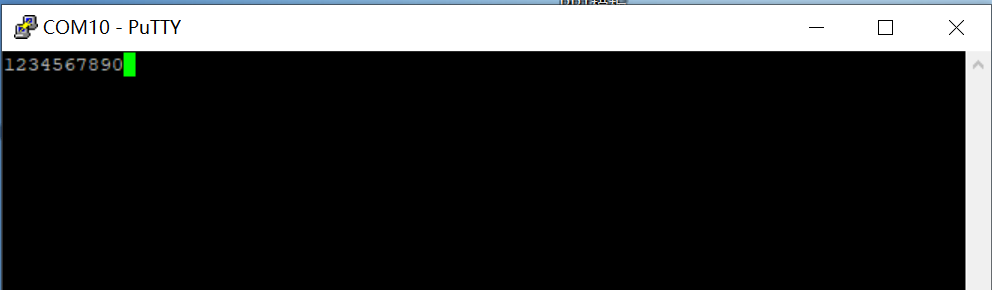

发送任意字符:

然后查看串口接收到的字符是否与之一致:

备注:

基于TSP(C5P/OSK)的例程下载地址:

通过网盘分享的文件:TSP_UART.rar

链接: https://pan.baidu.com/s/1iY0f5ef2YXWrHaXl_6q_xA 提取码: tera