module sinewave(sindata,clk,addm,cs);

input clk,cs;

input [4:0] addm;

output [7:0] sindata;

reg [7:0] sindata;

reg [7:0] sinrom [19:0];

initial

begin

sinrom[0]=8'd128;

sinrom[1]=8'd167;

sinrom[2]=8'd203;

sinrom[3]=8'd231;

sinrom[4]=8'd250;

sinrom[5]=8'd255;

sinrom[6]=8'd250;

sinrom[7]=8'd231;

sinrom[8]=8'd203;

sinrom[9]=8'd167;

sinrom[10]=8'd128;

sinrom[11]=8'd88;

sinrom[12]=8'd53;

sinrom[13]=8'd24;

sinrom[14]=8'd6;

sinrom[15]=8'd0;

sinrom[16]=8'd6;

sinrom[17]=8'd24;

sinrom[18]=8'd53;

sinrom[19]=8'd88;

end

always@(posedge clk)

if(cs)

sindata<=8'hzz;

else

sindata<=sinrom[addm];

endmodule

//测试平台送地址读出rom中数据

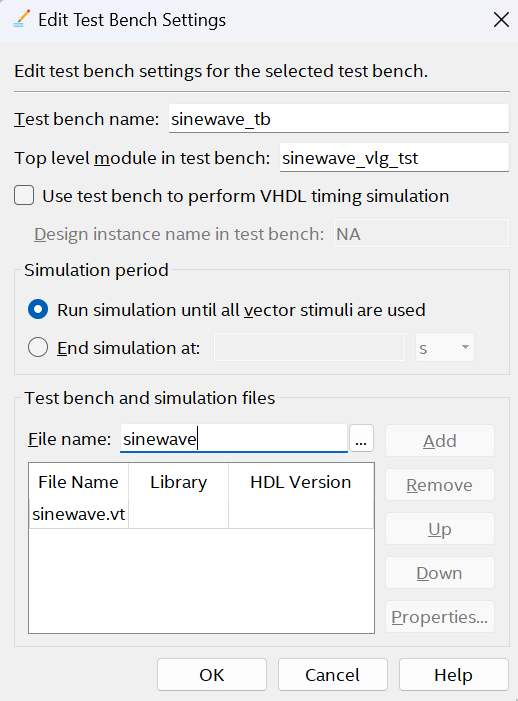

`timescale 1 ps/ 1 ps

module sinewave_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg [4:0] addm;

reg clk;

reg cs;

// wires

wire [7:0] sindata;

// assign statements (if any)

sinewave i1 (

// port map - connection between master ports and signals/registers

.addm(addm),

.clk(clk),

.cs(cs),

.sindata(sindata)

);

// 添加时钟生成

initial begin

clk = 1'b0;

forever #10000 clk = ~clk; // 10ns 周期 (对应 timescale 1ps)

end

initial begin

// 初始化

cs = 1'b1; // 片选无效

addm = 5'b0;

#20000; // 等待20ns

$display("========== 开始正弦波ROM测试 ==========");

$display("时间(ps) | 地址 | 数据");

$display("--------------------------");

// 使能片选并顺序读取所有地址

cs = 1'b0; // 片选有效

// 顺序读取地址0-19

addm = 5'd0; #20000; // 每个地址等待20ns

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd1; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd2; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd3; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd4; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd5; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd6; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd7; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd8; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd9; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd10; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd11; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd12; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd13; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd14; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd15; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd16; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd17; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd18; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

addm = 5'd19; #20000;

$display(" %t | %2d | %3d", $time, addm, sindata);

$display("========== 测试完成 ==========");

#50000;

$stop;

end

// 删除无用的 always 块(可选)

/*

always

begin

@eachvec; // 这个在大多数情况下不需要

end

*/

endmodule

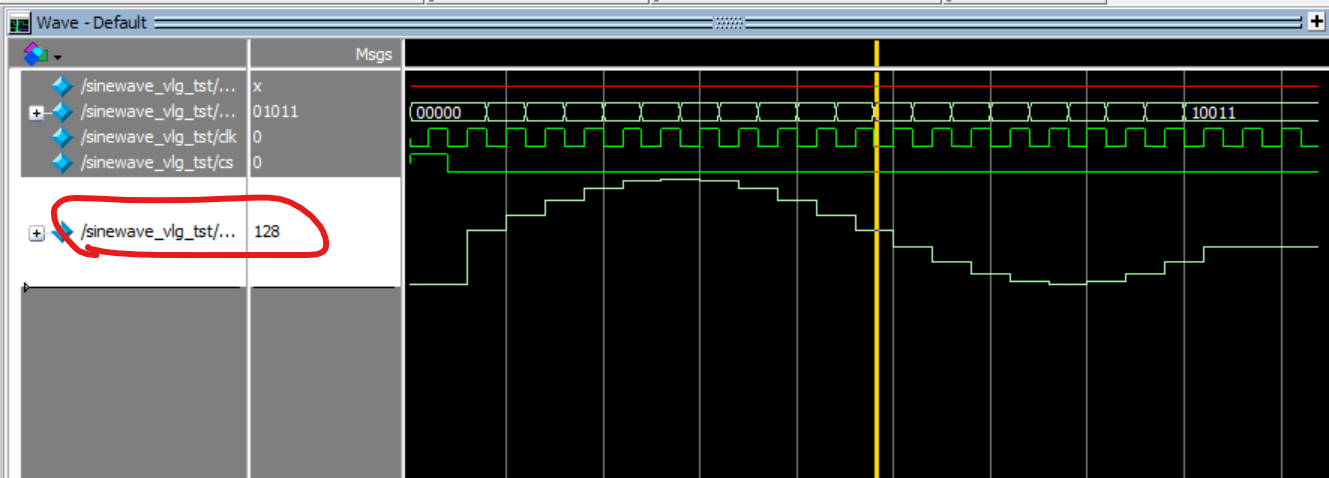

右键选中,radix选中unsigned,format选中analog

右键选中,radix选中unsigned,format选中analog