帧时钟:

ADC芯片的LVDS接口中的帧时钟FCLK,是一个低速的与数据相位对齐的时钟,一般FCLK与ADC的采样时钟相关;

上图是文档中提供的一个基本框架发现电路,用于寻找FCLK和数据在解串到并行输出的对齐时刻;

电路中,两个ISERDESE2组件在NETWORKING SDR模式下使用,使用比特时钟DCLK作为高速时钟驱动ISERDESE2,当DCLK对齐稳定之后,帧时钟的发现逻辑开始正常工作,图里是分别对帧时钟的两个差分信号进行解串操作;

将两个ISERDESE2的输出与我们预期的帧时钟模式的固定值进行比较,当ISERDESE2输出与这个固定值不同时,将对帧时钟和所有数据信号做bitslip操作,重复执行直到ISERDESE2输出与给定的帧时钟模式固定值匹配上,停止bitslip操作,此时一般认为FPGA中的帧时钟和数据有效了;

帧同步捕获:

帧时钟当做数据流被ISERDESE2捕获,其数据格式是恒定且重复的;

且由于帧时钟和数据是相位对齐的,帧时钟适合用作真实数据通道的训练模式或同步操作;

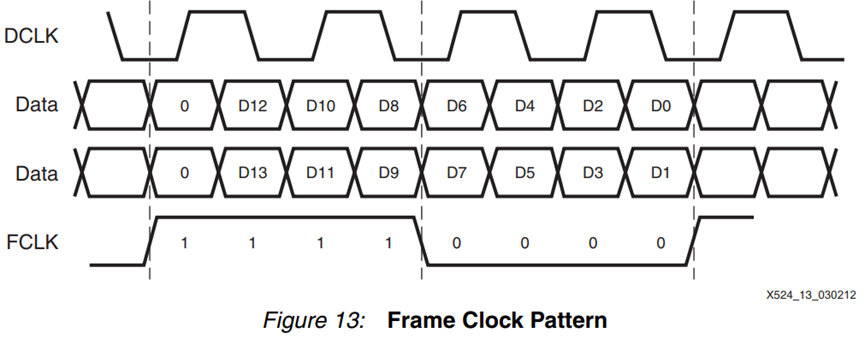

当ADC接口以2线模式运行时,帧模式如下图所示(16位,DDR,2线模式),当帧时钟对齐,一般数据通道也会受到正确数据:

可以看到,上图中,FCLK要检测的固定值,就是11110000这个序列,bitslip检测到该状态表示对齐;

Bitslip操作:

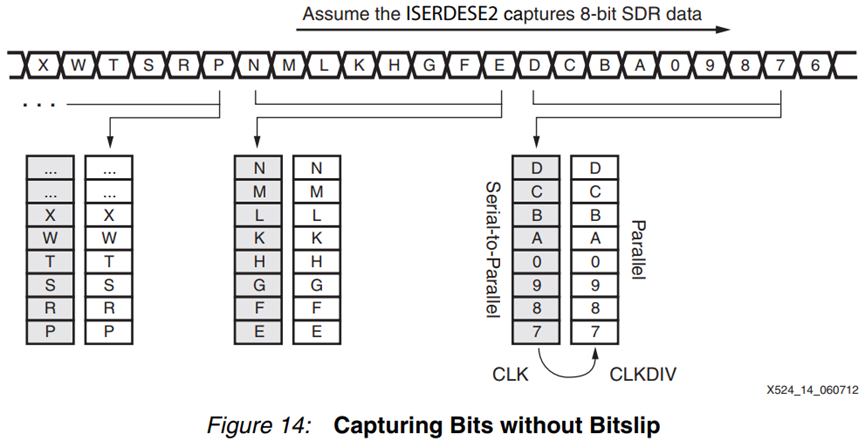

下图为在没有bitslip操作时捕获比特,当8个比特在捕获串转并放入并行寄存器从Q输出时,没有位移操作,无法控制解串出来的数据在原始比特流中的位置,获取不了正确的数据;

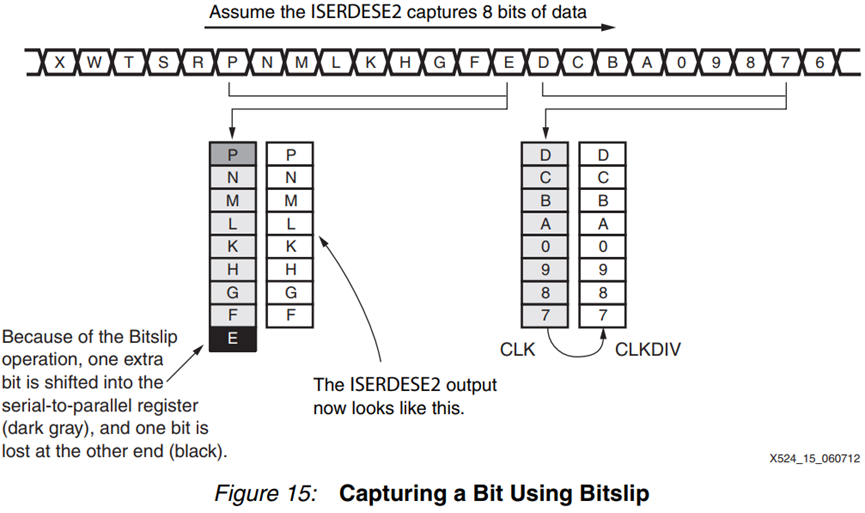

下图为带有bitslip的解串操作,可以看到,有了位移操作,在PNMLKHGFE这9个bit中,可以使用位移操作,取出PNMLKHGF这8个比特,在使用bitslip时,以CLK时钟频率捕获到的串行数据会晚一个CLK周期到达并行寄存器,因为此时要额外移入1个比特,同时要将另一端的1个比特丢弃,如下图中多移入一个P,将另一端的E丢弃;

该操作看起来像是数据被移位了一个比特;

数据通道:

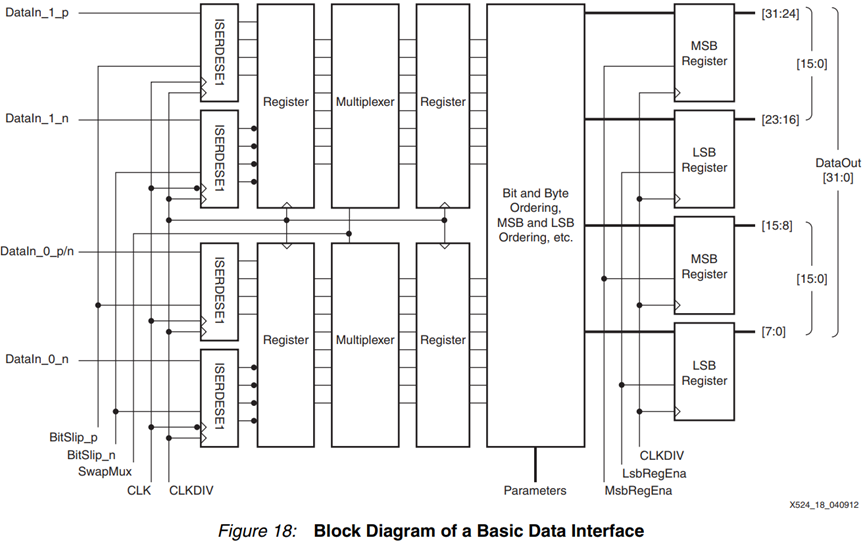

ADC可以用1线或2线提供数字数据,1线指使用单个差分LVDS对传输一个转换器的数据,2线指使用2个差分LVDS对传输一个转换器的数据;

转换器在通过1线或2线LVDS传输数据时,可以使用不同的位或字节组织,数据可以先发最高有效位MSB,先发最低有效位LSB,可以以位导向bitwise mode,字节导向bytewise mode,这些一般情况下,都可以通过ADC的低速SPI或其他接口进行模式的配置选择;

上图为一个2线模式,datain0组成一个32位的低16位,datain1组成32位的高16位;

数据的对齐是使用帧时钟进行对齐的,帧时钟被判定对齐,一般数据也会被对齐;

下一节将根据xapp524提供的思路,进行ad9253 lvsds接口的处理;

本文章由威三学社出品

对课程感兴趣可以私信联系