GMII是千兆以太网接口,它使用8位数据总线,在125MHz时钟下工作,每个时钟周期传输一个字节,因此数据速率是1000Mbps。GMII有独立的发送和接收数据线,还有相关的控制信号,比如TX_EN、RX_DV,以及错误信号等。GMII的时序应该是在时钟的上升沿采样数据,控制信号如TX_EN。也需要在时钟边沿有效。

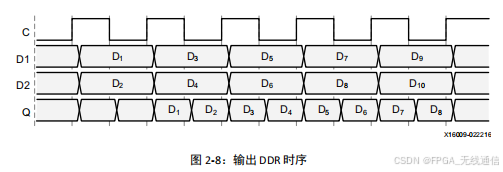

RGMII,它为了减少引脚数量,将数据总线从8位减少到4位,同时使用双倍数据速率(DDR),在时钟的上升沿和下降沿都传输数据。因此,RGMII的工作时钟是125MHz,但因为DDR,每个时钟周期传

输两个半字节(4位),所以总的数据速率也是1000Mbps。

GMII到RGMII的转换器需要将8位的数据在125MHz下转换为4位的数据在双沿传输,同时将TX_EN和TX_ERR编码到TX_CTL的两个边沿。

RGMII到GMII需要将双沿的4位数据组合成8位,并在每个时钟周期输出,同时从TX_CTL中提取控制信号。

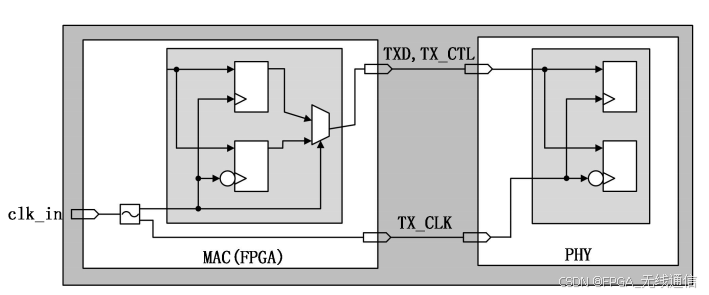

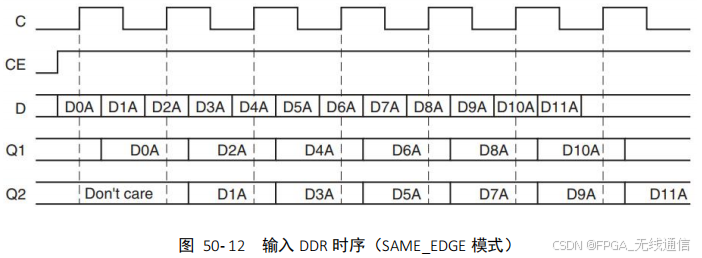

FPGA内部处理的数据都是单沿数据,双沿数据的变换只能发生在FPGA的IOB上面;

RGMII TX : FPGA(cpri) -> ARM

RGMII RX : ARM -> FPGA(cpri)

GMII > RGMII : GMII_TXD[7:0] = {RGMII_TXD下降沿,RGMII_TXD上升沿};

RGMII > GMII : GMII_RXD[7:0] = {RGMII_RXD下降沿,RGMII_RXD上升沿};

RGMII_RXD[3:0]上升沿传输,RGMII_RXD[7:4]下降沿传输;

IDELAYE3(输入信号延迟模块,作用是将信号延迟一段时间)

ODELAYE3(输出信号延迟模块)

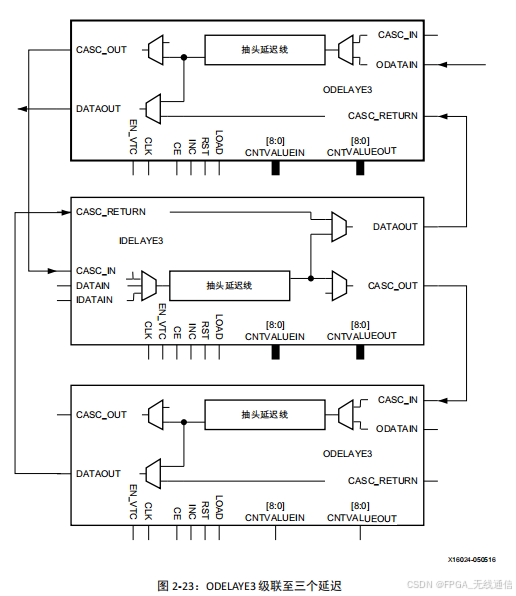

因单个IDELAYE3或者ODELAYE3有固定的延迟,如果所需要的延迟超过固定延迟,则需要进行级联;

上图中可以看到,IDELAYE3的级联操作需要ODELAYE3一起穿插使用,第一级CASCADE参数设置为MASTER,中间级设置为SLAVE_MIDDLE,最后一级设置为SLAVE_END,级联组件之间的布线是专用高速布线,IDELAYE3 或 ODELAYE3 级联的固定内部插入延迟总量是初始插入延迟与级联插入延迟的总和。此延迟按 IDELAYE3 和 ODELAYE3 级联次数而成倍增加。

在TIME模式下级联时,同一site下两者延迟要相同,如把IDELAYE3延时0.75ns,级联的ODELAYE3延时0.75ns,那么就延时了1.5ns,在FIXED模式下DELAY_VALUE设置两者相同,VAR_LOAD模式下两者CNTVALUEIN输入相同值;

IDELAYCTRL(辅助模块,使用了IDELAY或者ODELAY就必须使用该模块)

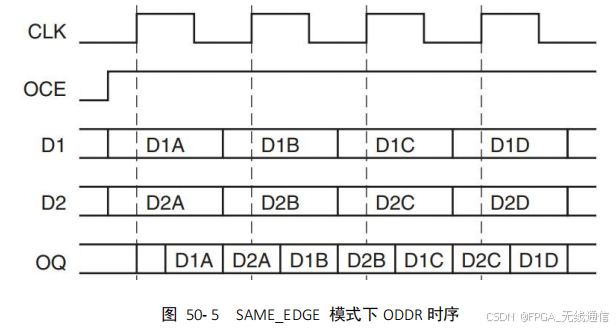

IDDRE1(输入信号为单沿,输出信号为双沿)

ODDRE1(输入为双沿信号,输出为单沿信号)

RGMII发送设计逻辑框图

PHY通过RGMII发送至FPGA(FPGA只处理单沿数据)

源语:ODDR;双输入单输出

支持RGMII的PHY芯片在时钟上升沿发送数据低4位,时钟下降沿发送数据高4位;

PHY通过RGMII接收FPGA的数据

源语:IDDR;单输入双输出

对时钟或数据信号进行延时使用以下源语(适用于U+系列):

IDELAYCTRL、ODELAYE3、IDELAYE3

如果使用了IDELAYE3或ODELAYE3的TIME模式,就必须例化IDELAYCTRL组件,如果使用

COUNT模式,就不使用IDELAYCTRL组件;

REFCLK:参考时钟,使用时参考时钟与其联合使用的IDELAYE3和ODELAYE3设置相同值;