为什么RRU需要如此精确的同步。

-

TDD(时分双工)系统:

-

在TDD系统中,上行(手机到基站)和下行(基站到手机)使用相同的频率,但在不同的时间片段(时隙)进行传输。

-

如果同一个网络内不同基站的RRU时间不同步,会导致一个基站正在发射(下行)时,另一个相邻的基站正在接收(上行)。这将造成强烈的基站间干扰,使上行链路几乎无法工作。

-

-

协同技术:

- 现代通信(4G/5G)的高级功能,如载波聚合、CoMP 和MIMO,特别是涉及多个RRU协同为一个用户服务的场景,都要求这些RRU在时间上保持微秒级甚至纳秒级的同步。如果不同步,协同发射的信号无法在手机端正确合并,反而会相互干扰。

-

定时与相位同步:

- 最先进的5G Massive MIMO和毫米波技术甚至要求相位同步。这意味着多个RRU/天线之间不仅要知道"什么时候"开始发送,还要保持射频载波相位的一致性。这是实现波束赋形等关键技术的基础。

IEEE 1588 ,又称为PTP 1588

-

目标 :在分组网络(如以太网)上,为分布式设备提供高精度的时间同步。

-

精度 :理想情况下可以达到亚微秒级的同步精度,远高于传统的NTP(网络时间协议,精度在毫秒级)。

-

核心思想 :通过在主时钟和从时钟之间交换特定的报文,来测量和补偿网络中的传输延迟,从而校准从时钟的时间。

Altera 1588系统解决方案的不同时钟模式的工作原理,包括普通时钟(Ordinary Clock, OC)、边界时钟(Boundary Clock, BC)和透明时钟(Transparent Clock, TC)模式下的操作流程。

在普通时钟模式中,系统包括一个OC主时钟和一个或多个OC从时钟。主时钟会发送同步包,从时钟会回应延迟请求和延迟响应包。此过程中,主从时钟之间通过网络交换时间戳(T1至T4),从而允许从时钟计算出路径延迟,并据此调整自身的时间基准。 对于边界时钟模式,器件具有一个或多个主端口和至少一个从端口。边界时钟的工作方式与普通时钟类似,在接收同步消息、发送延迟请求和接收延迟响应的过程中,从端口能够收集时间戳,计算路径延迟和偏移量以校正其本地时钟。同时,作为主端口,它也会向下游设备发送同步和延迟响应消息。 透明时钟模式则是用于测量网络中的延时,它不会影响通过它的同步消息,而是记录时间戳来帮助计算路径延迟。 通过这些时钟模式,PTP(精密时间协议)网络能够实现高精度的时间同步。

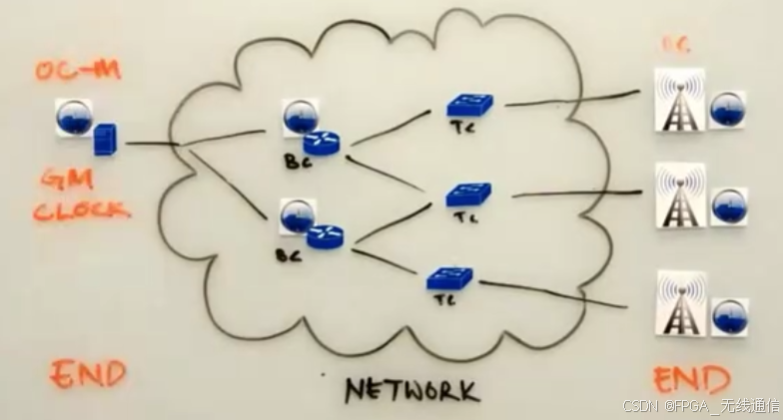

下图为由一些终端设备和网络设备(如交换机和路由器)组成的计算机网络,由于这是一个PTP网络,所以有一个PTP主时钟,一些器件将拥有自己的时钟,最终应该与主时钟同步。

带有时钟的器件,被识别为普通时钟OC;

带有时钟的网络设备,被识别为边界时钟BC;

测量时延的网络设备是透明时钟 TC;

普通时钟可以是主时钟 OC-M 或从时钟;

首先,OC主机的CPU将发送一个同步包,接下来包解析器将解码包并提取指纹。然后数据包解析器将发送数据包和指纹到MAC,以生成时间戳T1,然后通过物理层发送数据包。

在OC从属端口上,MAC将接收数据包并生成时间戳T2,数据包解析器将提取指纹,并将时间戳T2和指纹返回到FIFO,以供CPU收集;同步包被转发到CPU,以限制同步包中的时间戳T1;CPU还将读取FIFO以收集时间戳T2;

接下来,OC从CPU将发送延迟请求包,包解析器将解码包,提取指纹并将其发送到MAC。MAC将在接收延迟请求包后生成时间戳T3,并将时间戳和指纹返回给FIFO。同时,OC从CPU将读取FIFO以收集时间戳T3;延迟请求包随后通过物理层发送到网络。

OC主端口上的MAC接收延迟请求并生成时间戳T4,数据包解析器检索指纹并将时间戳和指纹返回给FIFO。延迟请求包被转发到CPU,然后CPU读取FIFO以收集时间戳T4,

接下来,OC主CPU将发送一个延迟响应包,其中包含时间戳T4,数据包解析器对数据包进行解码,并请求MAC不要为该数据包生成时间戳。MAC然后按原样发送延迟响应包。

OC从机拉起将接收数据包,并为其添加时间戳。

CPU读取了FIFO中生成的时间戳,但没有使用;

OC从CPU接收延迟响应包,并从包中收集时间戳T4。

现在,OC从站的CPU拥有所有时间戳T1、T2、T3、T4,可以计算中间路径延迟,从而更新模块的从站时间;

边界时钟模式的功能流程:

边界时钟是一个网络器件,它有一个从端口和一个或多个主端口;所有端口的时间D模块应该同步;

BC从端口同步类似于OC从同步,在接收同步、发送延迟请求和接收延迟响应的整个过程中,BC从站能够收集所有四个时间戳,并计算平均路径延迟和偏移,以校正其系统时钟;

针对1588v2在RRU中的应用:

第一步:偏移量测量

-

主时钟(通常是BBU或专门的时钟源)向从时钟发送一个

Sync消息,并记录精确的发送时间 t1。 -

由于

Sync消息本身无法携带足够精确的 t1 时间戳(因为硬件时间戳发生在MAC层),主时钟会紧接着发送一个Follow_Up消息,此消息中携带了 t1 的精确值。 -

RRU收到

Sync消息,记录精确的到达时间 t2。

至此,RRU知道了:

t2 = t1 + Offset + Delay

-

Offset:主从时钟之间的时间偏移(就是我们要求解的量)。 -

Delay:网络传输延迟(假设路径对称,上行和下行的Delay相等)。

第二步:传输延迟测量

-

从时钟 向 主时钟 发送一个

Delay_Req消息,并记录精确的发送时间 t3。 -

主时钟收到

Delay_Req消息,记录精确的到达时间 t4。 -

主时钟发送一个

Delay_Resp消息给从时钟,此消息中携带了 t4 的精确值。

至此,主时钟端有:

t4 = t3 - Offset + Delay

第三步:计算与校准

现在,RRU拥有了四个关键时间戳:t1, t2, t3, t4。它可以解出两个方程:

-

计算传输延迟:

Delay = [(t2 - t1) + (t4 - t3)] / 2 -

计算时钟偏移:

Offset = [(t2 - t1) - (t4 - t3)] / 2

一旦RRU计算出 Offset,它就可以调整自己的本地时钟,将其减去这个偏移量,从而与主时钟实现同步。