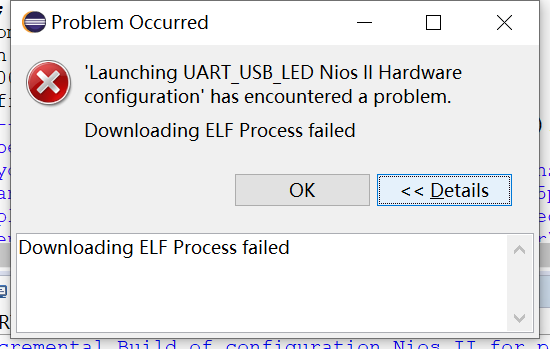

当你用的Quartus工具是Lite版本(免费版),且FPGA工程里面包含一些需要license的IP时,编译工程会生成带有 time-imited的文件(软件提示的原文是:one or more time-imited megafunctions that support the OpenCore Plus feature that will not work after the hardware evaluation time expires)),这种文件可以下载到FPGA进行测试验证,但Nios II 工程的elf文件却没法下载了 。提示:

如下有两种方法可以临时解决带Nios II的FPGA设计在测试时遇到time_limited文件导致elf下载不了的问题。

方法一 直接使用Programmer 和Eclipse 下载sof和elf

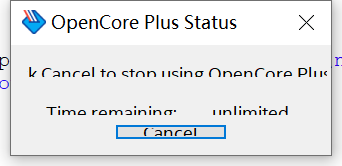

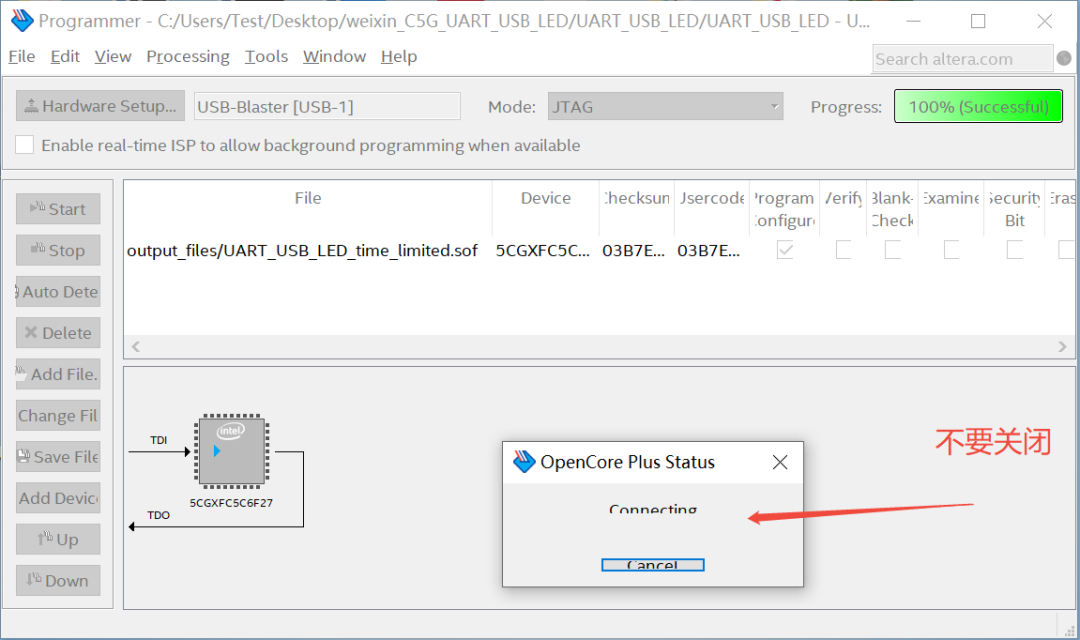

- 先用Programmer将带time_limited的sof文件下载到FPGA,此时会跳出一个OpenCore Plus Status窗口,保持这个窗口不关闭。

- 接下来对Eclipes工程点击Run As------ Nios II hardware 就OK了。

方法二 将elf文件转为hex文件加载到on chip memory IP中,直接通过Programmer下载

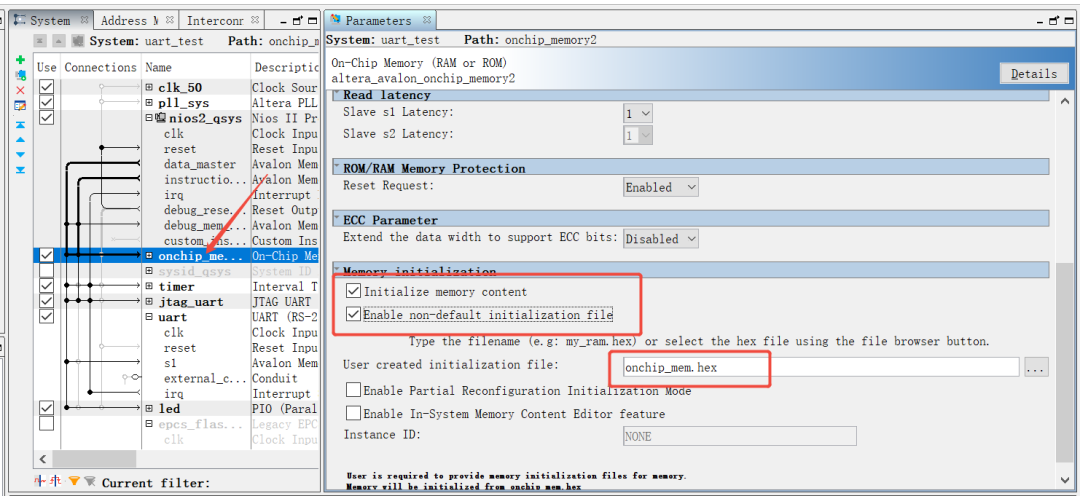

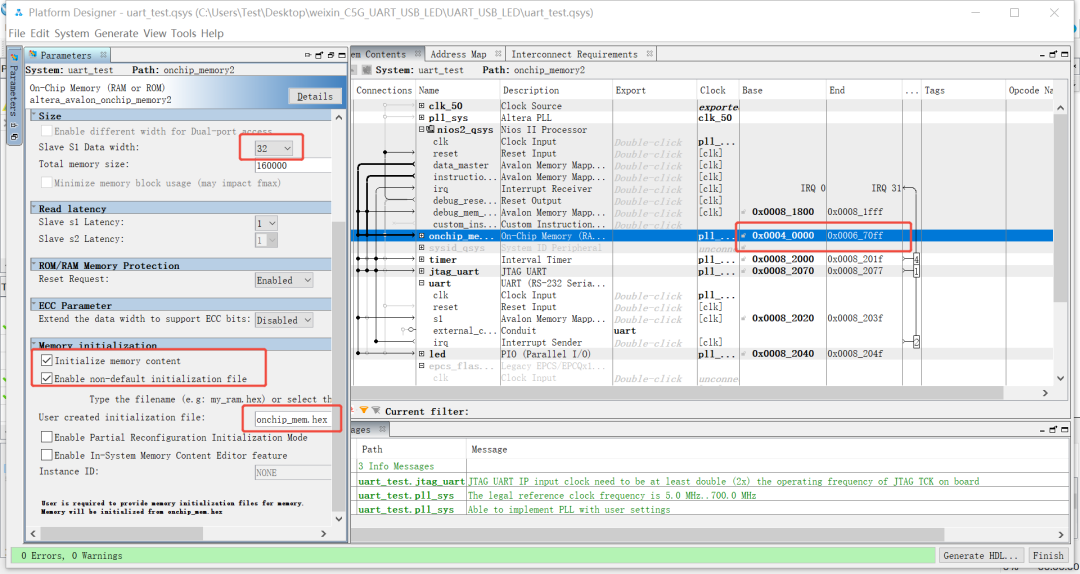

在qsys系统中,编辑on chip memory IP,勾选lnitialize memory content和Enable non-default initialization file,并在初始化文件处填入hex文件名:

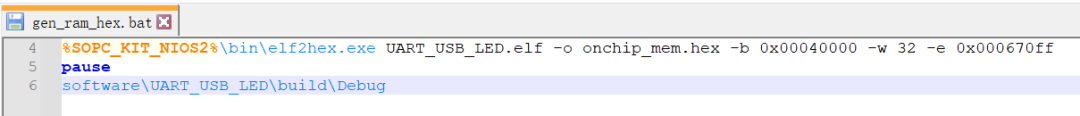

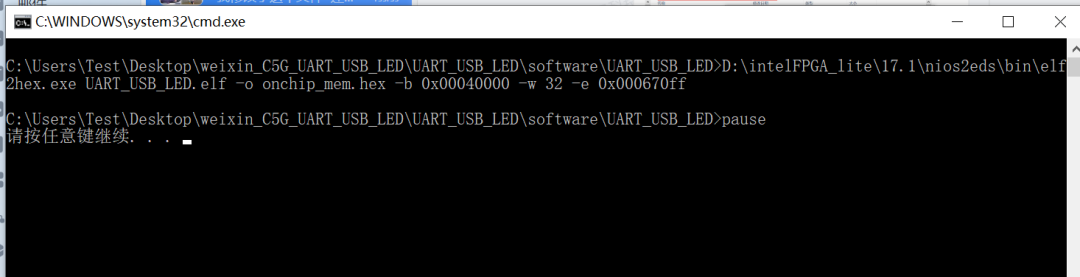

接着将Qsys系统generate生成sopcinfo文件,在Eclipse里面更新bsp,然后Build Project生成elf文件,把该elf文件转换为前面在qsys中填入的hex文件,可以使用batch文件(本文测试环境是Quartus 17.1 Lite 版本)进行转换:

i.elf文件:填入编译生成的elf文件名;

ii.-o onchip_ram.hex:指定生成的hex文件名,需要与qsys中填入的文件名一致;

iii.-b 0x00040000、-e 0xxx670ff: 是on chip memory的Base地址以及End地址;

iv.-w 32: 是S1 Data width;

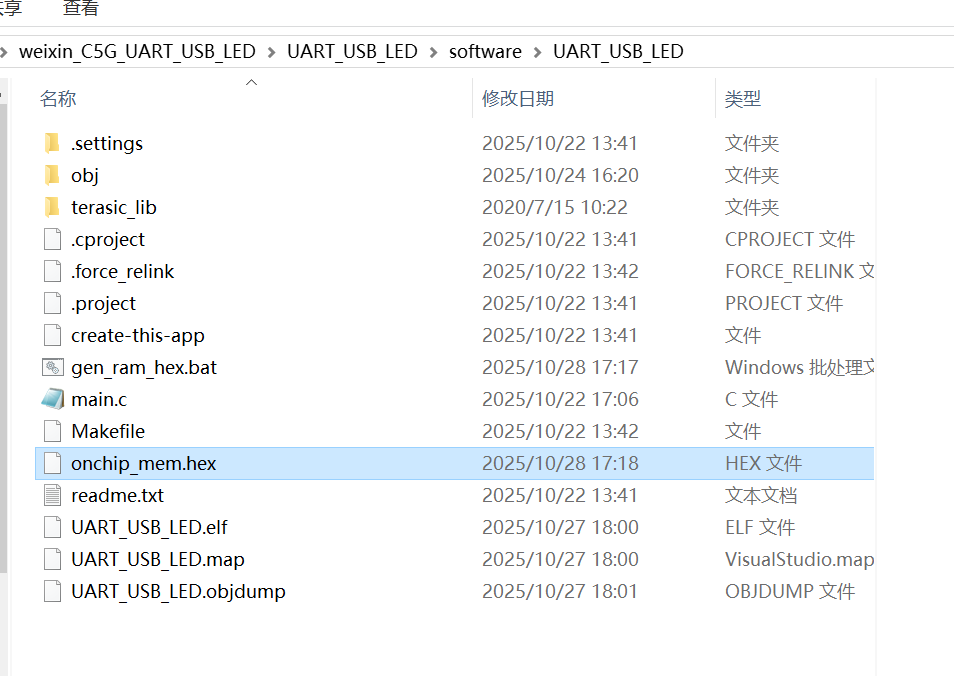

修改完成后,将batch文件放置在elf文件所在路径下,并运行gen_ram_hex.bat,此时会生成对应的hex文件:

把hex文件复制到Quartus工程路径:

再编译Quartus工程,此时编译生成的time limited sof中,已经包含了elf,直接下载sof文件,下载成功后保持Open Core Plus Status窗口不关,能正常观察到现象:

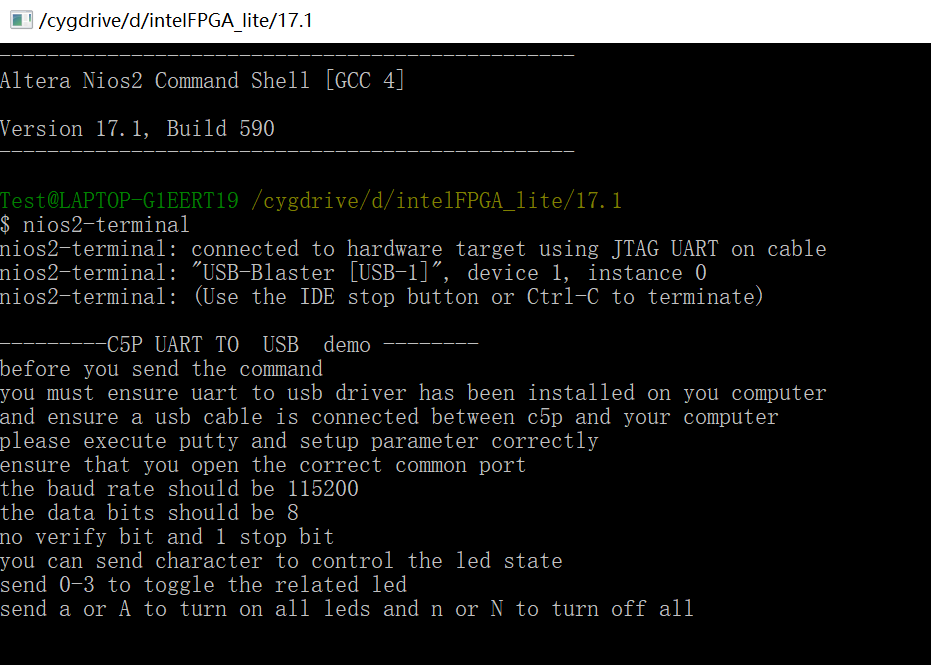

如需观测JTAG UART消息打印输出,则需运行Nios II Command Shell,并执行nios2-terminal命令:

总结: 这两种方法都是临时解决测试带Nios II的FPGA设计遇到time_limited文件时的办法。第一种办法简单,第二种办法虽然复杂点,但是后面每次下载文件时可不打开Eclipse,只需要Programmer就可以了,大家可以根据需要自行选择。