FPGA教程系列-番外篇Model Composer之滤波器优化设计仿真

在 FPGA 中创建优化设计

FPGA 设备的时钟频率可轻松超过 20 MHz。以更高的时钟频率运行 FPGA,可让 Vitis Model Composer 使用相同的硬件资源计算多个中间结果。

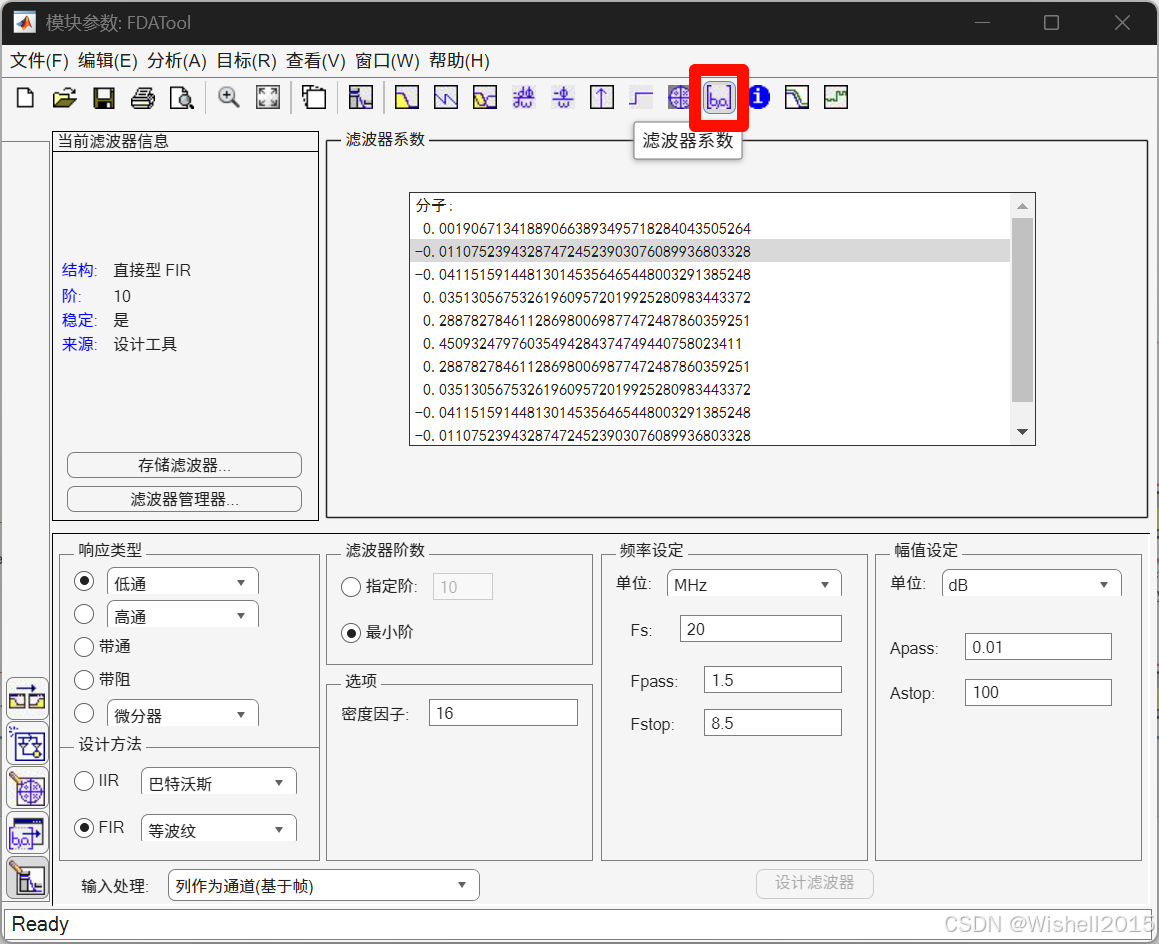

双击 FDATool 实例,打开属性编辑器。点击 "滤波系数 "按钮 查看滤波系数

这表明滤波器使用了 11 个对称系数。这至少需要六次乘法运算。这正是上一节末尾所显示的,最终硬件使用了 6 个 DSP48 元件。DSP48 是用于执行乘法运算的 FPGA 资源。

目前的设计以 20 MHz 的频率对输入进行采样。如果以当前频率的 6 倍对输入进行采样,就可以使用一个乘法器进行所有计算。

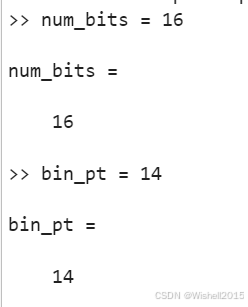

定义工作区 变量

在 MATLAB 命令窗口中输入:num_bits = 16;bin_pt = 14;

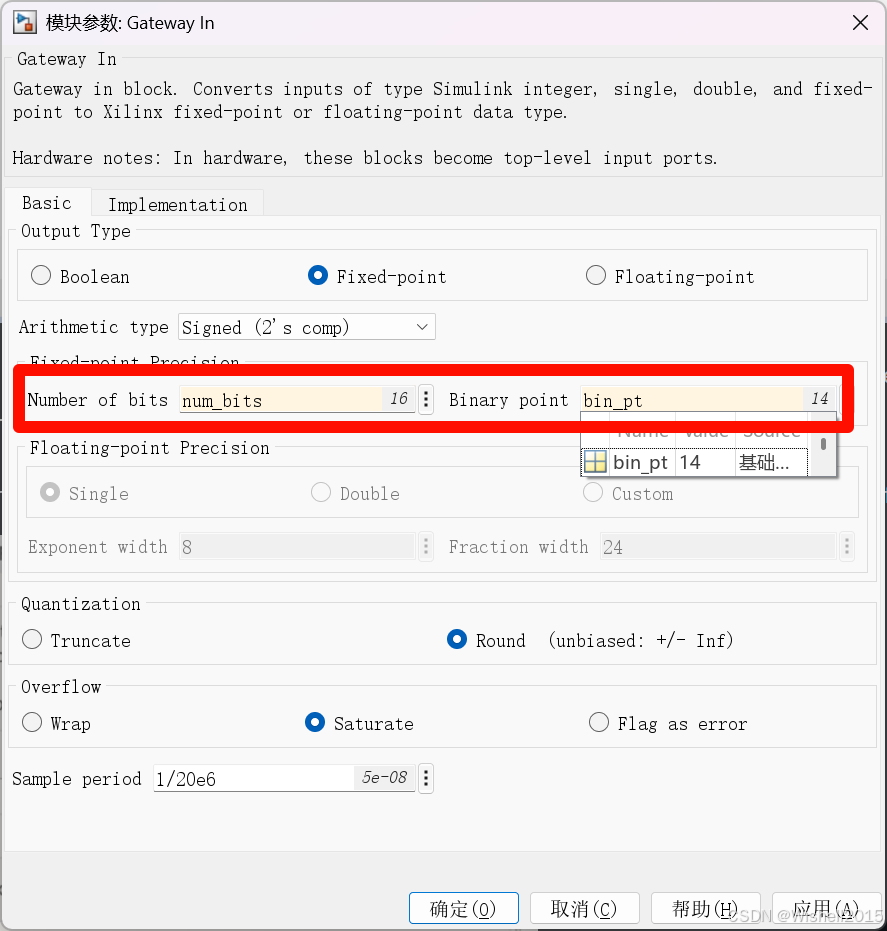

在 设计中,双击 HDL_filter 子系统,然后双击 Gateway In 块打开属性编辑器。更换变量:

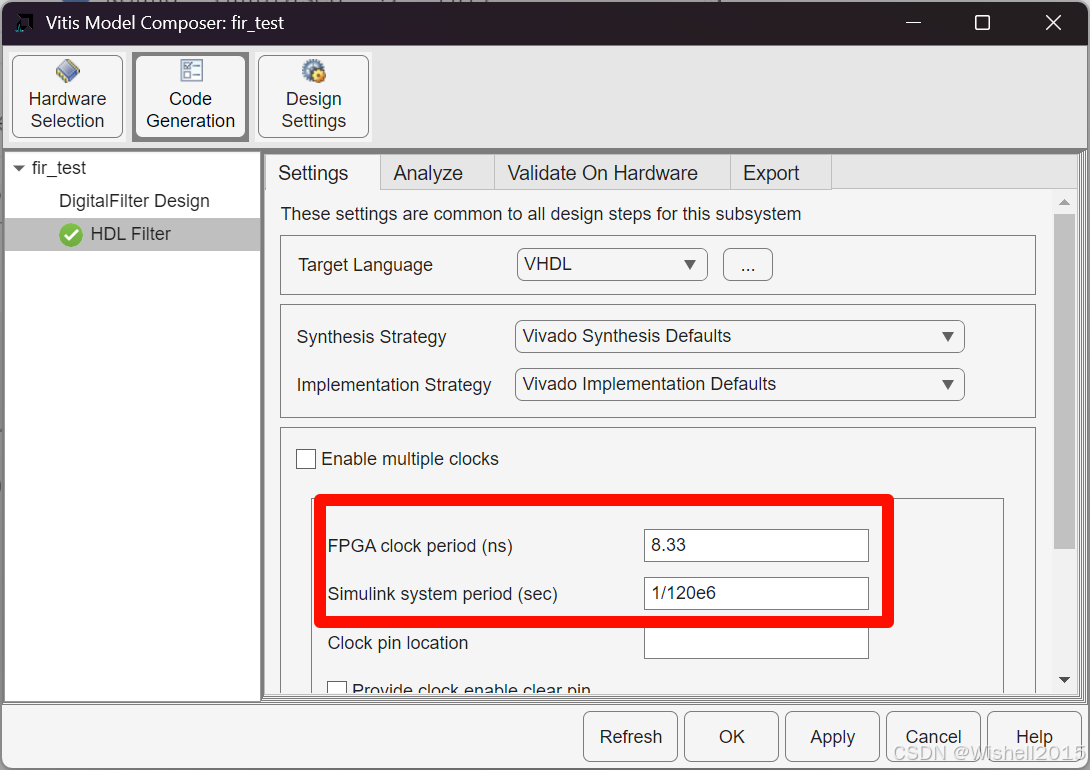

在 Vitis Model Composer Hub 中,将采样频率更新为 120 MHz (6 * 20 MHz):

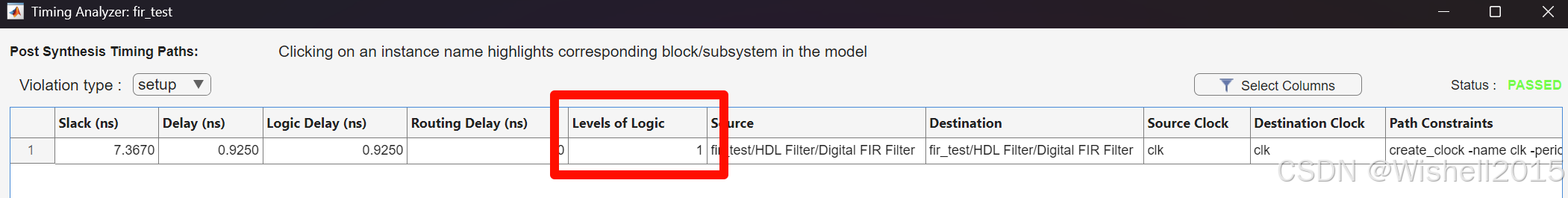

单击 "分析 "将设计编译成硬件描述。

现在,硬件设计只使用了一个 DSP48 资源(一个乘法器),与配置 HDL 块部分末尾的结果相比,使用的资源明显减少。