太久没写了,记录...

异步时钟单脉冲在快时钟域至慢时钟域的传输

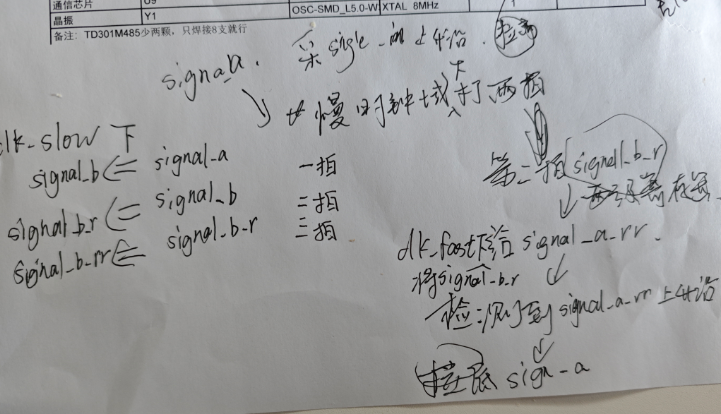

流程:

top:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/12/02 10:48:54

// Design Name:

// Module Name: single_pulse

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module single_pulse(

input clk_fast,

input rst_n,

input clk_slow,

input pulse_in,

output pulse_out

);

reg signal_a;

reg signal_a_r;

reg signal_a_rr; //展宽结束信号

reg signal_b;

reg signal_b_r;

reg signal_b_rr;

always@(posedge clk_fast or negedge rst_n)begin //fast clk用于时钟同步

if(!rst_n)begin

signal_a <= 1'b0;

end else if(pulse_in == 1'b1)

signal_a <= 1'b1;

else if(signal_a_rr == 1'b1)

signal_a <= 1'b0;

else

signal_a <= signal_a;

end

always@(posedge clk_slow or negedge rst_n)begin //slow clk打两拍

if(!rst_n)

{signal_b_rr,signal_b_r,signal_b} <= {3{1'b0}};

else

{signal_b_rr,signal_b_r,signal_b} <= {signal_b_r,signal_b,signal_a};

end

always@(posedge clk_fast or negedge rst_n)begin

if(!rst_n)

{signal_a_rr,signal_a_r} <= {2{1'b0}};

else

{signal_a_rr,signal_a_r} <= {signal_a_r,signal_b_r};

end

assign pulse_out = (~signal_b_rr) & signal_b_r;

endmoduletb:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/12/02 14:56:47

// Design Name:

// Module Name: tb_single_pulse

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tb_single_pulse;

reg rst_n;

reg clk_fast;

reg clk_slow;

reg pulse_in;

wire pulse_out;

single_pulse u1

(

.rst_n (rst_n ),

.clk_fast (clk_fast ),

.clk_slow (clk_slow ),

.pulse_in (pulse_in ),

.pulse_out(pulse_out)

);

initial

begin

clk_fast = 1;

clk_slow = 0;

rst_n = 0;

pulse_in = 0;

repeat(5)@(posedge clk_slow);

rst_n = 1;

repeat(5)@(posedge clk_fast);

pulse_gen();

end

task pulse_gen;

begin

pulse_in <= 1;

@(posedge clk_fast);

pulse_in <= 0;

end

endtask

always #10 clk_slow = ~clk_slow;

always #5 clk_fast = ~clk_fast;

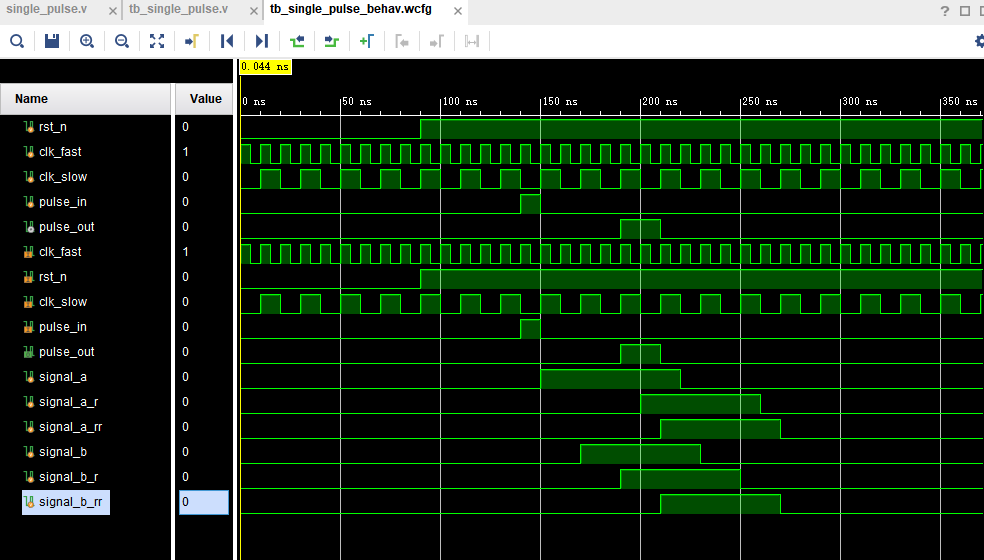

endmodule仿真:signal_a_rr用于控制展宽结束信号,

将输入信号脉冲展宽再同步的方法,通常展宽>2个慢时钟周期,保证慢时钟域至少能采到一次,再把慢时钟域同步打两拍,再通过边沿检测把"宽电平"还原成单脉冲

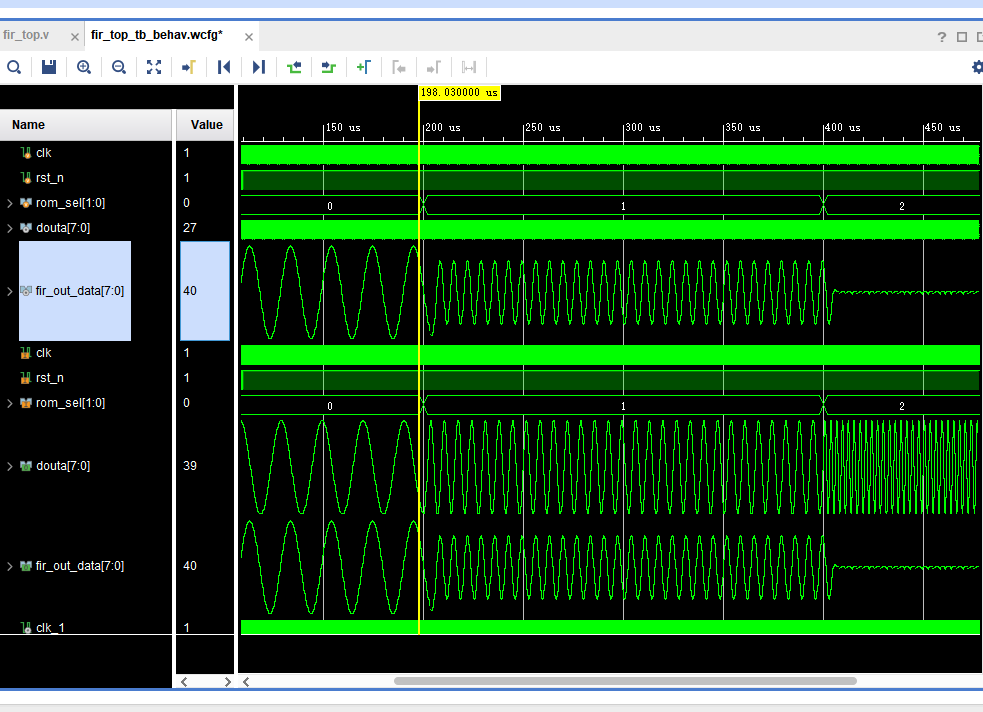

记另一个低通滤波器的仿真:低通滤波器额定采样为10MHz,通过分配不同的ROM读取时钟频率控制ROM的读取速度

低通滤波器设置300MHz的截止频率,第三段350MHz时几乎被全部滤掉了,原因是高频正弦被严重欠采样后混叠成低频,FIR 低通又把混叠高频分量砍掉" 造成的幅度衰减。

时钟越快,正弦频率越高 → 混叠后高频分量离通带越远 → FIR 把它们砍得越多 → 留下来的有效幅度越小,波峰就越来越低