50天精通FPGA设计-总体规划-CSDN博客

目录

简介

本章系统地讲述了数字电路的基本逻释单元---门电路。由于门电路中的二极管和三极管经常工作在开关状态,所以首先介绍了它们在开关状态下的工作特性。然后,重点讨论了目前广泛使用的TTL门电路和CMOS门电路。对于每一种门电路,除了讲解它们的工作原理和逻辑功能以外,还着重介绍了它们作为电子器件的电气特性,特别是输入特性和输出特性,以便为实际使用这些器件打下必要的基础。

半导体二极管和三极管的开关特性

半导体二极管的开关特性

- 静态开关特性(稳态)

- 导通状态

:正向偏置电压大于门槛电压(硅管约0.7V)后,二极管导通。此时表现为一个很小的电阻和一个基本恒定的正向压降 V_F。

- 截止状态

:反向偏置时,理想情况应无电流。但实际上存在微小的反向饱和电流 I_S(漏电流),且反向电压不能超过击穿电压 V_BR。

- 应用

:利用其单向导电性,可作为简单的电子开关,用于整流、钳位、隔离等。

- 动态开关特性(瞬态)--- 关键所在

二极管从开到关,或从关到开,都需要时间。最关键、最影响速度的是 从导通到截止的切换过程。

反向恢复过程:

当二极管正向导通时,PN结两侧充满了少数载流子(称为"存储电荷")。突然加上反向电压时,这些存储电荷不会立刻消失,它们会先形成一股很大的反向电流 I_R,待存储电荷被"抽空"或复合掉之后,二极管才能完全进入截止状态。

三极管的开关特性

三极管通常工作在截止区(关)和饱和区(开),放大区只是快速经过的过渡状态。

- 静态开关特性(稳态)

- 截止状态

:发射结零偏或反偏,集电结反偏。I_B ≈ 0, I_C ≈ 0, V_CE ≈ V_CC(电源电压)。相当于开关断开。

- 饱和状态

:发射结正偏,集电结也正偏。I_B 足够大,使得 I_C 达到最大值且不再随 I_B 增大而增加。此时:

-

- I_C = V_CC / R_C

(由外电路决定)

-

- 饱和压降

V_CE(sat) 很小(硅管约0.1-0.3V),相当于开关闭合。

-

- 临界饱和条件

:I_B ≥ I_C / β。为确保深度饱和,通常取 I_B = (2~5) * (I_C / β)。

- 动态开关特性(瞬态)

三极管的状态切换需要时间,因为结电容需要充放电,基区存储电荷需要建立和消散。

最基本的逻辑门,与或非

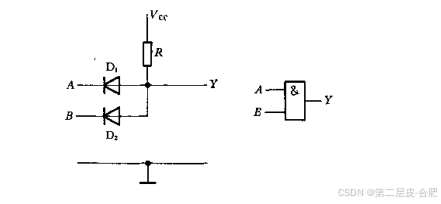

用二极管搭建的与门

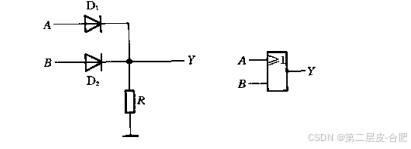

用二极管搭建的或门

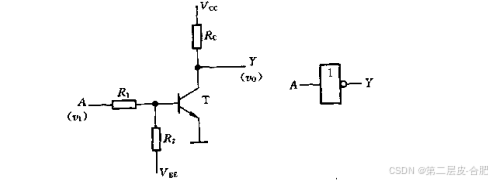

用三级管搭建的非门

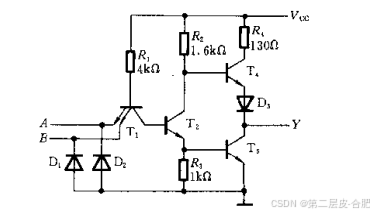

TTL门电路

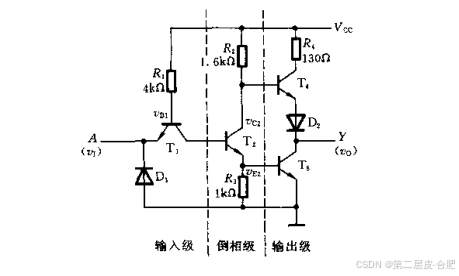

TTL反相器的电路结构和工作原理

设电源电压Vcc=5V,输入信号的高、低电平分别为Va=3.4V,V.=0.2V。PN结的伏安特性可以用折线化的等效电路代替,并认为开启电压Von为0.7V

由图可见,当 =V.时,,发射结必然导通,导通后 ,的基极电位被钳在0.9V。因此的发射结不会导通。由于的集电极回路电阻是 R。和的b一c结反向电阻之和,阻值非常大,因而 工作在深度饱和状态,使Vc∞~0。这时的集电极电流极小,在定量计算时可略而不计。 截止后∞为高电平,而v∈为低电平,从而使导通、截止,输出为高电平Von。时,如果不考虑 的存在,则应有 Vm+ Von =4.1V。显然,在存在 。和 的情况的发射结必然同时导通。而一旦 ,和导通之后,便被钳在了 2.1V,所以在实际上不可能等于 4.1V,只能是2.1V左右。导通使∞降低而升高,导致 T,截止、导通,输出变为低电平 VoL。可见输出和输入之间是反相关系,即Y=A。。集电极输出的电压信号和发射极输出的电压信号变化方向相反,所以把这一级叫做倒相级。输出级的工作特点是在稳定状态下。总是一个导通而另一个截止,这就有效地降低了输出级的静态功耗并提高了驱动负载的能力。通常把这种形式的电路称为推拉式(push一pull)电路或图腾柱(to-tem一 pole)输出电路。可靠地截止,又在 的发射极下面串进了二极管D。 悬输入端钳位二极管,它既可以抑制输人端可能出现的负极性干扰脉冲,又可以防止输人电压为负时,的发射极电流过大,起到保护作用。这个二极管允许通过的最大电流约为20mA。

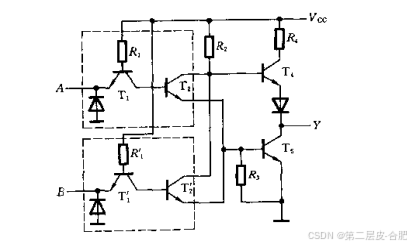

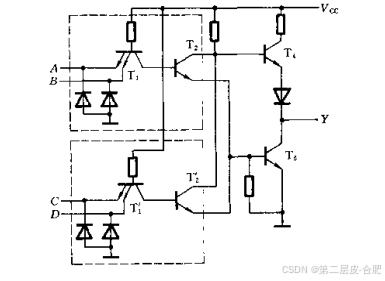

其他类型的TTL门电路

为便于实现各种不同的逻辑函数,在门电路的定型产品中除了反相器以外还有与门、或门、与非门、或非门、与或非门和异或门几种常见的类型。尽管它们逻辑功能各异,但输入端、端出端的电路结构形式与反相器基本相同.因此前面所讲的反相器的输入特性和输出特性对这些门电路同样适用。

TTL与非门

TTL或非门

TTl与或非非门