波峰焊与选择性波峰焊是两种不同的通孔插件焊接技术,理解它们的区别对于正确的PCB布局设计至关重要。

第一部分:波峰焊 vs. 选择性波峰焊的区别

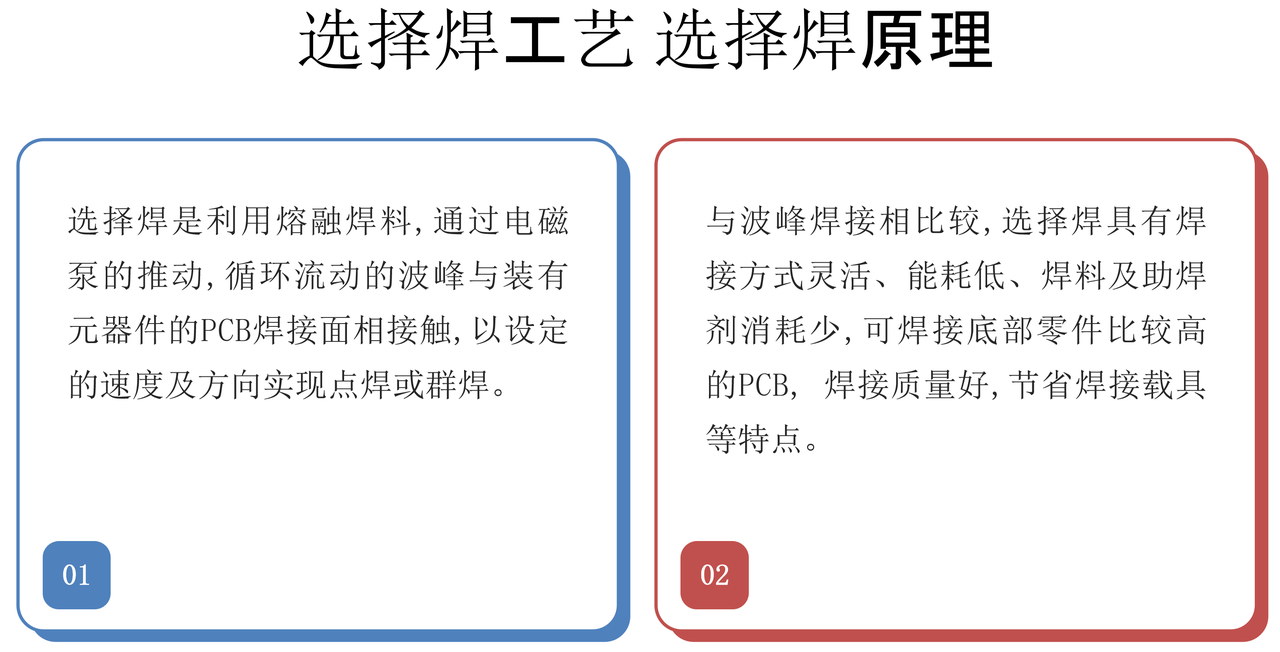

选择焊焊接时,PCB固定不动,焊接头根据程序的设定在X,Y,Z轴方向移动实现PCB焊点的焊接。

|------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 特性 | 传统波峰焊 | 选择性波峰焊 |

| 工作原理 | 整块PCB的焊接面平行地经过一个连续的、流动的锡波。 | 一个微型的锡波喷嘴,按编程路径仅移动到需要焊接的通孔焊盘上方进行局部焊接。 |

| 焊接范围 | 整板焊接。无法区分区域,一次过炉焊接所有露出焊盘。 | 局部点焊。可精确控制焊接哪个点,哪个不焊。 |

| 热影响 | 大面积、长时间加热。整个焊接面及元器件都会经历高温预热和锡波接触。 | 局部、短时间加热。热影响区域非常小,仅限于焊点周围几毫米。 |

| 优点 | - 效率极高,适合大批量、元件类型单一的板卡。 - 成本低(设备与耗材)。 | - 极高的灵活性,可在密集SMT器件旁焊接插件。 - 热应力小,保护了敏感器件和PCB本身。 - 焊料消耗少,无桥连,焊接质量高。 |

| 缺点 | - 热冲击大,会损坏已焊好的SMT器件(特别是另一面的BGA)。 - 容易造成桥连、漏焊,需后续修补。 - 需设计波峰焊托盘(治具)来遮蔽和保护SMT器件,增加成本。 | - 速度慢,每个焊点逐个或小区域焊接。 - 设备昂贵,编程和维护复杂。 - 初始设置时间长。 |

| 典型应用 | 消费电子、电源板、低密度控制板等大批量产品。 | 汽车电子、工控、通信设备、航空航天等高可靠性、高混合度(SMT+THT密集) 的板卡。 |

第二部分:布局贴装器件时的注意事项(针对波峰焊接工艺)

当你的PCB需要采用波峰焊工艺时,SMT器件的布局必须遵循严格的DFM规则,否则会造成焊接灾难。而对于选择性波峰焊,限制则少得多。

通用核心原则:区分"焊接面"与"元件面"

-

焊接面:波峰焊的锡波接触的一面。所有通孔器件的引脚和焊盘都在这一面。

-

元件面:与焊接面相对的一面,主要放置贴片器件。

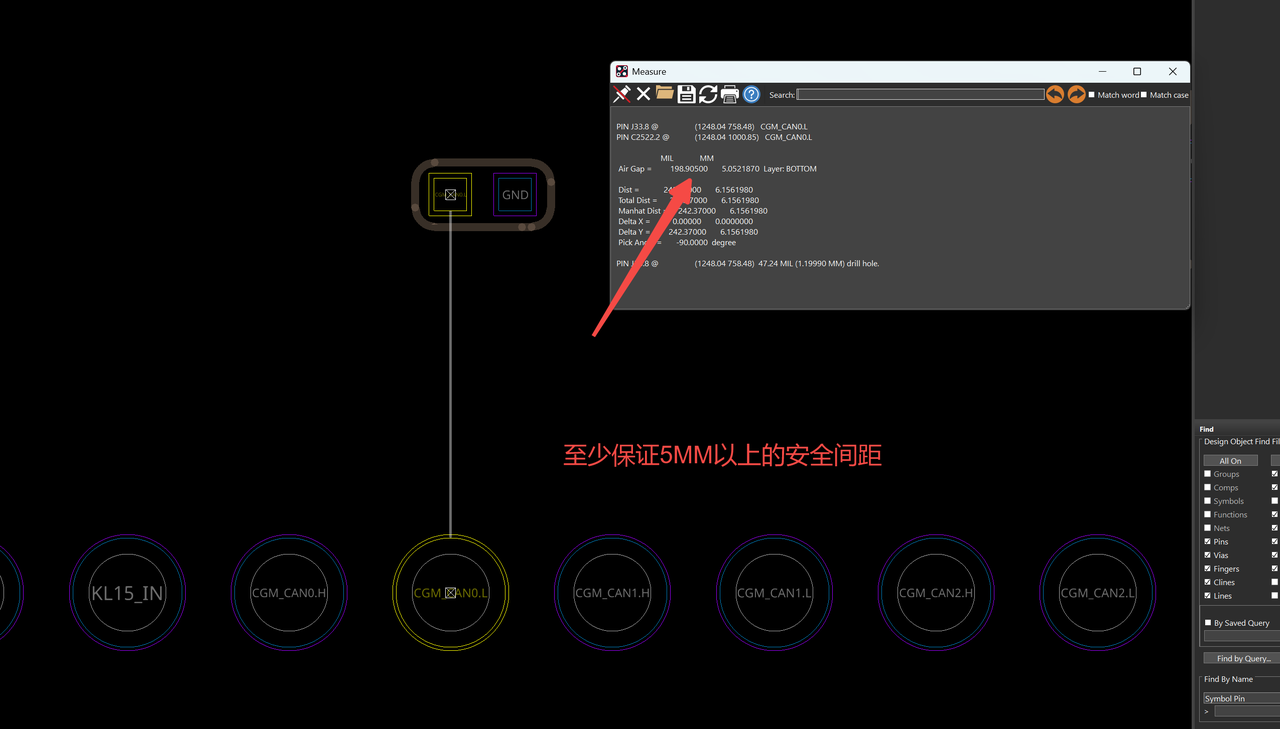

若是换成波峰焊的话,器件离通孔器件的焊盘间距要求至少都是5MM以上了,7-10MM间距要求比较多一些。

布局规则对比表

|----------------|-----------------------------------------------|----------------------|---------------------------------------------|

| 注意事项 | 波峰焊 | 选择性波峰焊 | 原理与原因 |

| 1. 器件类型与方向 | | | |

| - 焊接面能否放SMT器件? | 原则上不允许。必须放的需用波峰焊托盘遮蔽保护。 | 可以,且非常自由。 | 波峰焊的锡波会淹没、冲走或桥连未保护的SMT器件。选择性焊只针对特定点。 |

| - 器件方向 | 器件长边应平行于传送方向。 | 无特殊要求。 | 防止"阴影效应":器件本体阻挡锡波流入其后的焊盘,造成漏焊。 |

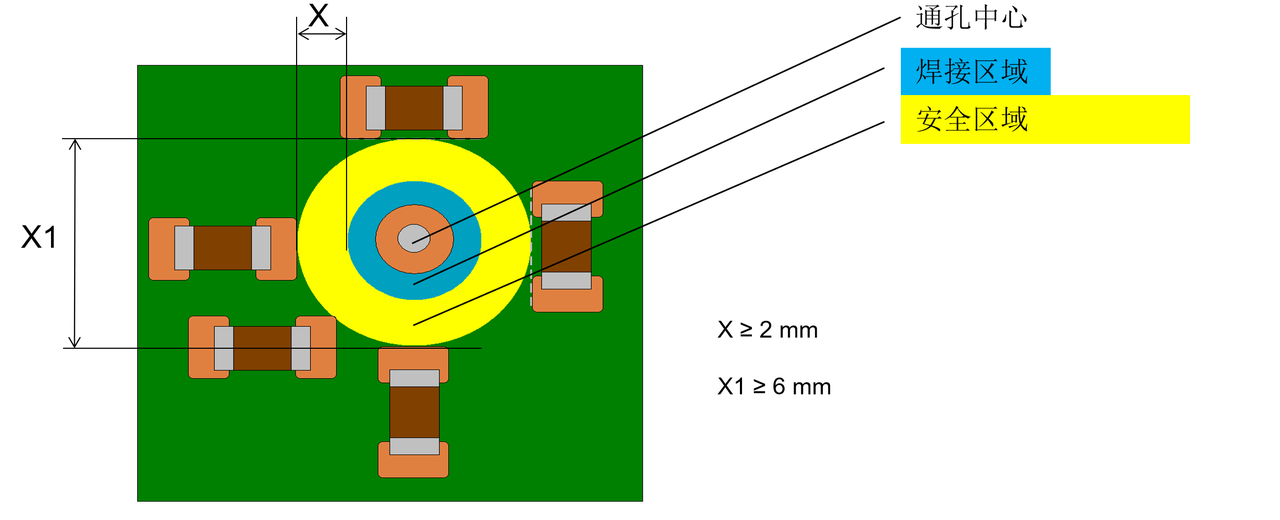

| - 相邻器件间距 | 间距需足够大(通常>2.5mm),防止锡波桥连。 | 无特殊要求,只要满足电气和装配空间即可。 | 液态焊料表面张力容易在密集的器件间形成桥连。 |

| 2. 器件到通孔/板边的距离 | | | |

| - SMT器件距通孔插件 | 建议≥5mm。防止托盘开窗困难,以及热传导影响。 | 可以很近,甚至相邻(如1.5以上mm)。 | 波峰焊需要物理托盘来遮蔽SMT器件,距离太近托盘开窗脆弱或无法制作。选择性焊无此问题。 |

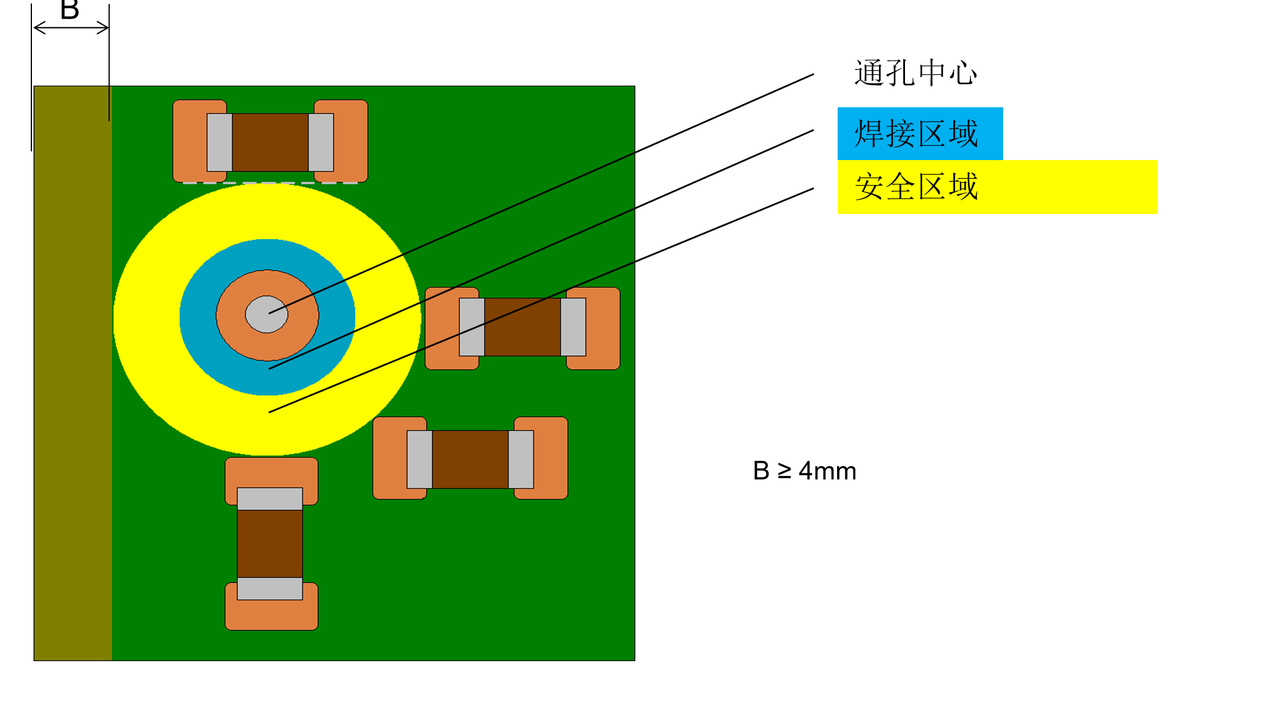

| - 器件距板边 | ≥5mm,为轨道夹持和托盘支撑留出空间。 | ≥4mm即可,主要考虑机械强度。 | 波峰焊设备夹具和托盘需要可靠的支撑边。 |

| 3. 敏感器件的保护 | | | |

| - BGA、QFN、连接器等 | 绝对禁止放在焊接面。尽量避免放在元件面(即背面),因为热风预热会使其二次回流。 | 放在任何一面都相对安全,热影响极小。 | 波峰焊的预热和热辐射足以使BGA焊球重熔,导致失效。选择性焊热量高度集中。 |

| 4. 焊盘与走线设计 | | | |

| - 偷锡焊盘 | 必须添加。在最后一排引脚的后方(下游)设计一个小焊盘,用于引导离开的锡波,防止桥连和挂锡。 | 不需要。 | 帮助切断焊料尾巴,是波峰焊的经典DFM设计。 |

| - 走线与焊盘连接 | 避免从焊盘非下游侧引出大铜皮,否则会形成"盗锡",导致焊盘上锡不足。 | 影响很小,对送热更关注。 | 大铜皮散热快,会抢夺焊盘热量,导致冷焊。 |

| 5. 其他考虑 | | | |

| - 托盘成本与交期 | 必须为每款PCB设计和制作昂贵的玻纤或合成石托盘。 | 通常不需要托盘,或只需要简单的支撑夹具。 | 托盘是波峰焊的必要消耗品和成本项。 |

| - 工艺复杂度 | 高(需设计托盘、优化波峰参数、处理大量不良)。 | 高(需精确编程、维护喷嘴)。 | 两者都复杂,但难点不同。 |

布局决策流程与建议

-

首先确定工艺:

-

如果板子通孔插件多、布局稀疏、产量巨大 → 优先考虑传统波峰焊,并严格遵守其布局规则。

-

如果板子通孔插件少、与SMT高度集成、可靠性要求高、混产频繁 → 优先考虑选择性波峰焊,布局自由度大幅提升。

-

-

采用波峰焊时的"保命"清单:

-

CASE 1: 焊接面只放通孔插件,坚决不放SMT(除非万不得已且用托盘保护好)。

-

CASE 2: 元件面(背面)的SMT器件,特别是BGA,尽量远离大的通孔插件区域,减少热影响。

-

CASE 3: 与工艺工程师一起评审托盘设计方案,在布局阶段就考虑托盘开窗的可行性和可靠性。

-

CASE 4: 方向、间距、偷锡焊盘三要素必须检查。

-

-

采用选择性波峰焊时的优势利用:

-

可以实现 "两面都是SMT面" 的布局,仅在需要的地方"打孔插装",极大提升布局密度和设计灵活性。

-

重点注意:为选择性焊喷嘴留出足够的移动和避让空间,避免被周围高大的器件阻挡。

-

分析总结:

总体来说就是波峰焊要求布局服从工艺,选择性波峰焊让工艺服务于布局。 在成本允许的情况下,选择性波峰焊是现代高密度、高可靠性电子产品的首选,它能从根本上解决SMT与THT混装的布局矛盾。如果必须使用传统波峰焊,则必须在PCB布局之初就将其苛刻的DFM规则作为铁律来执行,把这个安全间距规则提前导入到EDA软件中去,避免后期有所遗漏掉,有的比较规范的公司做的封装前期的时候把这个通孔插件的器件上封装上已经做好了波峰焊的安全间距了,这个做法还是比较好的。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!